## Mechanisms for Distributed Shared Memory

by

## Steven K. Reinhardt

## A dissertation submitted in partial fulfillment of

the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

## UNIVERSITY OF WISCONSIN—MADISON

1996

## Abstract

Distributed shared memory (DSM) systems simplify the task of writing distributedmemory parallel programs by automating data distribution and communication. Unfortunately, DSM systems control memory and communication using fixed policies, even when programmers or compilers could manage these resources more efficiently.

This thesis proposes a new approach that lets users efficiently manage communication and memory on DSM systems. Systems provide primitive DSM mechanisms without binding them to fixed protocols (policies). Standard shared-memory programs use default protocols similar to those found in current DSM machines. Unlike current systems, these protocols are implemented in unprivileged software. Programmers and compilers are free to modify or replace them with optimized custom protocols that manage memory and communication directly and efficiently.

To explore this new approach, this thesis:

- identifies a set of mechanisms for distributed shared memory,

- develops *Tempest*, a portable programming interface for mechanism-based DSM systems,

- describes *Stache*, a protocol that uses Tempest to implement a standard shared-memory model,

- summarizes custom protocols developed for six shared-memory applications,

- designs and simulates three systems—*Typhoon, Typhoon-1*, and *Typhoon-0*—that support Tempest, and

- describes a working hardware prototype of Typhoon-0, the simplest of those designs.

Tempest combines fine-grain coherence support, an active message model, and virtualmemory–based page allocation to provide portability across a range of platforms.

Typhoon, Typhoon-1, and Typhoon-0 support Tempest using different levels of custom hardware integration. Typhoon achieves high performance by integrating key components on one device. Typhoon-1 and Typhoon-0 use off-the-shelf parts for some of these components, trading some performance for simpler designs.

Typhoon demonstrates that mechanism-based DSM systems can compete with hardwired-protocol systems on unmodified shared-memory applications (within 25% across six benchmarks). Despite Typhoon's low overheads, custom protocols improve performance significantly for some applications—by 384% for one benchmark. Results for Typhoon-1 and Typhoon-0 on unmodified applications are varied, but custom protocols bring them within 13% and 47% of Typhoon, respectively.

A working Typhoon-0 prototype demonstrates the feasibility of these designs. Measurements of the prototype's performance substantiate simulator projections.

## Acknowledgments

I cannot possibly thank all who have contributed to making my time in Madison so enjoyable and successful. Nonetheless, I will try.

David Wood, my advisor, provided guidance, encouragement, and raw material in just the right amounts. Mark Hill and Jim Larus, the other members of the Wisconsin Wind Tunnel triumvirate, provided ideas, opinions, support, and invaluable advice on both the technical and non-technical aspects of research. It has been a privilege to start on the ground floor and watch the WWT group grow in size and stature under their leadership.

Guri Sohi did his best to keep me honest in his role as the loyal opposition. Thanks to David, Mark, Jim, Guri, and Jim Smith for serving on my thesis committee. Jim Smith and Guri provided comments from an external perspective that greatly improved the presentation of this thesis. Thanks also to Jim Goodman for his interest in my work.

Thanks to all the other students in the Wisconsin Wind Tunnel group and in the larger UW computer architecture community for their support and camaraderie. In particular, Alvy Lebeck provided friendship, counsel and occasional commiseration over countless lunches and coffee breaks. Babak Falsafi had the dubious pleasure of hacking on a lot of my code; I thank him for not complaining any more than he did. Rob Pfile designed Vortex, the key component of the Typhoon-0 prototype. That system is a reality due to his dedication. Alvy, Babak, Shubu Mukherjee, and Yannis Schoinas helped to develop and maintain a lot of critical software including simulators, Tempest support components, and the custom protocols for the benchmarks used in this thesis. I also thank AT&T Bell Labs and the Wisconsin Alumni Research Foundation for their generous fellowship awards.

Diana, my wife, set aside her personal goals to follow me to Wisconsin, and ended up raising three children while I completed my degree. I cannot thank her enough for her love, support, patience, and friendship. Thanks also to our children—Ziggy, Anastasia, and Sophia—for giving me extra motivation to come home and (almost) always being glad to see me when I arrived. I also thank our parents for their generosity and support.

Neither Diana nor I could have survived without lots of help and prayers from our church family, especially Danean & Dan Kirchner and Kelly & Ken Jensen.

Most of all, I must give thanks and praise to Jesus Christ. Through faith in him, I am reconciled with the one true God of the universe—a fact that makes earthly trials and achievements pale in comparison.

> Oh, the depth of the riches of the wisdom and knowledge of God! How unsearchable his judgments, and his paths beyond tracing out! "Who has known the mind of the Lord? Or who has been his counselor?" "Who has ever given to God, that God should repay him?" For from him and through him and to him are all things. To him be the glory forever! Amen. Romans 11:33–36 (NIV)

## Contents

| Abstrac   | t     | i                                            |

|-----------|-------|----------------------------------------------|

| Acknow    | ledg  | mentsiii                                     |

| List of F | ligur | esviii                                       |

| List of T | able  | SX                                           |

| Chapter   | · 1.  | A New Approach to Distributed Shared Memory1 |

| 1.1       | Mec   | chanisms for distributed shared memory5      |

| 1.2       | The   | Tempest interface                            |

| 1.3       | Har   | dware support for Tempest                    |

| 1.4       | The   | sis organization                             |

| Chapter   | · 2.  | Mechanisms for Distributed Shared Memory12   |

| 2.1       | Fun   | damental mechanisms                          |

| 2.2       | The   | Tempest interface                            |

| 2         | .2.1  | Messaging                                    |

| 2         | .2.2  | Local storage management                     |

| 2         | .2.3  | Access control                               |

| 2         | .2.4  | Mechanism interactions                       |

| 2.3       | Trai  | nsparent shared memory using Tempest         |

| 2.4       | Opt   | imizing applications using Tempest           |

| 2         | .4.1  | EM3D                                         |

| 2         | .4.2  | Appbt                                        |

| 2         | .4.3  | Barnes                                       |

|         |             | vi                                            |

|---------|-------------|-----------------------------------------------|

| 2       | 2.4.4       | DSMC                                          |

| 2       | 2.4.5       | Moldyn                                        |

| 2       | 2.4.6       | Unstructured                                  |

| 2.5     | Rela        | ted work                                      |

| 2.6     | Sum         | mary                                          |

| Chapter | r <b>3.</b> | Hardware Support for Tempest43                |

| 3.1     | Com         | nmon features                                 |

| 3       | 3.1.1       | Messaging                                     |

| 3       | 3.1.2       | Local storage management                      |

| 3       | 3.1.3       | Fine-grain access control                     |

| 3.2     | Typl        | hoon: integrated hardware support for Tempest |

| 3       | 3.2.1       | Protocol processor                            |

| 3       | 3.2.2       | Access control (RTLB)                         |

| 3       | 3.2.3       | Block transfer unit and block buffer          |

| 3       | 3.2.4       | Handler dispatch                              |

| 3       | 3.2.5       | Primary CPU access                            |

| 3.3     | Deco        | pupled hardware support for Tempest           |

| 3       | 3.3.1       | Cacheable control registers                   |

| 3       | 3.3.2       | Handler dispatch                              |

| 3       | 3.3.3       | Access control                                |

| 3       | 3.3.4       | Typhoon-1                                     |

| 3       | 3.3.5       | Typhoon-0                                     |

| 3.4     | Perf        | ormance                                       |

| 3       | 3.4.1       | Microbenchmark                                |

| 3       | 3.4.2       | Macrobenchmarks                               |

| 3       | 3.4.3       | Impact of network latency                     |

| 3       | 3.4.4       | Impact of protocol-processing performance     |

| 3.5     | Rela        | ted work                                      |

|              |                                          | vii |

|--------------|------------------------------------------|-----|

| 3.6 Summ     | nary                                     |     |

| Chapter 4. T | he Typhoon-0 Prototype                   |     |

| 4.1 Hardw    | vare                                     |     |

| 4.2 Softwa   | are                                      |     |

| 4.2.1        | Vortex configuration                     |     |

| 4.2.2 H      | Process setup                            |     |

| 4.2.3        | Other Solaris modifications              |     |

| 4.2.4        | System issues                            |     |

| 4.2.5 N      | Messaging                                |     |

| 4.3 Perfor   | mance                                    |     |

| 4.3.1 N      | Microbenchmarks                          |     |

| 4.3.2 N      | Macrobenchmarks                          | 102 |

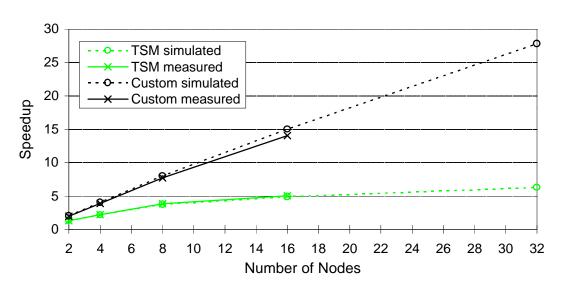

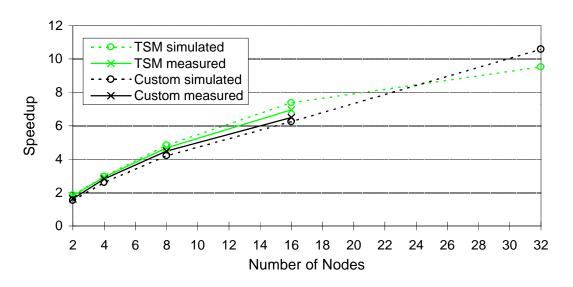

| 4.4 Compa    | arison of measured and simulated results | 103 |

| 4.5 Summ     | nary                                     | 106 |

| Chapter 5. C | onclusion                                |     |

| 5.1 Summ     | nary                                     | 108 |

| 5.2 Future   | e directions                             | 110 |

| References   |                                          |     |

| Appendix A.  | Tempest Interface Specification          |     |

| Appendix B.  | Access Control Via Bus Snooping          | 141 |

# List of Figures

| Figure 1-1.  | Distributed-memory system organization                                  |

|--------------|-------------------------------------------------------------------------|

| Figure 2-1.  | DSM memory access flowchart                                             |

| Figure 2-2.  | Stache example, step 1                                                  |

| Figure 2-3.  | Stache example, step 2                                                  |

| Figure 2-4.  | Stache example, step 3                                                  |

| Figure 2-5.  | Example EM3D bipartite graph                                            |

| Figure 2-6.  | EM3D program fragment                                                   |

| Figure 3-1.  | Common system organization45                                            |

| Figure 3-2.  | Logical components of Tempest support                                   |

| Figure 3-3.  | Component integration diagram                                           |

| Figure 3-4.  | Shadow tag space example                                                |

| Figure 3-5.  | Typhoon node, including a block diagram of the network interface/       |

|              | access control/protocol processor device                                |

| Figure 3-6.  | Typhoon RTLB diagram                                                    |

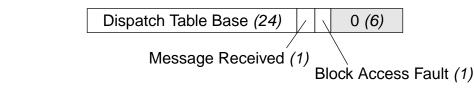

| Figure 3-7.  | Dispatch program counter format                                         |

| Figure 3-8.  | Dispatch register layout for block access faults                        |

| Figure 3-9.  | Dispatch code for block access faults                                   |

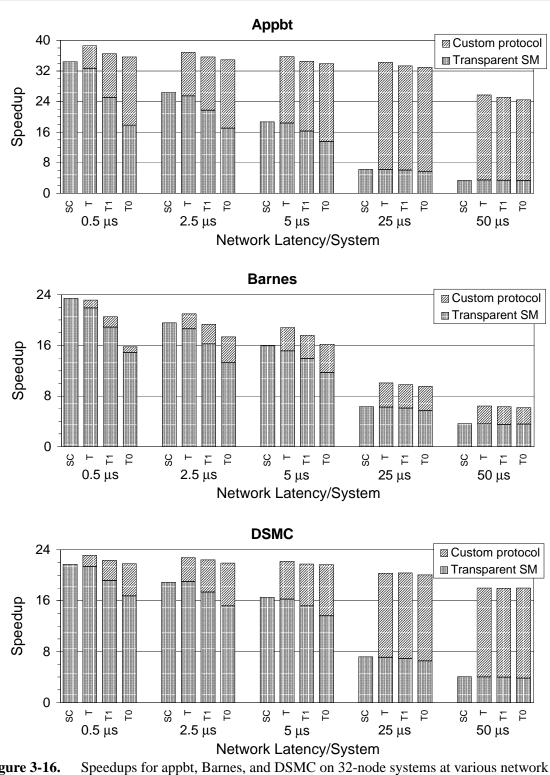

| Figure 3-10. | Typhoon-1 node,                                                         |

| Figure 3-11. | Typhoon-0 node,                                                         |

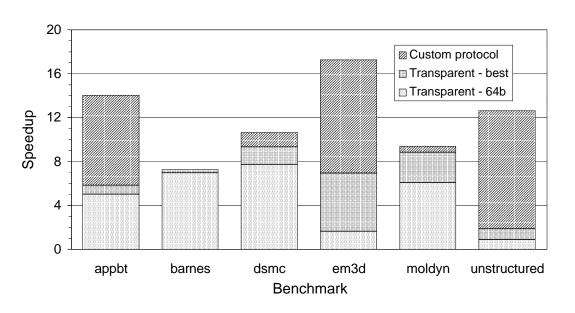

| Figure 3-12. | Application speedups for transparent shared memory on 32-node           |

|              | systems                                                                 |

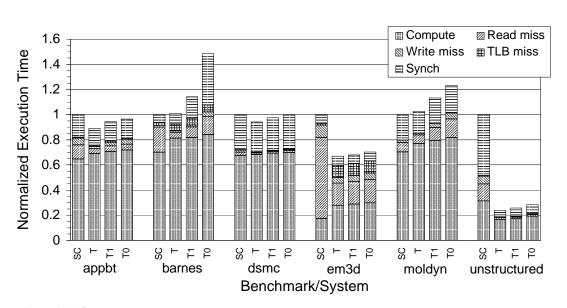

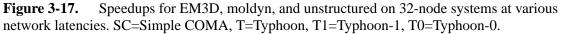

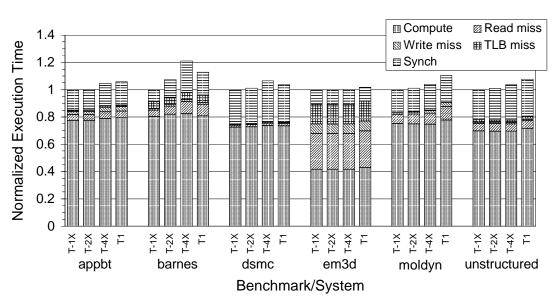

| Figure 3-13. | Execution time breakdown for transparent shared memory                  |

| Figure 3-14. | Application speedups on 32-node systems, including application-specific |

|              | protocols                                                               |

| Figure 3-15. | Execution time breakdown for the application-specific protocols, normalized |

|--------------|-----------------------------------------------------------------------------|

|              | to transparent shared memory on Simple COMA                                 |

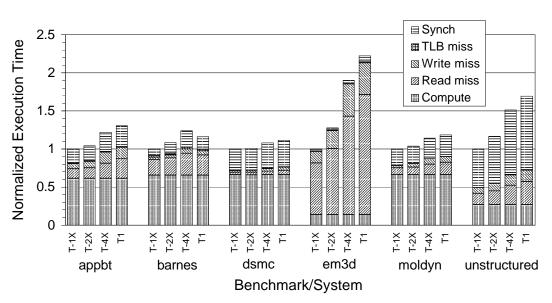

| Figure 3-16. | Speedups for appbt, Barnes, and DSMC on 32-node systems at various          |

|              | network latencies                                                           |

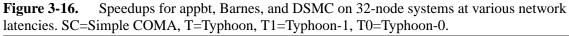

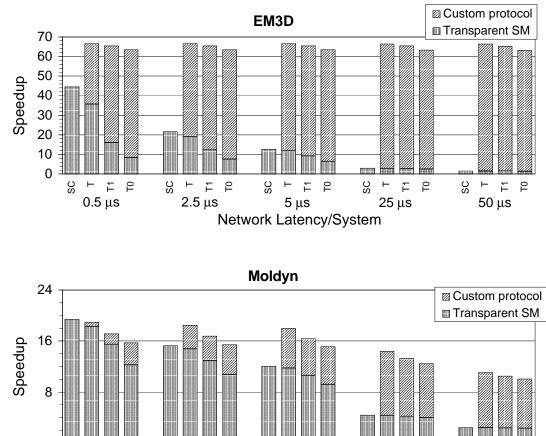

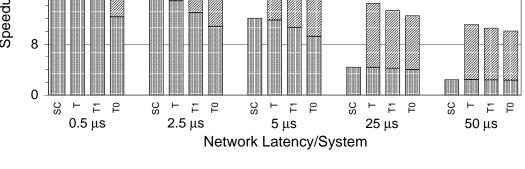

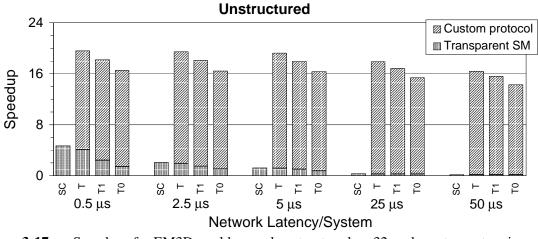

| Figure 3-17. | Speedups for EM3D, moldyn, and unstructured on 32-node systems at           |

|              | various network latencies                                                   |

| Figure 3-18. | Execution time for transparent shared memory on Typhoon, varying the        |

|              | protocol processor speed                                                    |

| Figure 3-19. | Execution time for the application-specific protocols on Typhoon, varying   |

|              | the protocol processor speed                                                |

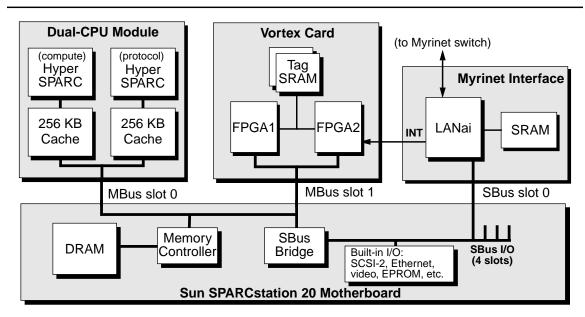

| Figure 4-1.  | Block diagram of a Typhoon-0/COW node                                       |

| Figure 4-2.  | Application speedups on 16 nodes of the prototype system                    |

| Figure 4-3.  | Simulated and measured speedups for Appbt105                                |

| Figure 4-4.  | Simulated and measured speedups for Barnes                                  |

## List of Tables

| Table 3.1: | Remote miss latency breakdown for simulated systems             |

|------------|-----------------------------------------------------------------|

| Table 3.2: | Benchmark applications and data sets                            |

| Table 4.1: | Remote miss latency breakdown for the Typhoon-0 prototype101    |

| Table A.1: | Access tag semantics                                            |

| Table A.2: | Block tag change enumeration values (type TPPI_BlkTagChange)133 |

| Table B.1: | Bus monitor snooping behavior                                   |

### Chapter 1

## A New Approach to Distributed Shared Memory

Modern microprocessors provide a tremendous amount of computing power for a relatively small price. Currently, the fastest microprocessors execute up to four instructions every two nanoseconds—a peak rate of two billion instructions per second—yet sell for \$3,000 or less [Mic96] and can be had in complete systems for under \$10,000 [Eno96]. It is difficult and costly to reach higher performance levels by building faster processors: the cheapest non-microprocessor–based system that is faster by any measure is the half-million–dollar Cray J90 [McC96, Cra96]. With few exceptions, the most cost-effective approach to higher performance is to gang multiple microprocessors together.

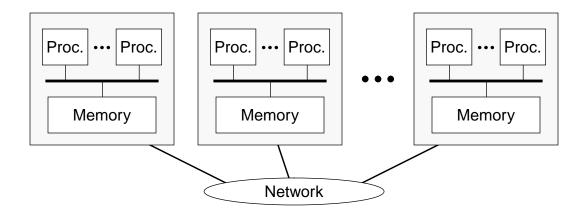

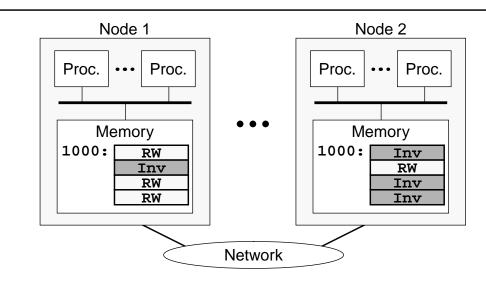

Nearly all current multi-microprocessor systems organize their processors and memory using one of two methods. The simplest approach uses a bus—a common set of wires—to join the processors and memory [Bel85]. However, competition for use of the shared bus limits these *bus-based* systems to at most a few tens of processors. Larger systems avoid the bus bottleneck by grouping processors and memory into nodes—each one essentially a bus-based uni- or multiprocessor system itself—which communicate via a point-to-point messaging network (see Figure 1-1). The size of these *distributed-memory* systems is lim-

Figure 1-1. Distributed-memory system organization.

ited primarily by cost: Intel is scheduled to deliver a machine with 9,000 processors and 262 gigabytes of memory by the end of this year (1996)—at a cost to the U.S. government of \$46 million [Int95].

Although distributed memory allows the construction of larger machines, it introduces two new tasks: distributing data among the nodes and communicating across the network when processors need data from other nodes. To achieve high performance—the primary motivation for building a large machine—these tasks must be performed well. Efficient data distribution and communication—storing data on the node or nodes where it is used and overlapping network delays with useful work—improves performance by reducing or eliminating the time processors wait for data to cross the network. Two prevalent types of distributed-memory machines—*message passing* and *distributed shared memory*—handle these tasks in markedly different ways.

Message-passing systems leave data distribution and communication entirely to software. Programs specify explicitly on which node each datum is located and when each message is sent. If programmers and compilers can predict precisely where and when each datum is used, they can exploit this control to use memory and network resources efficiently. However, less predictable programs require potentially costly run-time software to locate data and process messages dynamically. In addition, a message-passing program's data distribution and communication patterns affect its structure and correctness substantially. Programmers who use message passing directly must deal with these issues up front, and decisions made early in development often are not easily reversible.

In contrast, distributed shared memory (DSM) systems distribute and communicate data automatically. These systems provide the abstraction of one global, uniformly fast memory. Programs access data by referencing locations in this global memory space. Systems transparently fetch data, regardless of its physical location, to satisfy these references. At the same time, these systems replicate and migrate data dynamically across the nodes to keep values near the processors that reference them. Because the shared-memory abstraction matches the model that arises naturally on bus-based multiprocessors, DSM systems take advantage of programs written for—and programmers trained on—the much more common bus-based machines. Programmers can develop correct, working programs without considering data distribution or communication.

Unfortunately, DSM machines hide the underlying distributed-memory organization too well at times. Although programs that are naive about data distribution and communication will function correctly on a DSM system, they may not perform well. Programmers must reason about (or compilers must deduce) a program's memory and communication behavior to improve its performance. However, once a program's behavior is understood, DSM systems provide no standard, direct techniques for implementing efficient data distributions or communication protocols. Instead, programmers and compilers must attempt to effect these optimizations indirectly by modifying the program's reference pattern.

This thesis proposes a new approach that lets users efficiently manage communication and memory on DSM systems. This approach is based on separating DSM *mechanisms* the low-level operations that make DSM feasible—from the *policies* that govern their use [Bri70, LCC<sup>+</sup>75, Wul81]. Systems implement primitive memory and communication mechanisms sufficient to support distributed shared memory—mechanisms present in some form in most DSM machines. Unlike existing systems, which bury these mechanisms underneath fixed policies, these new mechanism-based systems let ordinary software access these mechanisms directly. For standard shared-memory programs, software libraries provide universal policies, similar to those implemented in current DSM systems. However, because these policies are ordinary software—just like any other program component—programmers and compilers may modify or replace them, exploiting programspecific knowledge to optimize data distribution and communication. This mechanismbased approach maintains DSM's convenient model and dynamic data management while enabling the potential efficiencies of message passing's explicit resource control.

To make this proposal concrete, I describe a programming interface for mechanismbased DSM systems called *Tempest*. Tempest strikes a balance between portability and performance by combining virtual-memory page mapping—as used by page-based software DSM systems [LH89]—with the fine-grain coherence found in hardware DSM machines. This balance makes Tempest a suitable interface for all-software implementations on generic message-passing machines [SFL<sup>+</sup>94, SFH<sup>+</sup>96] as well as higher-performance hardware-accelerated systems [RLW94, RPW96]. Applications and programming tools written to the Tempest interface run unmodified across this wide range of systems. I describe *Stache*, a software library that implements application-transparent shared memory—similar to that provided by a typical DSM system—using Tempest. I also summarize six shared-memory applications which programmers have optimized by accessing Tempest's mechanisms directly [FLR<sup>+</sup>94, MSH<sup>+</sup>95].

An interface is a contract between the users and the implementors of a system, so it must carefully consider both perspectives. On the implementation side, this thesis examines Tempest systems that can be constructed by adding custom hardware to networks of offthe-shelf workstations. I describe three designs that explore the relationship between the level of custom hardware integration and system performance. The systems proposed here demonstrate that Tempest is amenable to a range of custom hardware acceleration techniques. Simulations show that the design with the most highly integrated Tempest support—called *Typhoon*—performs at a level comparable to a hardware-controlled DSM system. I also describe a prototype implementation of the simplest custom-hardware design—known as *Typhoon-0*—that demonstrates the feasibility of this approach and provides a real-world system for benchmarking.

The following section discusses the mechanism-based approach to distributed shared memory further. The remaining sections describe the two main contributions of this thesis—the Tempest interface and the design and analysis of hardware support for Tempest in more detail.

#### **1.1 Mechanisms for distributed shared memory**

To understand the role of mechanisms in distributed shared memory, consider the operation of typical DSM systems. These systems approximate the behavior of a uniform shared memory by caching data stored on other nodes (*remote* data). When a processor in such a system accesses remote memory, the system copies the requested data, plus some neighboring values—a data *block*—to a portion of local memory called a *cache*. The system then satisfies future accesses to that remote data block using the local cache copy, avoiding further network traversals. Because most programs exhibit locality—that is, once a processor accesses a memory location, it is likely to access that location or others near it shortly—the local cache handles most memory accesses, regardless of the data's original location. As memory values change, *coherence protocols* ensure that processors do not access out-of-date cache copies. These protocols track the nodes that copy each data block and send messages to invalidate or update those copies when a block is modified.

Because programmers communicate with the system only through memory accesses (loads and stores), they must relinquish message passing's direct control over memory and communication to gain shared memory's ease of use. This lack of control forces them to forgo potential optimizations [KJA<sup>+</sup>93, Lar94]. For example, a programmer may know (or a compiler may deduce) that a value written on node *A* will be read next on node *B*. In this case, sending the value directly from *A* to *B* is almost certainly more efficient than relying

on a DSM system's coherence protocol. Even without exact information, a programmer or compiler may be able to supply useful hints. For example, if a processor is not likely to access a memory region again, the system can avoid coherence overhead by not caching the data—while still behaving correctly if the hint is wrong. Finally, some operations, such as synchronization, are expressed more naturally and efficiently in terms of messages.

This thesis proposes that systems give users direct control over memory and communication by providing access to the same primitive mechanisms employed by the coherence protocol. Systems that provide primitive mechanisms can avoid the needless run-time generality of a one-size-fits-all solution [Wul81]. For DSM systems, this one-size-fits-all solution is the coherence protocol. By providing access to a complete set of mechanisms, programmers and compilers are free to modify or replace protocols arbitrarily. Libraries provide standard, universal protocols, such as those found in current DSM systems.

Mechanisms exist at numerous levels; for example, fetching remote data is a mechanism that relies on lower-level mechanisms, including sending a request message and receiving a reply message. To maximize generality and flexibility, this thesis seeks to identify the lowest-level mechanisms that make efficient distributed shared memory feasible. I identify three mechanisms that underlie nearly all DSM systems: *messaging, local storage management*, and *memory access control*. Explicit messaging provides direct control over network communication. Local storage management lets users control each node's memory contents by associating global addresses with local memory locations. Memory access control detects accesses that require coherence action by marking locations invalid, read-only, or writable.

Although these mechanisms are very general, this thesis focuses on their use in optimizing shared-memory application performance. Specifically, programmers tune performance-critical data structures by replacing the standard coherence protocol with application-specific *custom protocols*. These programmer-developed protocols rely on knowledge of the application's communication patterns to improve performance, typically by sending data directly to its consumer. Performance improvements of an order of magnitude have been observed from custom protocols [FLR<sup>+</sup>94]. Although this thesis reports on manual optimizations only, automatic optimizations based on static program analysis [Lar94] or programmer annotations [RAK89, CBZ91, HLRW93] are a promising approach to achieving similar efficiency with reduced programmer effort. Other researchers are investigating tools to aid custom protocol development [CRL96] as well as other applications of these mechanisms—for example, language-specific shared-memory support [LRV94].

In contrast with the mechanism-based approach proposed here, other DSM system designers have dealt with this issue through a combination of two techniques: extending the shared-memory interface and implementing low-overhead, low-latency DSM hard-ware. Mechanism-based DSM is less restrictive than specific interface extensions— enabling a large variety of higher-level programming interfaces—and provides an alternative to building aggressive DSM hardware.

Many systems extend the shared-memory interface—adding operations beyond simple loads and stores—to provide a channel for software to communicate additional information. These operations include uncached accesses, prefetch instructions [CKP91, MG91], writes that update outstanding data copies [RSW<sup>+</sup>93, LLG<sup>+</sup>92], atomic read-modify-write operations [GGK<sup>+</sup>83], and explicit synchronization operations [GVW89]. Weak consistency models [AH90, GLL<sup>+</sup>90] modify the semantics of ordinary loads and stores to allow more reordering—and hence more overlap—among memory accesses. These models require additional operations that force a partial order between accesses to achieve meaningful memory semantics. At a higher level, the Munin software DSM system [CBZ91] lets programmers annotate data structures with expected reference patterns. The system uses these annotations to select from a set of coherence protocols.

In theory, a DSM system that provides a complete set of universal mechanisms can support any or all of these extensions. Ordinary software composes the available mechanisms to support the desired operation(s). Simple extensions such as prefetch may be implemented as a library or inline function; more complex interfaces may involve compiler support as well. In practice, the specific mechanisms provided by a DSM system, and their run-time cost, determine the feasibility and efficiency of a particular operation on that machine.

A second approach to dealing with shared-memory inefficiencies—complementary to extending the interface—is to minimize the impact of these inefficiencies by building aggressive hardware. If communication overhead is low, many applications can achieve good performance within a standard shared-memory model. Simple interface extensions such as prefetching enable good performance for more communication-intensive programs. Systems such as MIT's Alewife [ABC<sup>+</sup>95] and Stanford's DASH [LLG<sup>+</sup>92] and FLASH [KOH<sup>+</sup>94] employ significant amounts of custom hardware to reduce coherence protocol overheads. Although this hardware may increase the number of bus-based multiprocessor applications that perform well without modification, the expense of designing and manufacturing these systems may limit their affordability.

Due to the overhead of sequencing mechanisms in software, mechanism-based systems have a performance disadvantage relative to these hardware-protocol DSM systems on demanding, unmodified shared-memory applications. However, simulations of the Typhoon design (see Section 1.3) indicate that high-end mechanism-based systems can compete with hardware DSM systems on moderately demanding standard shared-memory applications—and have the potential to outperform them significantly when custom protocols are used to optimize communication-intensive applications. The mechanism-based approach also enables effective shared-memory performance on less expensive hardware platforms, as demonstrated by software-only implementations described elsewhere [SFL<sup>+</sup>94, SFH<sup>+</sup>96] and the less integrated hardware designs described in Section 1.3.

#### **1.2 The Tempest interface**

Tempest provides a concrete, portable interface to the three DSM mechanisms identified in the previous section: messaging, local storage management, and memory access control. Tempest's messaging borrows from von Eicken's Active Messages [vECGS92]. Standard virtual address translation mechanisms are used for local storage management, as in software DSM systems [LH89]. The most innovative aspect of Tempest is its specification of *fine-grain* access control, a feature that enables fine-grain coherence and provides scalability to high-performance systems.

Tempest allows a range of implementations so that optimized applications and optimizing compilers need not be re-implemented for every platform. Platform-specific mechanisms are less likely to inspire developers to invest the effort to exploit them, since their effort will be wasted if they move to a different platform. Tempest implementations also span a wide cost/performance range. Low-cost implementations are key to making an interface widely available, which in turn generates a supply of trained programmers, a body of applications, and a market for development tools such as compilers. At the same time, higher-cost, higher-performance implementations must also exist both to support the most demanding applications and to reassure low-end users that their software investment is not wasted if their computational needs increase.

#### **1.3 Hardware support for Tempest**

The second focus of this thesis is the design and evaluation of hardware support for Tempest. Existing software-only Tempest implementations [SFL<sup>+</sup>94, SFH<sup>+</sup>96]—not covered in this thesis—demonstrate the potential of Tempest for low-end systems. The goals of studying hardware support are:

to demonstrate that Tempest scales up incrementally, through a range of higher-cost, higher-performance solutions, to the point where it is competitive with high-end, dedicated distributed shared memory systems;

- to identify techniques that can be used to accelerate Tempest at various cost/performance points; and

- to quantify the performance of these alternatives for shared-memory applications, with and without Tempest optimizations.

I describe three distributed-memory Tempest designs—*Typhoon*, *Typhoon-1*, and *Typhoon-0*—and compare their performance using simulation. I also describe a prototype hardware implementation of the Typhoon-0 system that demonstrates the feasibility of the hardware fine-grain access control approach used in all three systems.

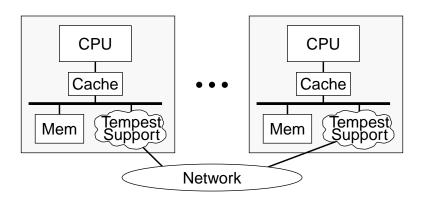

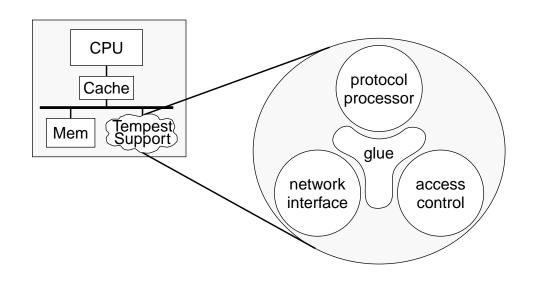

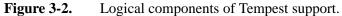

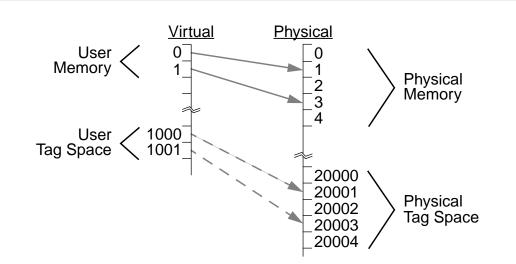

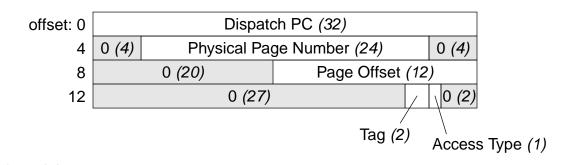

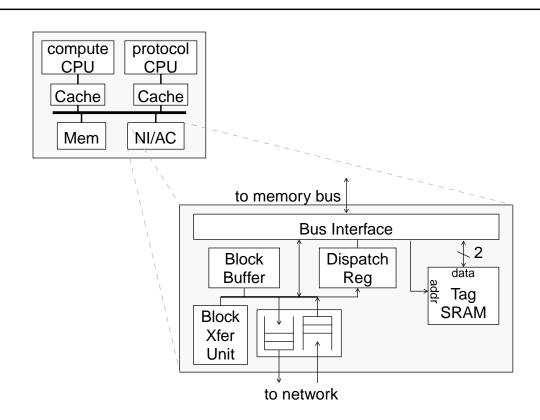

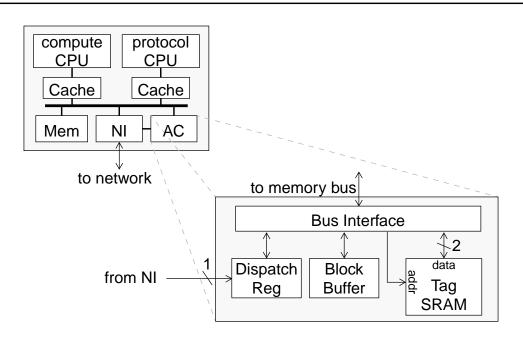

All three designs use cost-effective off-the-shelf workstations for the processor-memory nodes. Each design adds three logical components to every node: a snooping access control device, a network interface, and a protocol processor. The systems differ in the level of custom hardware integration used to implement these components.

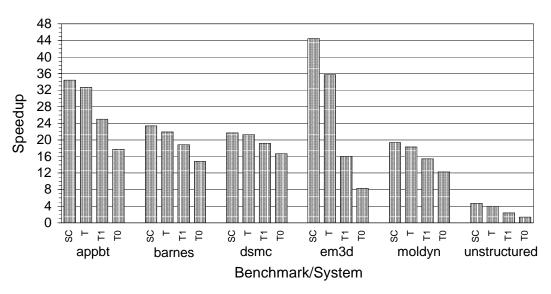

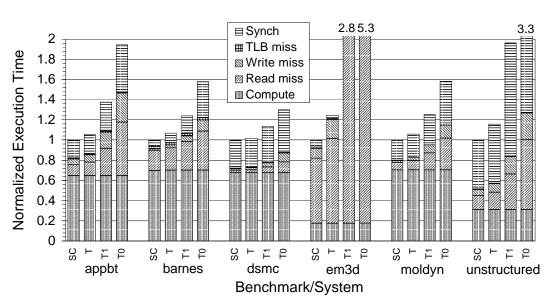

- Typhoon integrates all three components on a single device. This integration lets protocol software efficiently interact with the access control and messaging mechanisms, resulting in high performance—within 25% of a comparable hardwired-protocol system on a set of six unmodified shared-memory benchmarks.

- Typhoon-1 integrates the network interface with access control, but leaves protocol processing to an off-the-shelf processor. Relative to Typhoon, this lower level of integration reduces design complexity, and (potentially) manufacturing cost, at the expense of some performance—11% to 222% on the unmodified benchmarks.

- Typhoon-0 uses a custom access control device with an off-the-shelf protocol processor and an off-the-shelf network interface. Typhoon-0 has the least complexity and lowest performance of the three systems. On the unmodified benchmarks, Typhoon-0 ranges from 28% to 427% slower than Typhoon.

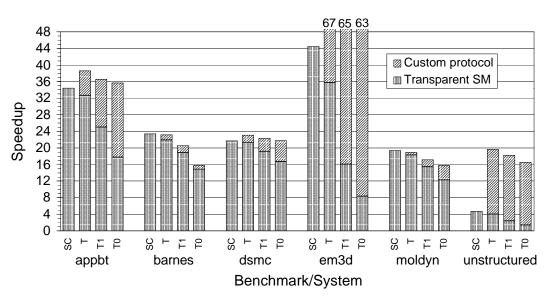

The simulation results also show the effectiveness of Tempest-based custom protocols. Even on Typhoon, with its low-overhead support for standard shared memory, custom protocols sped up one of the benchmarks by 384% and another by 86%. With the custom protocols, Typhoon's performance ranges from 2% worse to four times better than the hardwired-protocol system.

Custom protocols provide even greater benefits on systems with higher overheads. Although Typhoon-1 and Typhoon-0 can be significantly slower than Typhoon for standard shared memory—a factor of two and four, respectively, on the most demanding benchmark—custom protocols reduce the differences to 13% and 47%. Custom protocols also provide more robust application performance in the face of other increased overheads, such as larger network latencies and, for Typhoon, slower embedded processors.

A prototype hardware implementation of Typhoon-0 demonstrates the feasibility of these designs and provides a real-world system for benchmarking. Despite a high-overhead commercial messaging network, five of the six benchmarks achieve better than 58% efficiency on sixteen nodes of the prototype. Application-specific protocols are critical to achieving this efficiency in three of the five cases. The prototype's measured performance agrees substantially with simulator projections.

#### **1.4 Thesis organization**

Chapter 2 motivates the fundamental shared-memory mechanisms, then describes the Tempest interface and its use for both application-transparent and custom shared-memory protocols. Chapter 3 discusses hardware support for Tempest, with a detailed descriptions and a simulation-based performance comparison of Typhoon, Typhoon-1, and Typhoon-0. Chapter 4 focuses on the Typhoon-0 hardware prototype, including measured performance results. Chapter 5 concludes with a summary and future directions for this work.

## **Chapter 2**

### **Mechanisms for Distributed Shared Memory**

This thesis proposes a new, flexible approach to distributed shared memory. Systems provide primitive shared-memory mechanisms without prescribing specific policies (e.g., cache coherence protocols). Programmers and compilers can combine these mechanisms arbitrarily to optimize existing protocols and to implement new ones.

This chapter begins by examining the abstract mechanisms required for distributed shared memory (DSM). Three mechanisms—messaging, local storage management, and access control—underlie nearly all DSM systems. Section 2.2 describes Tempest, a concrete, portable interface to these mechanisms. Tempest uses a variant of Active Messages [vECGS92] for messaging. Virtual address translation provides local storage management. Tempest's most innovative feature is *fine-grain* access control. The next two sections show how Tempest can be used, first to provide application-transparent shared memory (Section 2.3), then to optimize the performance of shared-memory applications using custom protocols (Section 2.4). The chapter closes with a discussion of related work (Section 2.5) and a summary (Section 2.6).

#### 2.1 Fundamental mechanisms

This section identifies three abstract mechanisms—messaging, local storage management, and access control—required to support shared-memory programming models on distributed-memory machines. Mechanisms are the separable components of a process or system. Policies are the rules that govern how mechanisms are used to achieve a desired result. The division of a process into mechanisms can be done at several levels; a mechanism at one level may be built from a lower-level set of mechanisms and policies. To maximize generality and flexibility, this work seeks to identify the lowest-level mechanisms that make efficient distributed shared memory feasible.

These mechanisms assume a typical distributed-memory parallel machine, comprising a set of nodes connected by a messaging network (see Figure 1-1 on page 2). Each node contains one or more processors that share a memory module and an interface to the network. Hardware maintains coherence among processor caches within a node. Memory accesses are performed only on the node where they are issued—that is, remote data references are performed on a copy of the data in local main memory or a hardware cache.<sup>1</sup>

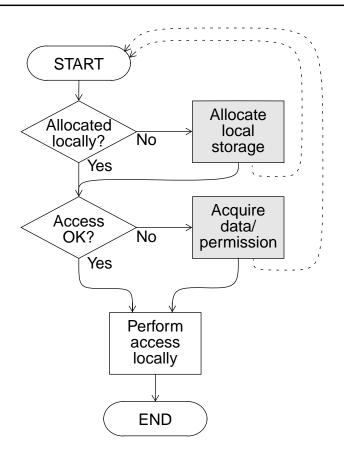

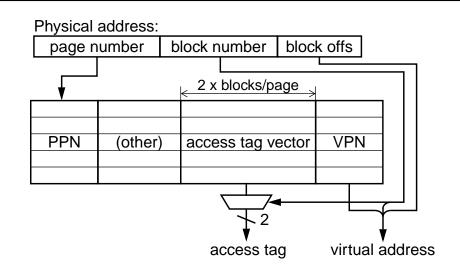

Every distributed-memory machine incorporates a **messaging** mechanism—that is, a way for nodes can communicate through the network—even if messaging is not directly available to users. To understand the remaining DSM mechanisms, consider the process of performing a shared-memory access. The flowchart in Figure 2-1 summarizes this process. In the figure, unshaded objects represent mechanisms and shaded objects represent policies.

As the first step in performing an access, a **local storage management** mechanism finds the local memory, if any, allocated to the shared-memory address. If there is no local

This model excludes systems which may perform individual loads and stores on a node other than the one on which they are issued. Examples include systems that use write-through or write-update caching of remote memory [BR90, WHL92, WJI<sup>+</sup>94, IDFL96] and those that migrate threads to data on misses [CR95]. Support for these models can conflict with some common implementation features—for example, writeback processor caches.

**Figure 2-1.** DSM memory access flowchart. If either the allocation check or the access check fails, the system must take action before the reference can be performed. The solid arrows indicate that the reference is suspended and later resumed without repeating the allocation and access checks. An alternate approach is to abort and retry the reference, as indicated by the dotted arrows.

memory for the referenced address, the mechanism invokes an allocation policy. This policy selects the local memory to allocate, possibly evicting previously cached data to make room. The policy interacts with local storage management to set up and tear down mappings from addresses to local memory. It also uses messaging to send evicted data to other nodes when necessary.

Once local memory is allocated, an **access control** mechanism determines whether that memory contains a valid copy of the data. If not, the mechanism invokes an access policy to acquire up-to-date data or additional access permissions. (A copy's validity may depend on the type of the access; in most protocols, replicated copies are valid for reading but not for writing.) The access policy includes both the global allocation policy, which selects the node to which a particular request is sent, and the coherence protocol, which determines how requests are handled. This policy uses both messaging and access control. For example, the policy may send messages telling other nodes to mark their copies invalid before it lets the local node write its copy.

In contrast to earlier work [Cha94, WCF<sup>+</sup>93], I do not consider operations internal to the coherence protocol (e.g., recording pointers to the nodes sharing a block) as mechanisms. This thesis seeks to identify *fundamental* mechanisms—mechanisms that cannot be synthesized efficiently. Stanford's FLASH system [KOH<sup>+</sup>94, HKO<sup>+</sup>94] and the Typhoon design described in Chapter 3 demonstrate that software protocols are not inconsistent with high-performance systems.

After the allocation and access control checks succeed, the system performs the access on the local copy.

Messaging, local storage management, and access control are three mechanisms that are fundamental to the operation of practically any DSM system. To allow flexible, efficient policies, systems must present these mechanisms to users in a practical fashion. The next section describes an interface designed to meet that need.

#### 2.2 The Tempest interface

Tempest is a concrete interface to the three abstract mechanisms identified in the previous section. One of Tempest's primary goals is portability across a wide cost/performance range. At the low-cost end, Tempest allows all-software implementations on generic message-passing hardware [SFL<sup>+</sup>94]. At the same time, the interface is amenable to hardware support. Chapter 3 describes a range of designs that provide hardware acceleration for Tempest; the most aggressive (Typhoon) is competitive in performance with dedicated distributed shared memory systems. The following sections describe the significant features of Tempest. (See Appendix A for a more complete interface specification.) Each of the abstract mechanisms is examined in turn. For messaging, Tempest borrows from the Active Messages model [vECGS92]. Standard virtual memory hardware supports local storage management. The most innovative aspect of Tempest is *fine-grain* access control, which is provided using a tagged memory model. The final section discusses mechanism interactions.

#### 2.2.1 Messaging

Most systems designed for explicit user message passing perform best on large, statically scheduled transfers. The implicit messaging behavior of DSM systems differs in the following ways:

- Messages are short: some contain only control information (e.g., a request for data), while others consist of control information plus a small amount of data (e.g., the response to a request). Assuming 64-bit addresses and 128-byte data transfers, we can estimate the former at 16-24 bytes, whereas the latter may be around 150 bytes.

- Most messages are handled asynchronously at the receiver. That is, requests for data and coherence operations are driven by the dynamic execution of other nodes, and are unrelated to the execution on the receiving node.

- The control information in messages originates in processor registers on the sender and is consumed in registers on the receiver.

- Low latency is important for high performance. Several techniques exist to tolerate memory latency—such as multithreading, prefetching, and non-blocking loads—but none of these is capable of hiding the latencies of most modern networks.

Tempest bases its messaging model on Active Messages [vECGS92], a flexible, lowoverhead messaging model designed for fine-grain message-based systems. The header of each message contains a pointer to a function that is invoked at the receiving node to handle the message arrival. These message handlers are invoked asynchronously with respect to the main thread of computation at the receiver. Each handler is responsible for disposing of the remainder of the message. To reduce scheduling and synchronization overheads, each handler is run to completion before another message handler is started.

Deadlock is an issue in any messaging system. The network buffers message data as it is routed to its destination. A node cannot send a message if there is no buffer space available in the network. A node may not simply wait for space to become available without removing any of the messages destined for it, because a cycle of nodes waiting for each other to remove their messages will deadlock. Because each Tempest (or Active Messages) message handler must complete before another handler is allowed to run, there is the potential for deadlock whenever a message is sent from within a message handler. Active Messages avoids deadlock by restricting handlers to sending at most one reply, and guaranteeing buffer space for that one message. However, this solution is awkward for DSM cache coherence protocols, in which a handler may send out multiple messages to update or invalidate all the sharers of a particular memory block. To avoid placing unnecessary burden on the user, Tempest places no restrictions on sending messages from within message handlers. In cases where these sends overflow the network, the runtime system buffers message data in the user's virtual memory. A truly errant process will be terminated when it exhausts the memory available to it. A similar approach is taken in the Fugu system [MKAK94].

In addition to the modified Active Messages model, Tempest includes a separate messaging interface for bulk data transfer. This alternate interface complements Tempest's Active Messages by providing asynchronous, high-bandwidth memory-to-memory communication for large amounts of data. Users set up *virtual channels* that bind a sending node with a buffer on the receiver.<sup>1</sup> The sender can transmit directly to the receiver's buffer without explicitly invoking a handler on the receiver. The sender can use the channel repeatedly without reestablishing it. Although this bulk interface can be implemented

<sup>1.</sup> This interface is modeled after the virtual channels facility in the CMMD library on the Thinking Machines CM-5, which similarly complements CMMD's CM Active Messages.

on top of Active Messages, it is included in the specification to give system developers the freedom to optimize the implementation—for example, by employing DMA hardware.

#### 2.2.2 Local storage management

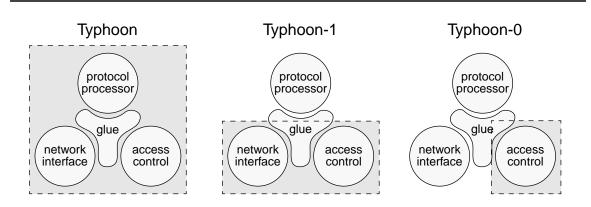

The second mechanism, local storage management, maps shared-memory accesses to local storage locations and invokes a software handler to allocate and map local storage if an unmapped address is referenced. The virtual address translation hardware found in most processors is suitable for this task, a fact that has been exploited in numerous DSM systems [LH89, CBZ91, BZS93, KDCZ94, HSL94]. Shared virtual addresses are mapped to local physical memory; a reference to an unallocated location results in a page fault.

Using virtual address translation for the local storage management mechanism has several advantages. Support is ubiquitous in modern processors, so portability is guaranteed. Capacity is bounded only by the available local memory. Associativity is practically unlimited. As long as the application's working set fits in the processor's TLB, the per-reference overhead is very low. There are two potential drawbacks. First, the cost of taking a page fault is typically large [ALBL91]. However, most of this overhead is due to operating system structure, so it can be greatly reduced at the cost of modifying the OS [RFW93, TL94]. Second, the virtual memory page size is large enough (typically four to eight kilobytes) to make fragmentation a concern. In cases where this occurs, the only real solution is to modify the application to improve its data layout or its reference pattern. Applications that suffer from fragmentation are also likely to suffer from poor TLB locality, so this type of optimization will pay off in both of these areas. (Table 3.2 on page 71 reports the observed fragmentation overhead for six applications.) The drawbacks are usually outweighed by the advantages: because allocation should be necessary for only a small fraction of references, the per-reference overhead typically has the greatest impact on performance.

The Tempest interface specifies functions to allocate and map, unmap, and remap pages, and to install a user function as the page fault handler.

#### 2.2.3 Access control

Access control is the mechanism that filters loads and stores, determining for each one whether action is required to obtain access rights to the referenced data. This mechanism can be viewed as a function that returns a single bit (action vs. no action) based on two inputs: (1) an access tag associated with the referenced address and (2) whether the access is a load or a store. Tempest provides three access tags: Invalid (action on both loads and stores), ReadOnly (action on stores but not loads), and Writable (no action on either loads or stores).<sup>1</sup> All three tags are necessary to support common multiple-reader, single-writer protocols. To reduce tag space overhead, a single access tag is associated with a memory *block* (an aligned, contiguous group of bytes). A reference that invokes an action is said to cause a *block access fault*. The thread that issued the reference is suspended, and a user function—the *block access fault handler*—is invoked. The block access fault handler initiates a protocol sequence that should culminate in acquiring access rights for the block, updating the access tag to allow the reference, and resuming the suspended thread.

Although only three access tags are required, implementations are unlikely to allocate fewer than two bits per block to encode these states. To exploit this extra capacity, Tempest specifies a fourth tag, Busy, which has the same access semantics as Invalid. For example, software can use the Busy tag to identify blocks which are inaccessible but for which there are outstanding requests.

Access control granularity can have a significant effect on performance due to *false sharing*: when different processors write different locations in the same block, a standard single-writer protocol will unnecessarily serialize the writes, causing potentially tremendous performance degradation as the block "ping-pongs" among the writing nodes [EK89]. A larger granularity makes false sharing both more likely and more difficult to remedy by rearranging or padding data.

<sup>1.</sup> There is a fourth possible tag with distinct semantics—one that invokes an action on loads but not stores—but such a "write only" tag is of no practical value.

Page-based DSM systems use virtual address translation hardware for access control as well as local storage management. As a result, the access control granularity is the virtual memory page size—four to eight kilobytes, typically—which easily leads to false sharing. To avoid ping-ponging these large pages, the most efficient page-based protocols allow multiple simultaneous writers for each page [CBZ91, KCZ92]. Unfortunately, these protocols trade significant computation and memory overheads for this reduction in communication. To merge updates from multiple nodes, each node isolates its contribution by comparing its modified copy with a second, unmodified local copy. Creating the unmodified copy and performing the comparison may take hundreds of microseconds [ACD<sup>+</sup>96].<sup>1</sup> As a result, these protocols are effective only when communication overheads are comparably large. In addition, these protocols support only weak consistency models.

Higher-performance hardware-based systems reduce false sharing by providing access control at cache-block granularity, typically 16 to 128 bytes. At these granularities, false sharing occurs less frequently and can usually be avoided by rearranging or padding application data structures. The protocol is free to focus on providing efficient coherence for true sharing patterns.

To provide portability to high-performance systems, Tempest specifies *fine-grain* access control. The number of bytes per block is implementation-specific, but must be a power of two no greater than 128. If Tempest allowed a coarser granularity, users would be forced to implement a multiple-writer protocol that is unsuitable for a high-performance system. Flexibility would also be impaired, because coherence policies would have to be tuned to dealing with false sharing rather than supporting actual application sharing patterns. The only potential drawback to specifying fine granularity is that it prevents the use of standard virtual memory; however, we have demonstrated an efficient, portable, software-only fine-grain access control technique [SFL<sup>+</sup>94].

<sup>1.</sup> These operations are memory intensive, so their performance is limited by memory bandwidths rather than computation rates.

While Tempest allows for low-cost, software implementations of fine-grain access control, it is specifically designed to support higher-performance hardware-assisted techniques as well. In [SFL<sup>+</sup>94], my colleagues and I enumerate five methods: in software, in the TLB, in the cache, in the memory controller, and in a bus snooping device. Chapter 3 describes three system designs that perform fine-grain access control in hardware via bus snooping. A detailed discussion of this technique appears in Appendix B.

The Tempest interface provides functions to read and change access tags and to register user functions as block access fault handlers. To allow implementations to optimize handler dispatch, users register separate handlers for each of the five possible fault types (read–Invalid, write–Invalid, read–Busy, write–Busy, and write–ReadOnly). Each handler invocation is passed the virtual address of the faulting access and two additional values associated with the referenced virtual memory page. These values, provided by the user when the page is allocated, are uninterpreted by Tempest but are intended to be used as a pointer to a per-page protocol data structure and to identify the page's home node.

For additional flexibility, users can register multiple sets of handlers. All block access faults on a particular page use the same set of handlers; the particular set is specified when the page is allocated. As described in Section 2.3, a typical protocol uses two sets of handlers, one for the page that contains the primary data copy and another for the cached copies on other nodes. The interface supports a larger number of handler sets to allow multiple protocols in the same application.

#### 2.2.4 Mechanism interactions

To support distributed shared memory effectively, the mechanisms described above must be designed to work together in an appropriate manner. This section describes two aspects of Tempest that cross mechanism boundaries: handler execution and atomic access control/messaging functions. Tempest systems run each message, allocation, and block access fault handler to completion before another handler of any type is invoked. In effect, Tempest extends the Active Messages handler execution model to include allocation (page) fault and block access fault handlers. Handlers enjoy mutually exclusive access to coherence protocol state without the overhead of locking. Unfortunately, this model precludes concurrent handler execution on multiprocessor nodes, which can increase throughput on communication-intensive benchmarks [FW96a].

Tempest also specifies functions that atomically change a block's access tag and send or receive the contents of the block. To understand why these calls are necessary, consider the common situation where a node must relinquish write access to a block and transmit the block's data to another node. Software must perform two actions: (1) change the block's access tag from Writable to Invalid and (2) send the block's contents. The tag change cannot be done first, because a block tagged Invalid cannot be accessed directly, even from inside a handler. (Because some implementations cannot easily disable access control for handlers, Tempest forbids handlers from performing accesses that could result in block access faults.) However, sending the block's contents first leads to a race: handlers are (possibly) concurrent with respect to computation threads (e.g., on multiprocessor nodes), so the block could be modified by another thread after the contents are sent but before the tag change occurs. Because the permanent copy of the block is the one in the message, this modification will be lost. A similar situation arises when a message arrives containing data for a previously Invalid block: the message handler is unable to write the data directly without first changing the tag, but changing the tag first creates a window where another thread could access incorrect data before the message data is written to memory.

#### 2.3 Transparent shared memory using Tempest

This section illustrates how Tempest can provide a standard shared-memory model in a manner transparent to the application—that is, the application uses only shared-memory

loads and stores; it does not observe the operation of the distributed shared memory layer or the underlying distributed-memory system. In contrast, the next section (Section 2.4) illustrates application-specific shared memory using Tempest, where applications customize the programming model and coherence protocol to improve performance.

The standard implementation of transparent shared memory (TSM) on Tempest is called *Stache*.<sup>1</sup> Stache is a user-level library that exploits the Tempest mechanisms. This library contains an allocation (page) fault handler, message handlers, block access fault handlers, and shared-memory allocation functions. Stache maps virtual addresses of shared data to local physical memory at page granularity, as do page-based software DSM systems [LH89]. However, Stache takes advantage of Tempest's fine-grain access control to maintain coherence at the block level. Because false sharing is not a major concern, Stache provides a strong consistency model using a standard single-writer, multiple-reader invalidation-based coherence protocol. The proposed Simple COMA design [HSL94] also combines page-granularity allocation with fine-grained invalidation-based coherence. However, Simple COMA uses a fixed hardware-implemented coherence protocol. In contrast, Stache is just one possible software protocol for Tempest systems.

In Stache, each shared page has a unique home node. Currently, Stache provides two home-node placement algorithms. The first assigns pages to nodes round-robin as they are allocated. The second algorithm—a simple first-touch migrate-once scheme [MKBS95]— attempts to reduce communication by placing each page on a node that references it. In this algorithm, the first node to access a page is the initial home. Unfortunately, all shared data written during the sequential initialization phase ends up on one node. To redistribute this data, the protocol also traps the first access to each page in the parallel portion of the code. If this access occurs on a node other than the initial home, that node will become the page's new, permanent home.

<sup>1.</sup> The name "Stache" is due to James Larus.

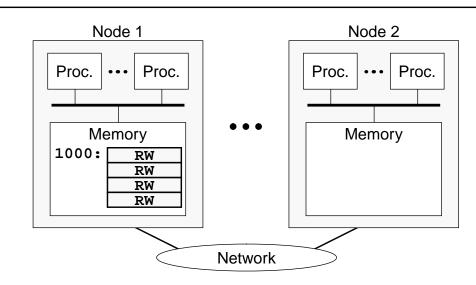

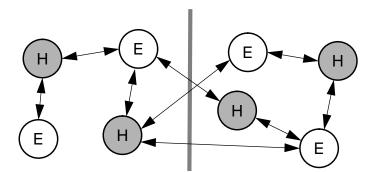

**Figure 2-2.** Stache example, step 1. Node 1 is the home node for the page at virtual address 1000. Node 1's processors have read-write access to all the blocks on the page (indicated by the **RW** label on each block). Node 2 has no mapping for virtual address 1000.

In either case, the home node uses a Tempest function to allocate a physical memory page and map it at the desired virtual address. It also allocates a vector of per-block directory structures (described later) on the program's heap and associates the home node's ID with the virtual page in a distributed mapping table. The page's block access tags are initialized to ReadWrite; as long as data on this page is not cached by another node, the home node can access it without software intervention. Figure 2-2 illustrates this situation, with node 1 serving as the home node for a shared data page.

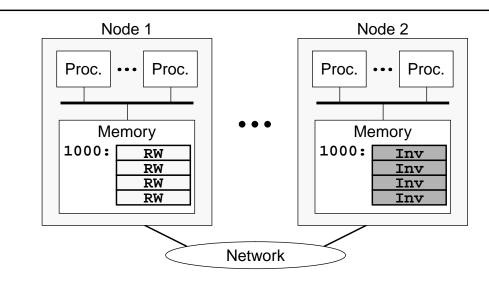

When another node first accesses a shared page, the reference causes an allocation (page) fault. The user-level allocation fault handler (part of the Stache library) allocates a physical memory page and maps it at the shared virtual address. To prevent concurrent computation threads from accessing the new page, the allocation function atomically sets the page's block access tags to Invalid. The handler also looks up the home node's ID in the distributed mapping table and stores it in a per-page data structure allocated on the heap. Finally, the handler restarts the thread at the faulting access. Figure 2-3 continues the example of Figure 2-2 to this point, with node 2 preparing to satisfy a reference to the shared data on node 1.

**Figure 2-3.** Stache example, step 2. Node 2 has mapped a memory page at address 1000 in response to an access from one of its processors. Because node 2 has no valid data for the page, the blocks on the page are marked invalid using the fine-grain access control mechanism (indicated by the **Inv** label on each block).

The restarted instruction now causes a block access fault because of the referenced block's Invalid tag. The block access fault handler retrieves the home node's ID from the page's local data structure, sends a request for the block, and terminates.<sup>1</sup> At the home node, the request message invokes a handler that performs the appropriate coherence actions and replies with the data. (If invalidations are required, the handler for the final invalidation acknowledgment message sends the data.) When the reply message arrives from the home node, the message handler writes the data into the allocated page, changes the block's access tag to ReadOnly or ReadWrite, and restarts the access. This time, the access completes and the program continues. Figure 2-4 illustrates the final stage of the example, where node 2 has obtained a shared data block from node 1.

Once a block is loaded into local memory, processors may access it repeatedly without protocol action. If the initial access was a read, the protocol tags the block ReadOnly; additional reads will complete locally, but the first write will invoke a block access fault

<sup>1.</sup> This initial request could be sent from the page fault handler, but the protocol software organization makes it simpler to keep a single copy of the request code in a block access fault handler.

**Figure 2-4.** Stache example, step 3. Node 2 has fetched a block of data from node 1 to satisfy the store access. In this example, node 2 obtains exclusive access to that block and node 1's copy is marked invalid. To satisfy a read access, node 2 would obtain a read-only copy, leaving node 1 also with a read-only copy.

handler to obtain an exclusive copy. Accesses to other blocks on the page, which are still tagged Invalid, avoid the page fault and directly invoke a block access fault handler.

When a node runs out of unused physical memory pages, accesses to additional shared data pages must reuse pages containing other cached data. In this case, the page fault handler selects a page to reuse, sends any modified data on the page back to its home, marks the page's blocks Invalid, and remaps the page at a new virtual address.

Blocks on the home page are initially ReadWrite, but are downgraded to ReadOnly or Invalid as remote nodes request read-only or exclusive copies. Thus references on the home node may require protocol action to reacquire a valid or exclusive copy. Stache registers a distinct set of block access fault handlers for home pages. These handlers directly access protocol data structures and perform needed coherence actions—for example, sending invalidation requests to caching nodes.

The Stache coherence protocol is similar to LimitLESS [CKA91], except that it is implemented entirely in software. The protocol allocates eight bytes of directory state per

cache block. Two bytes store the protocol state. The other six are typically used as six onebyte node pointers. (Full bytes are used, rather than a denser packing, to avoid bitfield operations.) If more than six pointers are required, four of the six bytes are used as a bit vector.

The protocol source code is independent of the coherence block size. The protocol can be compiled for any power-of-two block size—from the Tempest access-control granularity to the page size, inclusive—by defining a C preprocessor constant. Tempest aids this flexibility by including a block size parameter for access-control functions. Tempest implementations transparently support operations on any power-of-two multiple of the system's fine-grain access control granularity. (Non–power-of-two multiples are not supported directly because their use is rare and they complicate pointer alignment checks.)

Tempest allows the Stache implementation to emphasize speed and simplicity rather than generality. Although only one implementation is currently available, the library can provide several variations. Initialization code can install a version optimized for the number of nodes and block size—and perhaps other parameters—specific to that execution. For example, block sizes smaller than 128 bytes may use a protocol that allocates less than eight bytes per block. Systems larger than 32 nodes may use dynamic pointer allocation [SH91] to avoid multi-word bit vectors. Systems larger than 256 nodes will require multibyte node pointers. However, small systems need not pay at runtime to support these alternatives.

# 2.4 Optimizing applications using Tempest

The Stache protocol effectively supports applications written to a standard shared-memory programming model. However, the real power of Tempest lies in the opportunity it presents to optimize performance by tailoring the coherence protocol to the specific application. Because the protocol is simply user-level software—a set of functions linked in with the application—a programmer or compiler can customize protocols for specific data structures and specific phases of the application. Tempest allows users to bind a different set of block access fault handlers to each memory page, so multiple protocols—including Stache—can coexist peacefully, each managing a distinct portion of the shared data. Tempest gives programmers several paths to improve the performance of applications. They can:

- Select from available transparent-shared-memory protocols. Protocols can implement transparent shared memory (TSM) with a variety of policies (e.g., update vs. invalidate) and parameters (e.g., block size). Changing the coherence protocol for the entire application is as simple as linking with a different protocol library; using different protocols for different data structures requires only modest effort. Although some knowledge of the application is useful for selecting appropriate protocols, these changes cannot break a correct program. The range of available protocols should be expanded by the availability of high-level languages and compilers targetted for this domain [CRL96].

- Develop a protocol that exploits application-specific knowledge. Programmers or compilers can use precise knowledge of an application's synchronization and sharing patterns to optimize the coherence protocol aggressively. The program still executes in a shared address space, but an algorithmic change may require modifications to the coherence protocol as well. Most of the optimizations described in the examples below are of this type. In this work, these changes are performed manually, but the process can be automated using existing compiler techniques to extract access patterns from source code [VL96, DCZ96].

- Use message passing. Some operations, such as synchronization, fit the message-passing model naturally; in these cases, programmers can dispense with shared memory entirely. For example, the default lock and barrier implementations in Tempest's utility library use Tempest's Active Messages directly. Active Messages are also useful for building higher-level operations such as fetch-and-op and remote write.

This section illustrates some of these optimizations using six scientific applications. In each case, the programmer started with an optimized transparent–shared-memory parallel

**Figure 2-5.** Example EM3D bipartite graph. The vertical line represents a division of the graph across two nodes of a distributed-memory system.

program and further improved its communication behavior by developing custom protocols for critical data structures. I describe one of the applications—EM3D—in detail. Five other applications—Appbt, Barnes, DSMC, moldyn, and unstructured—were optimized by other members of the Wisconsin Wind Tunnel research group. I describe them here briefly to suggest the variety of optimizations that can be performed, and to provide background for the following chapters where all six of these applications are used as benchmarks. The original papers reporting on these optimizations (Falsafi et al. [FLR<sup>+</sup>94] for Appbt, Barnes, and EM3D,<sup>1</sup> and Mukherjee et al. [MSH<sup>+</sup>95] for DSMC, moldyn, and unstructured) detail the applications and the evolutionary optimization process.

# 2.4.1 EM3D

EM3D models electromagnetic wave propagation through three-dimensional objects  $[CDG^+93]$ . The principle data structure is a bipartite graph, in which *E nodes* represent electric field values and *H nodes* represent magnetic field values (see Figure 2-5). The main computation iteratively updates the field values to model the passage of time. Each iteration has two phases. The first computes new values for the E nodes using a weighted sum of their neighboring H node values. The second updates the H node values similarly based on the new values of their neighboring E nodes.

<sup>1.</sup> I wrote the original Tempest application-specific protocol for EM3D as part of the original paper on Tempest and Typhoon [RLW94]. This protocol was further analyzed and improved by Falsafi and Rogers [FLR<sup>+</sup>94].

```

typedef struct e_node {

double

/* field value at this node */

value;

edge_count; /* number of edges/neighbors */

int

/* vector of edge weights */

double

*weights;

struct h_node *(*h_nodes); /* vector of adjacent H nodes */

struct e node *next;

/* next local E node */

};

void compute E()

struct e node *n;

int i;

for (n = e_nodes; n != NULL; n = n->next)

for (i = 0; i < n -> edge_count; i++)

n->value -= n->h_nodes[i]->value * n->weights[i];

}

main()

{

int iter;

for (iter = 0; iter < num iters; iter++)</pre>

{

compute_E();

barrier();

compute_H();

barrier();

}

}

```

**Figure 2-6.** EM3D program fragment. The struct h\_node type and compute\_H() function are symmetric with struct e\_node and compute\_E(), respectively.

Figure 2-6 lists part of the shared-memory EM3D code. The parallel version assigns a set of E nodes and a set of H nodes to each processor. During each iteration, every processor updates its own nodes. Because only one processor updates each node, no locking is required. A barrier after each phase guarantees that all the new values for one type of node have been written before any processor starts reading the values to update the other nodes.

On a distributed-memory system, the program reduces traffic by allocating the graph nodes—that is, by placing their Stache home pages—in memory local to the processor that owns them. Communication occurs only when one processor reads a value that is

written by another, which happens when a graph edge connects nodes owned by different processors. Unfortunately, transparent shared memory does not support this producer– consumer communication pattern efficiently. When a processor reads a remote graph node value, the coherence protocol fetches the value and caches it. In the next phase, the owning processor updates the node value, causing the protocol to invalidate the cached copy. Thus in each iteration, each communicated value is fetched, cached, and invalidated, which requires at least four messages (request, response, invalidation, and acknowledgment). I optimized the transparent shared memory version to amortize this overhead by placing multiple values in a cache block. This optimization modifies the graph node data structure, replacing the embedded value with a pointer into a packed value array.

Tempest lets us optimize communication much more directly by using a custom protocol for the graph nodes. In the first iteration, this protocol behaves very much like the Stache protocol: references to remote values invoke block access fault handlers, which fetch and cache the data. Unlike Stache, the protocol records information regarding the addresses and nodes that are involved in each request. Because the graph does not change during execution, each requester needs the same set of addresses in every iteration. This set cannot be determined statically because the graph structure is input dependent.

After the first iteration, the protocol switches to update mode. After each phase, each processor uses the sharing information obtained in the first iteration to send updated values to the processors that need them. Because the updates are simply user-level messages, the protocol sends only the modified values, not full cache blocks. To further reduce overheads, the protocol packs all the values destined for a particular processor in a single message, and transmits that message using Tempest's virtual channels (see page 17). Each node also determines, from the information collected in the first iteration, how many update messages it should receive; the full barrier is replaced by a loop that waits until all of the expected messages arrive.

Using this custom Tempest protocol, iterations after the first reduce communication to one message between each producer–consumer pair, the same level of communication efficiency—and the same level of performance  $[FLR^+94]$ —as a message-passing implementation. However, the program retains its original shared-memory structure. The only changes to the code in Figure 2-6 are a function call to initialize the custom protocol, a call to notify it of the end of the first iteration, and calls to the new function that combines the updates and synchronization (replacing the barriers). The graph data structure is still pointer based; neither the struct e\_node type nor the compute\_E() function changes. The initialization code (not shown in Figure 2-6) uses a new memory allocation function that places the graph nodes on pages serviced by the custom protocol, but is otherwise unchanged. In contrast to the few simple changes in the original source, the custom protocol's complexity somewhat; this code represents one of the earliest custom protocols, and was written without the aid of experience or protocol development tools.

Although other programming models may achieve similar levels of efficiency, they generally require more drastic modifications to the program's code and data structures. For example, the optimized Split-C version modifies the graph itself, explicitly inserting local "ghost nodes" to cache remote values [CDG<sup>+</sup>93]. The optimized TSM version described earlier adds a level of indirection from the graph nodes to their values to increase locality. Even with this non-intuitive change, the TSM version falls well short of the Tempest version's efficiency. In contrast, the optimized Tempest program still enjoys the advantages of a shared-memory model: pointer-based data structures in a uniform, global address space.

## 2.4.2 Appbt

Appbt is a three-dimensional computation fluid dynamics code from the NAS Parallel Benchmarks collection [BBLS91], parallelized for transparent shared memory by Burger and Mehta [BM95]. The primary data structure is a three-dimensional dense matrix. The parallel version assigns a subcube of the matrix to each processor. All communication