## Design and Evaluation of Network Interfaces for

System Area Networks

by

Shubhendu Sekhar Mukherjee

A dissertation submitted in partial fulfillment of

the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

## UNIVERSITY OF WISCONSIN—MADISON

1998

© Copyright by Shubhendu S. Mukherjee, 1998

All Rights Reserved

### Abstract

Much of a computer's communication performance is determined by how well it interacts with networks. Such interaction is critical for latency-sensitive applications, such as parallel programs that send frequent, short messages. Fortunately, networks have improved dramatically, especially System Area Networks (SANs). SANs provide submicrosecond latency, gigabytes per second bandwidth, and very high reliability to 10-100 hosts. Unfortunately, this dramatic improvement in network performance is seldom delivered to applications. A key bottleneck is the host network interface (NI), which connects a network to a host computer. For example, conventional NIs are usually accessed via direct memory access or uncached, memory-mapped device registers, which can incur latencies between ten and hundreds of microseconds.

This thesis investigates novel techniques to improve interactions between a processor and a SAN NI. A key principle underlies these techniques: *treat NI access as regular, sideeffect-free memory access, and not as a disk interface access.* The thesis' first contribution shows that such treatment opens up at least eight opportunities for improving processor-NI interactions.

This thesis' second contribution is the design and evaluation of a novel class of NIs called *Coherent Network Interfaces* (CNIs). CNIs realize the key principle enunciated in this thesis. CNIs appear to their hosts more like regular, cachable memory than like a disk interface and exploit all eight opportunities for improving processor-NI interactions.

The thesis' third contribution is a systematic classification and evaluation of NI data transfer and buffering parameters. I evaluate these parameters in the context of several commercial and research NIs.

Finally, this thesis' last contribution is the *Cosmos* coherence message predictor. This part differs significantly from the rest of this thesis. Coherence protocol message predic-

ii

tion can accelerate the performance of directory protocols, which are used by most large shared-memory multiprocessors to keep per-processor caches coherent. Cosmos predicts the source and type of the next coherence message for a cache block using general prediction logic that is extension of Yeh and Patt's PAp branch predictor. For five scientific applications running on 16 processors, Cosmos' prediction accuracy ranges between 62% and 93%.

### Acknowledgments

Many people helped in making this dissertation possible and my bumpy ride through graduate school bearable. In particular, I am greatly indebted to two people: my advisor Mark Hill and my wife Mimi. Mark provided valuable guidance, encouragement, and criticism from the very first day I came to Wisconsin. Mark likes to teach by examples. To me Mark himself was the example and a role model. By watching Mark I learned how to discipline and balance my professional and social lives. I am thankful to him for the patience and the understanding with which he taught me the tricks of our trade.

In every step Mimi supported and encouraged me to complete my dissertation. She not only celebrated my successes, but also endured all my frustrations. Without her constant companionship and understanding I would not have finished this dissertation.

Jim Larus, Guri Sohi, and David Wood were great inspirations. Jim and David were a constant source of novel ideas. Guri's insightful comments helped improve my work.

My family helped and encouraged me in many different ways. My father, who did a Ph.D. himself, always encouraged me to pursue a Ph.D. My mother, who founded her own school, taught me that you can achieve anything in life if you set your mind to it. My brother (Dipu), sister-in-law (Tutu), and Mimi's sister (Riki) helped provide a supportive family environment. Mimi's parents' provided advice and support whenever needed. Finally, both my and Mimi's family patiently endured my absence from many family reunions.

The Wisconsin Wind Tunnel project, colleagues outside Wisconsin, and the Computer Sciences department at UW-Madison provided me with tools I needed to complete this dissertation. In particular, Steve Reinhardt, Babak Falsafi, and Mike Litzkow helped develop and debug the Wisconsin Wind Tunnel II (WWT II) parallel simulator, which I used for most of my experiments in this thesis. Fred Chong and Shamik Sharma provided me with one of the benchmarks (*spsolve*) I used in this thesis. The Computer Sciences department provided me with a tremendous amount of computing resources I needed for my simulations. In particular, the seven Sun Enterprise servers—most of them equipped with 16 250-MHz UltraSPARC processors—and the 40-node Wisconsin COW (Cluster of Workstations) provided rapid turnaround time for my parallel simulations with WWT II.

The architecture faculty at Wisconsin—Mark Hill, Jim Goodman, Jim Smith, Guri Sohi, and David Wood—have created a congenial atmosphere in which graduate students can interact freely and openly with faculty. The architecture students at Wisconsin were always willing to listen to my ideas and provide valuable criticism about them. In particular, Vijay—presently Prof. Vijaykumar at Purdue University—patiently listened to and criticized many of my ideas and provided valuable advice regarding the mechanics of graduate school.

Several people provided valuable feedback and information for this thesis. Mark Hill, Guri Sohi, and David Wood patiently read through this thesis. Nick Carter, Bob Felderman, Mike Galles, Leonidas Konthothanassis, Whay Lee, Ken Mackenzie, Toshi Shimizu, and Bob Zak provided valuable information regarding several commercial and research networks and network interfaces. Tom Anderson, Babak Falsafi, Suresh Chalasani, Satish Chandra, Erik Hagersten, Rebecca Hoffman, Stefanos Kaxiras, Larry Landweber, Jim Larus, Ken Mackenzie, Rich Martin, Subbarao Palacharla, Larry Peterson, Steve Reinhardt, Avinash Sodani, T.N.Vijaykumar, Jon Wade, and Bob Zak provided valuable comments on this work.

My dissertation research was supported in part by Wright Laboratory Avionics Directorate, Air Force Material Command, USAF, under grant #F33615-94-1-1525 and ARPA order no. B550, National Science Foundation with grants MIP-9225097, MIPS-9625558, and CDA-9623632, and donations from Sun Microsystems.

Finally, I would like to thank *Eureka Joe's* for providing me with a constant supply of cappucino and a place to sit, think, and relax during my tenure in graduate school.

## **Table of Contents**

| Abstrac   | xti                                                             |

|-----------|-----------------------------------------------------------------|

| Acknow    | vledgmentsiii                                                   |

| Table o   | f Contentsv                                                     |

| List of l | Figuresix                                                       |

| List of 7 | Tables   xi                                                     |

| Chapte    | r 1. Introduction                                               |

| 1.1       | Components of a Network Interface                               |

| 1.2       | Problems with Conventional Network Interfaces                   |

| 1.3       | Future Trends                                                   |

| 1.4       | Thesis Contributions for Network Interfaces                     |

| 1.5       | Using Prediction to Accelerate Coherence Protocols              |

| Chapte    | r 2. Treat Network Interface Access as Memory Access            |

| 2.1       | Use Virtual Memory Hardware to Virtualize the Network Interface |

| 2.2       | Place the Network Interface on the Memory Bus                   |

| 2.3       | Use Virtual Memory to Buffer Network Messages                   |

| 2.4       | Cache NI Registers in Processor and NI Caches                   |

| 2.5       | Allow Out-of-Order and Speculative Accesses to NI Memory        |

| 2.6       | Move Data Between a Processor and an NI in Cache Block Units    |

| 2.7       | Use Memory-Based Queues as Application Programming Interface    |

| 2.8       | Use Cache Invalidations as Notification Signals                 |

| 2.9       | Conclusion                                                      |

| Chapte | r 3.  | Coherent Network Interfaces Techniques41                          |

|--------|-------|-------------------------------------------------------------------|

| 3.1    | Cac   | hable Device Register (CDR)42                                     |

|        | 3.1.1 | Basic CDR operation                                               |

|        | 3.1.2 | Advantages of a CDR                                               |

|        | 3.1.3 | Disadvantages of a CDR                                            |

| 3.2    | Cac   | hable Queues (CQs)                                                |

|        | 3.2.1 | Basic CQ Operation                                                |

|        | 3.2.2 | CQ Optimizations                                                  |

| 3.3    | Hon   | ne                                                                |

|        | 3.3.1 | Operating System Issues                                           |

|        | 3.3.2 | Performance Issues                                                |

| 3.4    | CNI   | Taxonomy                                                          |

| 3.5    | CNI   | s on I/O buses                                                    |

| 3.6    | Mul   | tiprogramming CNIs                                                |

|        | 3.6.1 | Ensuring Protected Access to the NI                               |

|        | 3.6.2 | Providing the NI with Physical Addresses of Message Data          |

|        | 3.6.3 | Allowing Multiple Processes to Simultaneously Access the NI       |

|        | 3.6.4 | Detecting the Generation of New Messages by Different Processes75 |

|        | 3.6.5 | Multiprogrammed CNI <sub>i</sub> Q <sub>m</sub> Datapath          |

| 3.7    | Inte  | rfacing CNIs with Standard Networks                               |

| 3.8    | Rela  | ated Work                                                         |

| 3.9    | Sum   | 1 mary                                                            |

| Chapte | r 4.  | An Evaluation of Coherent Network Interfaces                      |

| 4.1    | Netv  | work Interfaces Simulated                                         |

| 2      | 4.1.1 | NI <sub>2w</sub> Implementation                                   |

| 2      | 4.1.2 | CNI <sub>4</sub> Implementation                                   |

| 2      | 4.1.3 | CNI <sub>32</sub> Q and CNI <sub>512</sub> Q Implementations85    |

vi

|            | vii                                                                |

|------------|--------------------------------------------------------------------|

| 4.2 Sim    | ulation Methodology                                                |

| 4.2.1      | Wisconsin Wind Tunnel II Simulator                                 |

| 4.2.2      | Simulation Parameters                                              |

| 4.2.3      | Macrobenchmarks                                                    |

| 4.3 Mic    | robenchmark Results                                                |

| 4.3.1      | Round-Trip Latency                                                 |

| 4.3.2      | Bandwidth                                                          |

| 4.4 Maa    | crobenchmark Results                                               |

| 4.4.1      | Performance Comparison of five NIs on Memory and I/O Buses         |

| 4.4.2      | $CNI_{32}Q_m$ and $CNI_{512}Q$ Speedup                             |

| 4.5 Imp    | act of Network Latency                                             |

| 4.6 Con    | clusions                                                           |

|            |                                                                    |

| Chapter 5. | Impact of Data Transfer and Buffering Alternatives113              |

| 5.1 Data   | a Transfer Parameters                                              |

| 5.1.1      | Size of Transfer                                                   |

| 5.1.2      | Degree of Processor Involvement for Transfer                       |

| 5.1.3      | Source and Destination of Transfer                                 |

| 5.2 Buf    | fering Parameters                                                  |

| 5.2.1      | Location of NI Buffers                                             |

| 5.2.2      | Degree of Processor Involvement for Buffering                      |

| 5.3 Net    | work Interface Implementations                                     |

| 5.4 Res    | ults                                                               |

| 5.4.1      | Microbenchmarks                                                    |

| 5.4.2      | Macrobenchmarks                                                    |

| 5.4.3      | Single-Cycle NI <sub>2w</sub> vs. CNI <sub>32</sub> Q <sub>m</sub> |

| 5.5 Rela   | ated Work                                                          |

|            |                                                                    |

| Chapter 6. | Using Prediction to Accelerate Coherence Protocols          |

|------------|-------------------------------------------------------------|

| 6.1 Bac    | ckground                                                    |

| 6.1.1      | Structure of a Directory Protocol                           |

| 6.1.2      | Two-Level Adaptive Branch Predictor144                      |

| 6.2 Pre    | dicting Coherence Protocol Messages144                      |

| 6.2.1      | Signature Generated by Producer-Consumer Sharing Pattern145 |

| 6.2.2      | Basic Structure of Cosmos                                   |

| 6.2.3      | Obtaining Predictions from Cosmos                           |

| 6.2.4      | Updating Cosmos                                             |

| 6.2.5      | How Cosmos Adapts to Complex Coherence Message Streams?149  |

| 6.2.6      | Filtering Noise from Coherence Message Stream               |

| 6.2.7      | Implementation Issues for Cosmos                            |

| 6.3 Usi    | ng Coherence Protocol Message Predictors                    |

| 6.3.1      | Mapping predictions to actions                              |

| 6.3.2      | Detecting when to perform actions                           |

| 6.3.3      | Handling mis-predictions154                                 |

| 6.4 Me     | thodology                                                   |

| 6.4.1      | Wisconsin Stache Protocol                                   |

| 6.5 Res    | sults                                                       |

| 6.5.1      | Basic Prediction Rate                                       |

| 6.5.2      | Additional Analysis166                                      |

| 6.6 Inc    | reasing Cosmos' Accuracy168                                 |

| 6.7 Co     | mparison with Directed Optimizations169                     |

| 6.8 Sur    | nmary and Conclusions                                       |

| Chapter 7. | Thesis Summary                                              |

| Appendix A | . System Area Networks                                      |

# **List of Figures**

| Figure 1-1. | Three components of message latency                                    |

|-------------|------------------------------------------------------------------------|

| Figure 1-2. | High-level views of an NI5                                             |

| Figure 1-3. | A shared-memory multiprocessor                                         |

| Figure 2-1. | Workstation Nodes with Network Interfaces                              |

| Figure 2-2. | Trends in peak SAN link bandwidth and I/O bus bandwidth22              |

| Figure 2-3. | Three examples of side-effects in existing NI designs                  |

| Figure 3-1. | CDR Transfer Example                                                   |

| Figure 3-2. | Cachable Queues                                                        |

| Figure 3-3. | A Cachable Queue (CQ) with four messages                               |

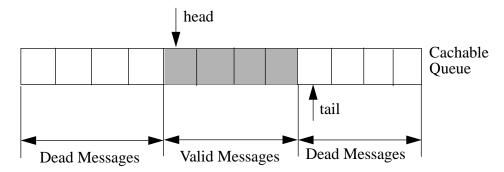

| Figure 3-4. | Dead message elimination                                               |

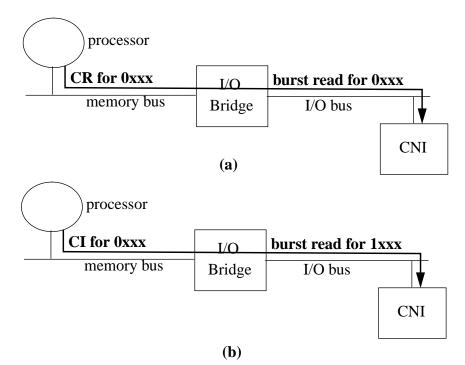

| Figure 3-5. | Illustration of shadow address with a CNI on the I/O bus               |

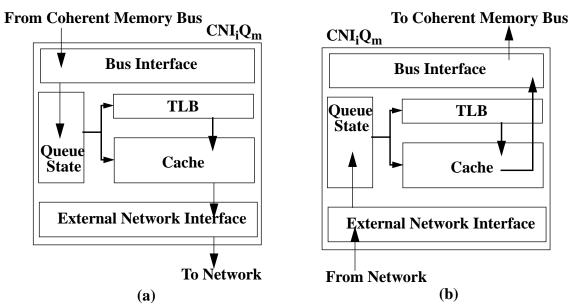

| Figure 3-6. | Logical datapath through multiprogrammed $CNI_iQ_m$ device             |

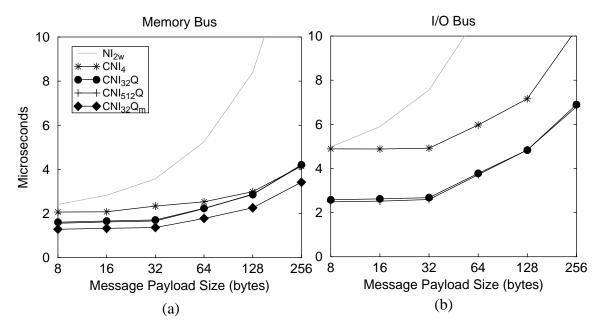

| Figure 4-1. | Process-to-process round-trip message latency                          |

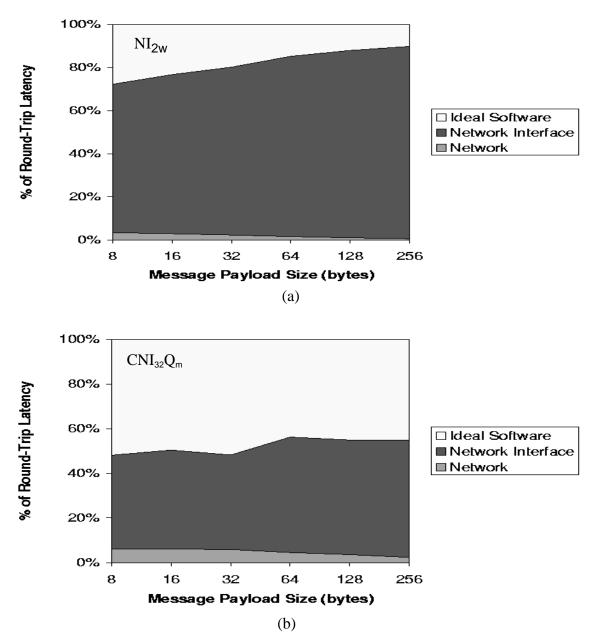

| Figure 4-2. | Breakdown of round-trip latency for $NI_{2w}$ and $CNI_{32}Q_{m}$      |

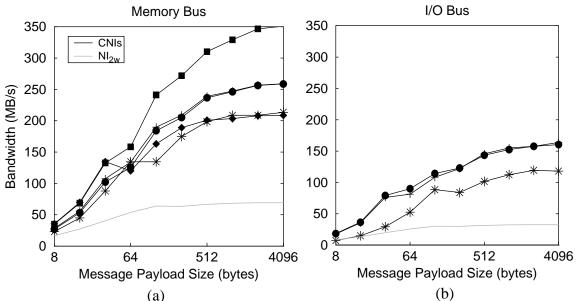

| Figure 4-3. | Process-to-process message bandwidth                                   |

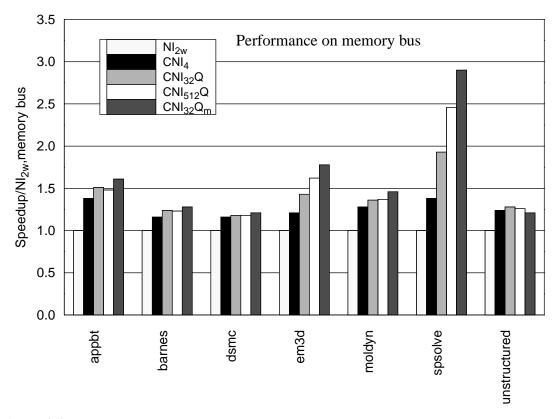

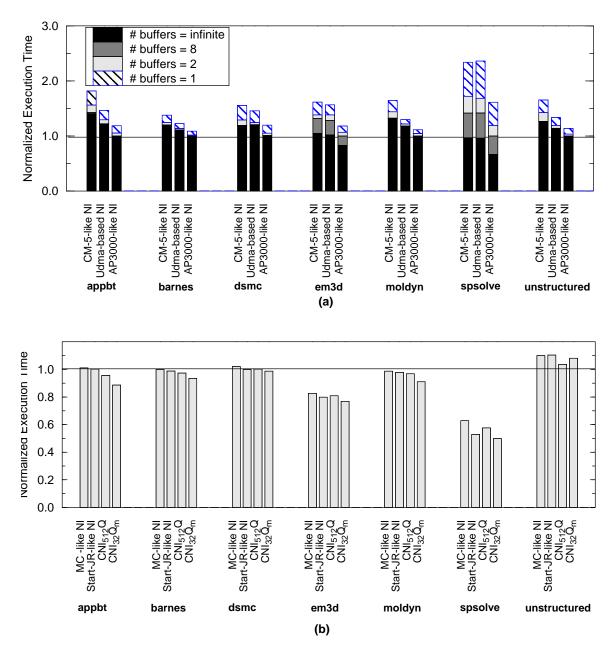

| Figure 4-4. | CNIs' performance on the memory bus                                    |

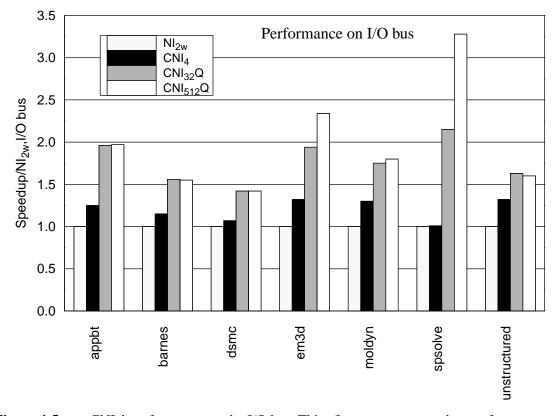

| Figure 4-5. | CNIs' performance on the I/O bus                                       |

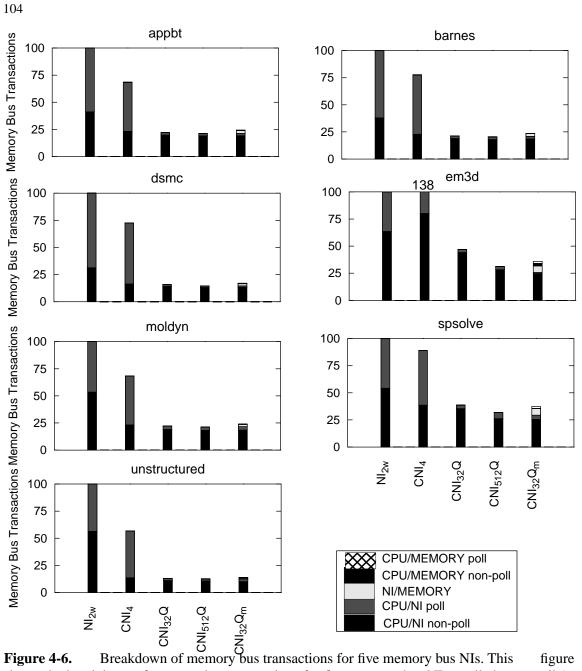

| Figure 4-6. | Breakdown of memory bus transactions for five memory bus NIs 104       |

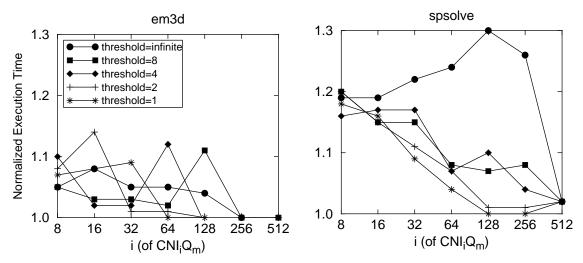

| Figure 4-7. | $CNI_iQ_m$ cache size variation                                        |

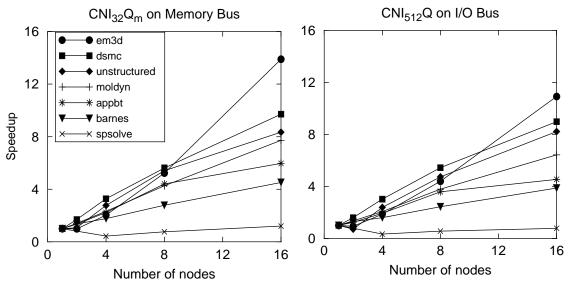

| Figure 4-8. | Macrobenchmark speedup                                                 |

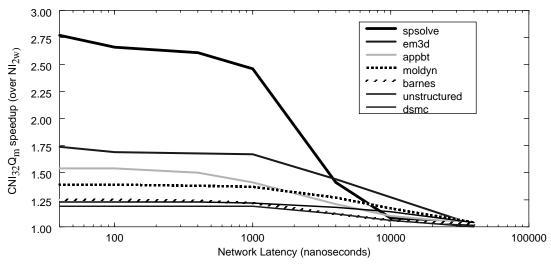

| Figure 4-9. | Impact of Network Latency                                              |

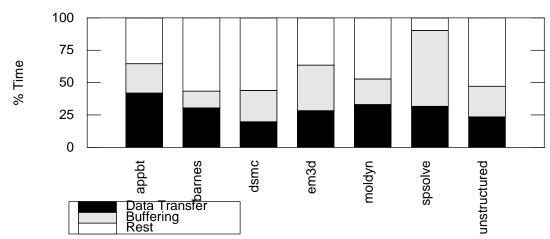

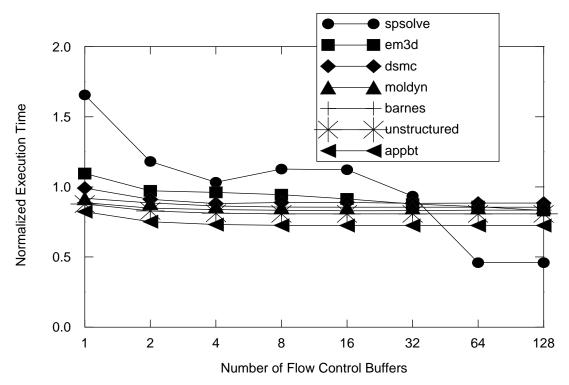

| Figure 5-1. | Impact of data transfer and buffering                                  |

| Figure 5-2. | Comparison of execution time of seven NIs                              |

| Figure 5-3. | Comparison of execution of a single-cycle $NI_{2w}$ with $CNI_{32}Q_m$ |

| Figure 6-1. | Basic structure of a directory protocol                                |

| Х           |                                                                       |

|-------------|-----------------------------------------------------------------------|

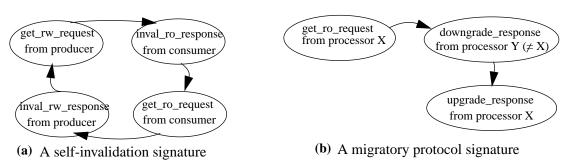

| Figure 6-2. | Message signature generated by a producer-consumer sharing pattern146 |

| Figure 6-3. | Cosmos' structure                                                     |

| Figure 6-4. | Two examples of using prediction to accelerate coherence protocols153 |

| Figure 6-5. | Dominant (incoming) message signatures for appbt, barnes, and dsmc160 |

| Figure 6-6. | Dominant (incoming) message signatures for moldyn and unstructured161 |

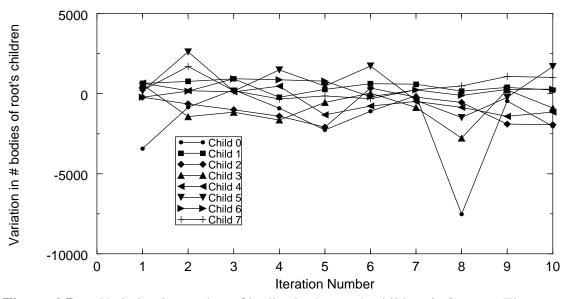

| Figure 6-7. | Variation in number of bodies in the root's children in barnes        |

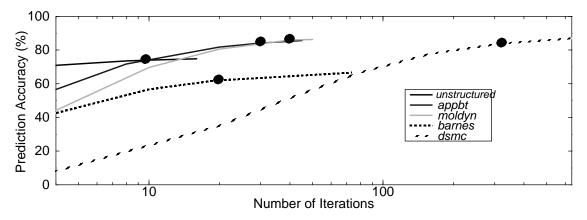

| Figure 6-8. | Cosmos' time to adapt                                                 |

| Figure 6-9. | Signatures for dynamic self-invalidation and migratory protocols171   |

|             |                                                                       |

## List of Tables

| Table 2.1: | Treat NI access as memory access and not as a disk interface access18        |

|------------|------------------------------------------------------------------------------|

| Table 2.2: | Error model for networks and memory                                          |

| Table 3.1: | Steps in the three-cycle handshake                                           |

| Table 3.2: | CQ state at sender and receiver                                              |

| Table 3.3: | Summary of CQ optimizations                                                  |

| Table 3.4: | Coherent Network Interfaces on I/O buses                                     |

| Table 3.5: | Comparison of CNI with other network interfaces                              |

| Table 4.1: | Summary of Network Interface Devices                                         |

| Table 4.2: | System parameters for simulated system                                       |

| Table 4.3: | Summary of macrobenchmarks                                                   |

| Table 4.4: | $NI_{2w}$ 's slowdown on the I/O bus                                         |

| Table 4.5: | Percentage of a cache block space wasted for CNI <sub>4</sub> <sup>102</sup> |

| Table 4.6: | Percentage of messages buffered explicitly for memory bus NIs103             |

| Table 4.7: | Breakdown of memory bus cycles for $NI_{2w}$ and $CNI_{32}Q_m$               |

| Table 5.1: | Buffering in commercial networks                                             |

| Table 5.2: | Classification of memory bus NIs                                             |

| Table 5.3: | Process-to-process round-trip latency for seven NIs                          |

| Table 6.1: | Sample of coherence messages                                                 |

| Table 6.2: | Examples of prediction-action pairs in existing protocols                    |

| Table 6.3: | Number of iterations for each benchmark                                      |

| Table 6.4: | Cosmos' prediction rates (expressed in percentage of hits)                   |

| Table 6.5: | Cosmos' prediction accuracy with filters                                     |

| Table 6.6: | Dsmc's prediction accuracies for specific transitions                        |

| Table 6.7: | Memory overhead of Cosmos predictors (with no filter)                        |

| Table 6.8: | Using processor numbers to improve Cosmos' accuracy                          |

xii

For your dissertation you must think of one thought that no one has thought before.

- Pasupati Mukerjee, Emeritus Professor, School of Pharmacy, U. of Wisconsin-Madison xiv

## Chapter 1

## Introduction

The term "computer" is perhaps a misnomer today. A modern computer system often "communicates" with a communication network more than it "computes." Consequently, much of a computer's value depends on how well it interacts with networks. To enhance this value, designers must improve the communication performance delivered to users. The aspect of communication performance that is quoted most commonly is *bandwidth*. Bandwidth is the rate at which data can flow through the network and computer. High bandwidth is critical when transmitting high-quality video or large files. An under-appreciated aspect of communication is *latency*. Latency is the user-to-user delay for sending a message. Latency determines performance of applications that send many small messages, as can be found in fine-grain parallel computing, network file systems, database lock managers, and world-wide web requests.

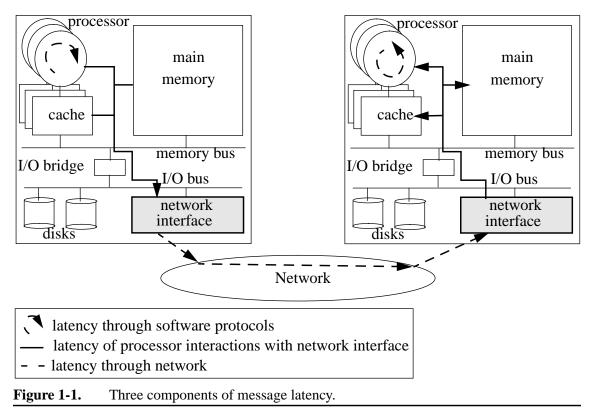

Latency of communication can be broken into three important components (Figure 1-1):

- latency through software protocols that generate and consume messages,

- latency through the network, and

• latency of processor interactions with a *network interface (NI)* that connects a computer with a network.

The advent of high-performance microprocessors with supercomputer-like clocks, lean software protocols (e.g., [127, 128]), and high-speed reliable networks with tens of nano-seconds latency (e.g., [41]) have drastically reduced the impact of software protocols and networks on the overall latency of communication. Consequently, the third component—processor interactions with an NI—threatens to become a critical bottleneck, particularly for a cluster of workstations connected with a high-speed network.

An NI is a device that sends and receives messages from the network on behalf of the computer. To send or receive a message a processor (and/or memory system) must interact with the NI by reading and writing messages into the device. Conventional NIs were designed for slower processors, heavy-weight protocols, and slow and unreliable networks. Consequently, processor interactions with conventional NIs incur large compo-

nents of latency. For example, conventional NIs are usually accessed via low-level software (e.g., device driver) inside the operating system, located on slower I/O buses, and accessed via direct memory access (DMA) or uncached, memory-mapped device registers. Each of the these components can add between ten and hundred microseconds latency to the total latency seen by a message [5, 127, 11].

The key problem with conventional NIs is that a processor interacts with them in almost the same way it interacts with disk interfaces. For example, disk-resident files are usually accessed via the operating system and read into memory using direct memory access (DMA). However, technological advances have made current networks between four to five orders of magnitude faster than disks. Consequently, NIs must be redesigned to accommodate this new generation of high-speed networks.

This thesis proposes and evaluates novel techniques to improve a processor and memory system's interactions with an NI. That is, this thesis examines techniques to improve an NI's internal interface to a computer and *not* its external interface to networks. These techniques reduce the overall message latency to a few microseconds. Other related projects and designs have proposed using reflective memory techniques to directly deposit data from a processor's cache or memory in one node to another node's memory [44, 12]. The techniques described in this thesis can further improve the performance of communication via reflective memory. This is because the techniques proposed in this thesis improves the important component of latency: processor-NI interactions, which is critical even for reflective memory (see Chapter 5).

The NI techniques I propose in this thesis are most relevant to a Cluster of Workstations (COW). A COW is a parallel machine built with commodity workstations and connected with a high-speed and reliable System Area Network (Appendix A). COWs are attractive over traditional massively parallel machines (MPPs) because COWs have the potential to offer performance similar to MPPs, but at a reduced price. The reduced price of COWs

arise from the commodity nature of its parts—commodity workstations, commodity operating system, and (perhaps) commodity network.

This thesis makes four contributions:

- The first contribution of this thesis (Chapter 2) is the development of a key NI design principle: *treat NI access as regular, side-effect-free memory access, and not as a disk interface access.* I show how treating a processor's access to an NI as a regular memory access can significantly improve processor-NI interactions.

- The second contribution of this thesis is the design (Chapter 3) and evaluation (Chapter 4) of a novel class of NIs called *Coherent Network Interfaces (CNIs)*, which interact with a processor and memory system via cachable, coherent memory operations. CNIs are the embodiment of the design principle mentioned above.

- The third contribution of this thesis (Chapter 5) is a systematic classification, examination, and evaluation of NI data transfer and buffering parameters, which have significant impact on the performance of processor-NI interactions.

- Finally, the fourth contribution (Chapter 6) differs significantly from the rest of this thesis. Techniques discussed in the rest of the thesis can accelerate user-to-user messaging in a parallel machine programmed with a message-passing programming model. In contrast, Chapter 6 examines techniques to accelerate the communication performance of parallel machines that are programmed with a shared-memory model. Most large shared-memory machines use a directory protocol to keep per-processor caches coherent. Unfortunately, these protocols often incur long latencies due to either long protocol actions or multiple message exchange. This chapter proposes and evaluates the *Cosmos* coherence protocol message predictor, which can help ameliorate this latency by predicting with high accuracy the next incoming coherence message for a cache block.

Finally, Chapter 7 summarizes this thesis and provides directions for future work. Appendix A describes the characteristics of a new generation of networks called system area networks.

4

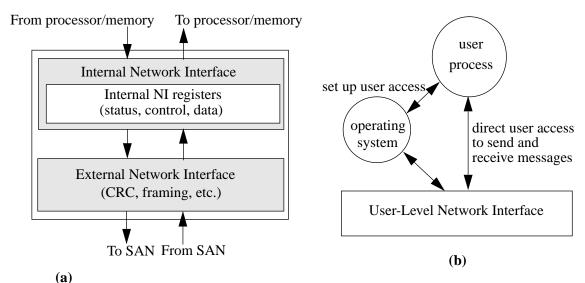

**Figure 1-2.** High-level views of an NI. (a) shows the building blocks of an NI. (b) shows how a user process can logically access an NI.

The rest of this chapter is organized as follows. Section 1.1 describes the key components of an NI. Section 1.2 outlines problems with conventional NI designs. Section 1.3 argues why these problems will become even more critical in the future. Section 1.4 states my proposed solutions and discusses contributions of this thesis. Section 1.5 motivates and examines the Cosmos coherence message predictor.

#### **1.1 Components of a Network Interface**

A network interface (NI) in a host node is a device that allows a processor to send and receive messages to and from a network that connects these host nodes. The network accepts messages from an NI and delivers them to one or more NIs connected to the network. An NI consists of two parts, the internal NI and the external NI (Figure 1-2a). I define the internal NI as the NI's interface to the processor, main memory, and (perhaps) disks, and external NI as the NI's interface to the network. The internal NI contains logic and memory that the processor uses to send and receive messages to and from the NI. For example, a processor can send a message to the network by writing messages to the data registers of the internal NI In contrast, an external NI performs network-specific functions, such as cyclic-redundancy checks, network-specific framing, etc.

This thesis examines the architecture of an internal NI. An internal NI consists of two parts: the send interface and the receive interface. Each interface consists of four components: status registers, control registers, data registers, and an optional notification mechanism. *Here I use the term registers just as an architectural specification*; the registers, for example, may be implemented with DRAM. I will examine alternative implementations of these registers and notification mechanism later. In this section, I discuss the function of each of the components.

**Status Registers.** NI status registers contain NI device status information. A receive interface status register, for example, can indicate that a new message has arrived from the network, and a send interface status register can indicate that the NI has successfully injected a message into the network.

**Control Registers.** NI control registers allows a user process to pass information and commands to the NI device. For example, a processor may want NI interrupts disabled in a critical section. It can do so by writing to a control register in the NI.

**Data Registers.** NI data registers contain message data sent by a processor or received by the NI from the network.

**Notification mechanism.** An NI notification mechanism is a mechanism through which the NI informs a process of any change in NI device status. For example, the NI can interrupt the process on a change in device status, such as arrival of a message from the network. Such explicit notification may be unnecessary if a process monitors changes in the NI status registers. Hence, the notification mechanism is optional.

To send a message to the network, a processor first reads the send interface status register to ensure there is enough space in the send interface's data registers. If there is enough space, the processor writes a new message to the data registers. If there is not enough space, the processor can either poll the NI periodically or have the NI notify it when free space becomes available. On receiving the new message in its data register the NI hands the message to the external NI, which injects the message into the network.

When a message arrives at the receiving external NI, the external NI extracts the message from the network and hands the message to the receive interface. The receive interface writes the message to its data registers and sets a status register that indicates to the processor that a message has arrived in the receive interface. Flow control (e.g., return-tosender) is typically used to ensure messages are never (or rarely) lost if the data registers are full. If the control registers have been appropriately set by the processor, the NI can send a notification to a processor in the receive host node about the arrival of this message through a processor interrupt. Finally, a processor in the receive host node reads the new message from the NI data registers.

Many recent research and commercial computers use a microprocessor instead of a hardware, finite-state machine to run message protocols. The discussion in the rest of this thesis is independent of the presence or absence of any such protocol processor. An internal NI must interact with processors and memory system internal to a node to send and receive messages. Such interaction can use all opportunities for performance improvement that I discuss in this thesis.

#### **1.2 Problems with Conventional Network Interfaces**

Conventional internal NI architectures do not efficiently support low-latency communication in a COW. Latency is the user-to-user delay for sending a message. Low latency determines the performance of applications that send small messages frequently. Frequent small messages underlie many traditional and emerging application domains, such as parallel scientific programs [32].

Fortunately, improvements in networks have reduced the impact of the network and software protocols (that generate and consume messages) on the overall latency of communication. In particular, local area network (LAN) bandwidth has improved from 10-100 megabits/second to one gigabit/second or more. Aggressive LANs, such as the Myricom Myrinet [15] or the Tandem Servernet [54], have moved so far that some view them as a new class of networks called a *system area network* or SAN [54, 8] (Appendix A). SANs improve performance in two ways. First, aggressive links and switches provide very high bandwidth and extremely low latency. Second, reliability properties of SANs allow systems to use lean communication layers (e.g., Active Messages [128]) instead of heavy-weight and one-size-fits-all protocols (e.g., TCP/IP). Consequently, SANs help improve the performance of both network hardware (links and switches) and network software (communication protocols).

Unfortunately, improvement in network and software protocols have exposed processor-NI interactions as a major bottleneck, particularly for COWs. Conventional internal NI architectures can introduce between ten and hundreds of microseconds latency to the overall communication latency. There are eight factors that can contribute to such latency:

- *Operating system intervention.* Conventional NIs are accessed by the processor via the operating system (e.g., Unix sockets). Such intervention eases protection and address translation for message buffers. Unfortunately, such intervention also introduces long latencies to the critical path of message send and receipt [5, 127]. For example, switching to the operating system from a user process can require execution of between hundreds and thousands of instructions.

- I/O bus. Conventional NIs are located on the I/O bus, and not on the higher performance memory bus. This is because I/O buses, unlike proprietary memory buses, offer standard interfaces to which third-party network vendors can manufacture their NI cards. Unfortunately, the latency and bandwidth of I/O buses are two to ten times worse than current memory buses.

- *Small message buffers in NI*. Most conventional NIs offer small amounts of buffering (e.g., few kilobytes) in their internal NIs and rely on processors to buffer messages in main memory. Unfortunately, such processor-controlled buffering can degrade proces-

sor performance by creating resource contention for processors, memory, and system buses.

- Uncached access to NI registers. Conventional NIs registers are marked uncachable

primarily because such NI designs have side-effects. For example, a load to an NI

device register both returns a value and deletes it from the device. Unfortunately,

uncached accesses are much slower than memory accesses that hit in processor caches.

- In-order and non-speculative access to NI registers. Conventional NIs do not allow

processors to access NI registers out of order and speculatively, again, because of the

presence of side-effects. For example, if a message send is initiated speculatively, then

it cannot be rolled back if the processor later decides that its speculation was incorrect.

Therefore, NIs will appear relatively slower, as processors continue to improve via

out-of-order and speculative memory accesses.

- Slow data transfer. Conventional NIs transfer data from the NI via either uncached loads/stores to memory-mapped NI registers or direct memory access (DMA). Both of these are low-performance solutions. Uncached accesses usually transfer small amounts of data (e.g., between 4 16 bytes), thereby offering low bandwidth. DMA transfers large amount of data, but require the operating system to initiate the transfer, which incurs huge latencies.

- *Application Programming Interface (API)*. Conventional NIs either directly expose the underlying data transfer primitives (e.g., programmed-controlled I/O via uncached loads/stores to memory-mapped NI registers) or require the operating system to serve as the API (e.g., Unix sockets) for message sends and receives. The first solution offers tight coupling between the processor and NI, which often blocks the processor until the access is complete. The second solution again requires slow operating system intervention. <sup>1</sup>

- *Notification via interrupts.* Conventional NIs usually notify processors of NI events via heavy-weight interrupts. Unfortunately, current microprocessors are not optimized

<sup>1.</sup> In reality, this interface is somewhere in between an Application Programming Interface (API) and an Application Binary Interface (ABI). I use API due to the lack of a better term.

for interrupts because they treat them as exception conditions. Consequently, interruptdriven messaging can significantly deteriorate communication performance.

#### **1.3 Future Trends**

Technology trends suggest that the latency to access the internal NI will become even more critical in the future. The contribution of software protocols and networks on overall communication latency will continue to reduce. Microprocessors that typically run these protocols are improving at a tremendous pace. The steady drop in feature sizes and introduction of microarchitectural techniques, such as speculative execution [83, 117], are projected to improve microprocessor performance by a factor of 80 in the next ten years [140].

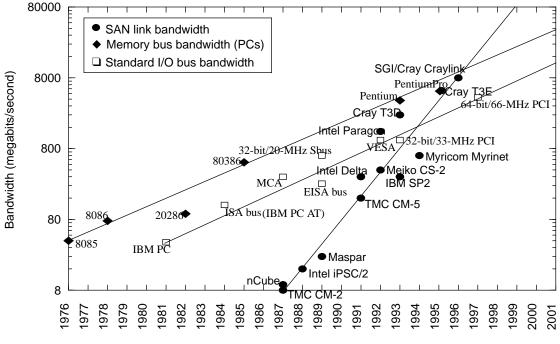

Network performance will keep pace with the improvement in processor performance. Currently, network bandwidth is improving at 100% per year (Figure 2-2), which translates into a factor 1000 improvement in the next ten years. Such massive improvement in bandwidth will make the latency of requests (carrying a few bytes) and responses (carrying multi-megabytes of data) similar. Consequently, overall communication latency will become even more critical. Fortunately, network latencies will also continue to drop in the future because of the advent of low-cost CMOS processes, novel switch architectures [6], and high-speed optical switches [95].

The explosive growth in the performance of microprocessors and networks requires innovative techniques to reduce the latency of processor-NI interactions in a COW. These techniques must also allow a seamless transition towards effectively using future technological and architectural advances. I argue that the solution to this problem is to treat processor-NI interactions like processor-memory interactions (Section 1.4). Since the gap between processor and DRAM memories is increasing [49], microprocessors will continue to invent novel techniques to bridge this gap. In a COW, treating an NI access like a memory access will allow internal NI architectures to take advantage of such future innovations.

10

#### **1.4 Thesis Contributions for Network Interfaces**

This thesis has four contributions. I discuss the first three contributions in this section. Section 1.5 discusses the fourth contribution.

The first contribution of this thesis (Chapter 2) is to show how treating a processor's access to a network interface as a regular memory access can tremendously improve processor-NI interactions in a COW. Memory is virtualized without requiring operating system intervention (in the common case), is on the memory bus, is plentiful in today's computers, does not have side-effects, and hence, can be cached and accessed out of order and speculatively, and is usually transferred in cache block units. I propose to do the same for NIs. Most of the these opportunities have been explored partially and independently by other researchers. My contribution is to organize these opportunities in a single framework that exposes commonality and synergistic interactions.

NIs that use direct memory access (DMA) offer some of these advantages because data DMA-ed into memory can be treated just like regular memory. Unfortunately, the DMA initiation itself often uses high-latency solutions, such as initiation via the operating system (for traditional DMA) or uncached loads/stores (for Princeton's User-Level DMA [11]).

Treating an NI access as a memory access can improve all eight components of latency listed in Section 1.2. Some of these eight opportunities have been partially explored by others. A principal contribution of this work is to organize these opportunities into a common framework. These eight opportunities are:

- using virtual memory hardware, and not operating system intervention, to virtualize the NI (Figure 1-2a),

- placing the NI on the higher performance memory bus, and not on the slower I/O bus,

12

- using virtual memory as a huge buffer for network messages, instead of small amounts of dedicated memory on the NI,

- caching messages in processor and NI caches, like regular cachable memory,

- allowing out-of-order accesses and speculative loads on a processor's accesses to an NI, like side-effect-free regular memory accesses,

- transferring messages between processor caches, NI cache, and main memory through cache block transfers, instead of DMA,

- designing the application programming interface (or API) to the NI as memory-based queues, and not directly exposing the underlying data movement primitives as the API, and

- notifying processor of NI events through cache invalidations, instead of heavy-weight interrupts.

The second contribution of this thesis is the design (Chapter 3) and evaluation (Chapter 4) of a new class of network interfaces called *Coherent Network Interfaces* (*CNIs*). CNIs sit on a computer's memory bus and interact with processors via cachable, coherent memory operations. The most aggressive CNI—that is,  $CNI_iQ_m$  in my nomenclature—exploits all eight opportunities for performance improvement outlined above.

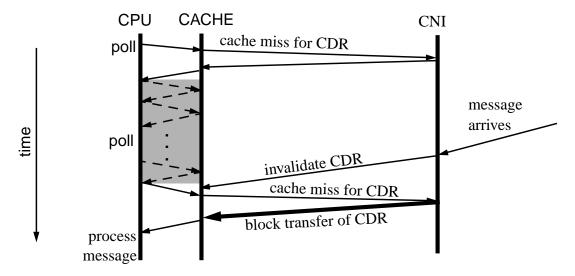

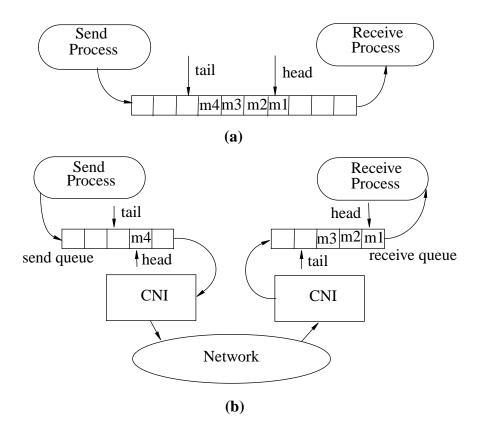

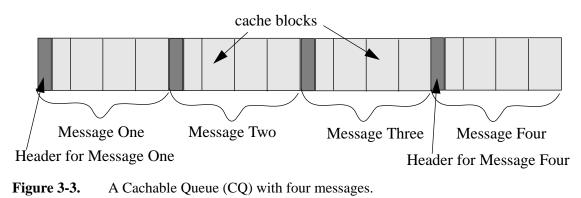

Chapter 3 develops and optimizes two mechanisms that CNIs use to communicate with processors. A *cachable device register*—derived from cachable control registers [101]—is a coherent, cachable block of memory used to transfer status, control, or data between a CNI and a processor. *Cachable queues* generalize cachable device registers from one cachable, coherent memory block to a contiguous region of cachable, coherent blocks managed as a circular queue. An important advantage of CNIs is that they allow cachable queues to be physically located in processor or CNI caches, but logically allocated in main memory, which allows plentiful buffering. Chapter 3 also explores several critical optimizations—*lazy pointer, shadow head, sense reverse, empty entry removal, intra-message prefetch, dead message elimination,* and *cache bypass*—that improves the performance of

CNIs. Finally, Chapter 3 examines different alternatives for multiprogramming a CNI that uses cachable queues.

Chapter 4 performs a detailed comparison of four CNIs with a more conventional NI that is, a Thinking Machines' CM-5 NI [124]—using a 16-node COW, two microbenchmarks, and seven parallel scientific applications. For small message sizes—between 8 and 256 bytes—CNIs improve the round-trip latency by 87-342% compared to a conventional NI on a coherent memory bus. For moderately large messages, between 8 and 4096 bytes, CNIs improved the bandwidth by 109-202%. Results with the seven applications show that CNIs can improve performance by up to 21-190% compared to a conventional NI.

The third contribution of this thesis (Chapter 5) is a systematic classification, examination, and evaluation of two of the eight opportunities—data transfer and buffering—listed above. To the best of my knowledge, this is the first work to systematically identify and explore the data transfer and the buffering parameters that underlie high-performance NIs designed for fine-grain communication. The data transfer parameters capture how messages are transferred between internal memory structures (e.g., processor caches, main memory) of a computer and a memory bus NI. The buffering parameters capture how and where an NI buffers incoming network messages. I evaluate these parameters by comparing seven memory bus NIs using the same system parameters and benchmarks as in Chapter 4. These seven NIs abstract the data transfer and buffering parameters of the NIs in TMC CM-5 [68], Fujitsu AP3000 [109], Princeton User-Level DMA [11], Digital Memory Channel [44], MIT StarT-JR [53], and two Coherent Network Interfaces (CNI<sub>512</sub>Q and CNI<sub>32</sub>Q<sub>m</sub>described in Chapter 4).

My results show that a high-performance NI in a COW should effectively use the block transfer mechanism of the memory bus, minimize processor involvement for data transfer, directly transfer messages between an NI and the processor (at least in the common case), provide plentiful buffering (possibly in main memory), and minimize processor involve-

ment to buffer incoming network messages.  $CNI_{32}Q_m$  performs the best among the seven NIs because it optimizes all five data transfer and buffering parameters.

#### **1.5 Using Prediction to Accelerate Coherence Protocols**

This part of the thesis differs significantly from the rest of the thesis. Techniques outlined in the rest of the thesis can accelerate user-to-user messaging in a parallel machine programmed with explicit message-passing. In contrast, this section examines techniques to improve the communication performance of parallel machines programmed with a shared-memory programming model.

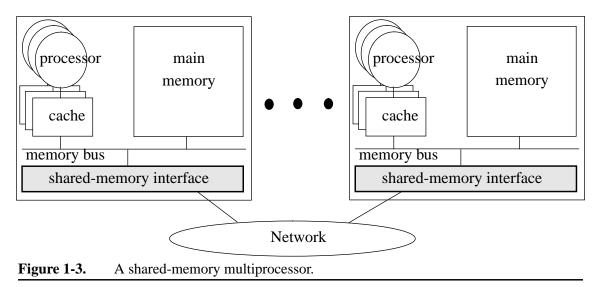

Shared memory simplifies programming multiprocessors because it provides a single address space to all processors, even when memory is physically distributed among different nodes of the machine (Figure 1-3). To reduce the disparity between latency of local and remote memory accesses, these machines cache both local and remote memory in perprocessor caches. Caches are usually made transparent to software with a cache coherence protocol implemented in a shared-memory communication interface. A coherence protocol usually exchanges *coherence messages* between shared-memory interfaces of different nodes to keep per-processor caches coherent. Unlike a message-passing communication

interface, a shared-memory interface usually generates these messages directly in hardware or firmware.

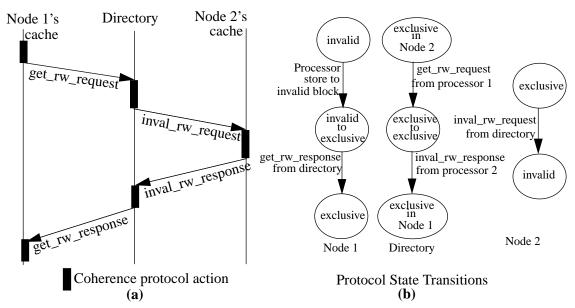

Shared-memory interfaces in most large multiprocessors use a form of coherence protocol called a directory protocol [4, 71, 66, 25, 130, 69, 2]. Directory protocols maintain a directory entry per memory block that records which processor(s) currently cache the block. On a processor cache miss for a remotely cached block, the shared-memory interface sends a coherence message over an interconnect to a directory entry, which often forwards message(s) to processor(s) currently caching the block, who then forward data or acknowledgments to the requesting processor and/or directory.

Regrettably, this cache miss and directory activity can disturb a programmer's performance model of shared memory by making some memory accesses tens to hundreds of times slower than others. Ameliorating this problem has led to many proposals, including weaker memory models [1, 43], multithreading [31, 3, 125], non-blocking caches [61, 118], and application-specific coherence protocols [93, 37]. To date, all proposals possess one or more of the following drawbacks: require a more complex programmer interface or model, retard uniprocessor performance, or require sophisticated compilers.

Another class of proposals for ameliorating memory latency is to predict future sharing patterns [9, 46] and take action to overlap coherence message activity with current work. Predictions can be made by programmers [51, 136], compilers [84, 113], or hardware. Specialized predictors in hardware include read-modify-write operation prediction in the SGI Origin protocol [66], pair-wise sharing prediction in SCI [116], dynamic self-invalidation [67], and migratory protocols [28, 120]. Existing predictors, however, are directed at specific sharing patterns known *a priori*. Furthermore, the protocol implementation is often made more complex by intertwining one or more predictors with the standard coherence protocol.

This thesis seeks a more general predictor to accelerate coherence protocols. Predictors would (logically) sit beside each standard directory and cache module to monitor coherence activity and request appropriate actions. If a directory predictor, for example, anticipates that a processor asking for a block B "shared" will next ask for block B "exclusive," the directory can answer the "shared" request with block B "exclusive."

The fourth contribution of this thesis (Chapter 6) is the design and evaluation of the *Cosmos* coherence message predictor for accelerating coherence protocols. Cosmos' design is inspired by Yeh and Patt's two-level *PAp* branch predictor [139]. Cosmos makes a prediction in two steps. First, it uses a cache block address to index into a *Message History Table* to obtain one or more sprccessor,message-type> tuples. These sprccessor,message-type> tuples correspond to sender and message type of the last few coherence messages received for that cache block. Second, it uses these sprccessor,message-type> tuples to index a *Pattern History Table* to obtain a sprccessor,message-type> prediction. Notably, Cosmos faces a greater challenge than branch predictors because the Cosmos' prediction is a multi-bit sprccessor,message-type> tuple rather than a single bit branch outcome.

My simulation results with five shared-memory applications running on a 16-node parallel machine show that variations of Cosmos predict the source and type of the next coherence message with surprisingly-high accuracies of 62-69% (*barnes*), 84-86% (*moldyn*), 84-85% (*appbt*), 74-92% (*unstructured*), and 84-93% (*dsmc*). Cosmos' high prediction accuracy results from predictable coherence message patterns or *signatures* associated with specific cache block addresses. Such signatures are generated by sharing patterns [9, 46] that do not change or change very slowly during the execution of these applications.

16

### Chapter 2

## **Treat Network Interface Access as Memory Access**

This thesis argues that NIs should be treated as "standard equipment", like memory or frame buffer, and not as peripheral add-ons. Today almost every computer is connected to a network. Consequently, every computer needs an NI. Computers connected to low-per-formance networks may not place a huge performance demand on the NI device. However, NIs for network-centric computers, such a Cluster of Workstations (COW) connected via high-performance networks, such as SANs, must be designed to deliver network performance to host user applications.

I argue that a processor access to an NI in a COW should be treated as a regular memory access, and not as a peripheral I/O operation (e.g., like a disk interface access). Since the gap between processor and DRAM access performance is increasing rapidly, microprocessors will continue to invent novel techniques to bridge this gap. Treating NI accesses as regular memory accesses will allow NI accesses to take advantage of such future innovations. Such treatment opens up at least eight opportunities to improve the performance of processor accesses to the NI [87]. These opportunities are listed in Table 2.1. An NI that supports all the eight opportunities behaves just like another processor cache in an SMP

| Problems                                                                               | Solutions                                  |                                             | Discussed   |  |

|----------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------|-------------|--|

|                                                                                        | Conventional                               | Proposed                                    | -           |  |

| Virtualize via                                                                         | operating system                           | virtual memory<br>hardware                  | Section 2.1 |  |

| Location                                                                               | I/O bus                                    | memory bus                                  | Section 2.2 |  |

| Buffer messages                                                                        | dedicated memory (in NI<br>or main memory) | virtual memory                              | Section 2.3 |  |

| Cache NI registers                                                                     | not allowed                                | allowed                                     | Section 2.4 |  |

| Out-of-order and speculative access                                                    | not allowed                                | allowed                                     | Section 2.5 |  |

| Message transfer mechanism                                                             | DMA or uncached load/<br>store             | cache block transfers                       | Section 2.6 |  |

| Application Programming Interface (API)                                                | has side-effects                           | no side-effects<br>(memory-based<br>queues) | Section 2.7 |  |

| Notification                                                                           | Interrupts                                 | cache invalidations                         | Section 2.8 |  |

| Summary: NI access similar to                                                          | disk interface access                      | memory access                               |             |  |

| <b>Table 2.1:</b> Treat NI access as memory access and not as a disk interface access. |                                            |                                             |             |  |

node. I discuss these opportunities in greater detail in a survey paper [88].

Many of the eight opportunities listed above have been explored partially by others. A principal contribution of this chapter is to organize these opportunities into a framework that exposes commonality and synergistic interactions. In particular, this thesis examines one opportunity in depth: how caching NI registers can significantly improve the performance of processor-NI interactions.

#### 2.1 Use Virtual Memory Hardware to Virtualize the Network Interface

There is a marked difference in how user processes access a peripheral I/O device (e.g., a disk) and main memory. Both of these are shared physical resources that must be virtualized across multiple user processes. Virtualizing a physical resource to a user process requires two mechanisms: protection and address translation. Protection isolates user processes from one another. Address translation allows a user process to access a physical device through virtual addresses. A peripheral I/O device is virtualized by the OS, which requires all user accesses to I/O devices be initiated through OS traps. Trapping to the OS is usually very expensive because modern microprocessors treat traps as exception conditions, rather than a common occurrence, and hence do not support them very efficiently. Main memory, on the other hand, is virtualized through the virtual memory hardware, which is supported by all high-performance microprocessors today, and does not involve OS intervention in the common case. Main memory is divided into physical pages and mapped to user virtual space on demand. A hardware structure called the Translation Lookaside Buffer rapidly translates user virtual page addresses to physical page addresses in main memory. Consequently, main memory accesses are much faster (less than a microsecond) compared to I/O device accesses (greater than 10 - 100 microseconds).

Accessing NI memory through the virtual memory hardware, and not via the OS, can therefore dramatically improve performance. The OS simply needs to map the NI memory pages directly into user space; the virtual memory hardware that already exists translates these memory-mapped virtual addresses to appropriate physical addresses in the NI memory and ensures protected access to it.

The TMC CM-5 NI and, more recently, the Myricom Myrinet host interface allow users to directly access the NI memory using this technique. I call such NIs *User-Level Network Interfaces (ULNIs)* since the NI memory can be directly accessed from user space. Compaq Corporation, Intel Corporation, and Microsoft Corporation are jointly developing such a ULNI specification called the Virtual Interface Architecture [36]. The VI architecture is a logical specification that will allow a user process to directly access the internal NI memory and thereby bypass the operating system to send and receive messages from the network.

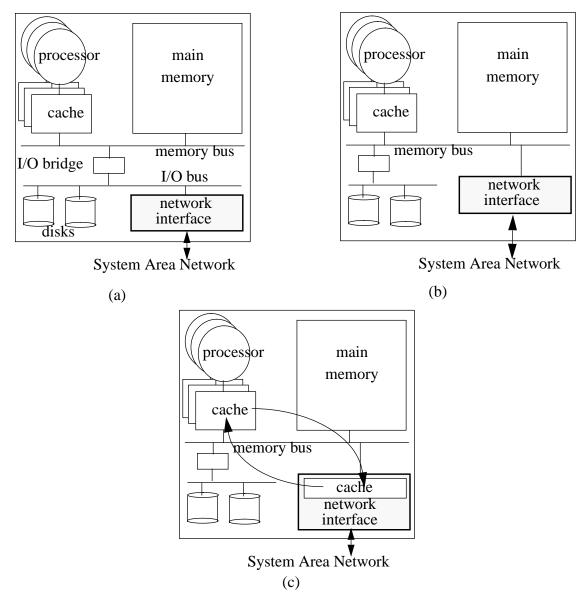

### **2.2** Place the Network Interface on the Memory Bus

In a standard workstation node (Figure 2-1a), I/O devices are typically located on the peripheral I/O bus. The choice of this location is dictated primarily by the availability of a standard I/O bus interface (e.g., SBus, PCI), which enables independent vendors to manufacture NI cards to these standard specifications. Unlike I/O buses, current memory buses

**Figure 2-1.** Workstation Nodes with Network Interfaces. (a) shows the architecture of standard workstation node with the network interface on the I/O bus. (b) shows the same workstation node with the network interface on the memory bus. (c) augments the network interface in (b) with a cache.

are usually proprietary, have non-standard interfaces because they often change across processor generations, and hence, manufacturers of I/O devices do not usually design I/O devices to memory bus specifications.

Current memory buses, however, offer three significant performance advantages over I/ O buses. First, memory buses are much faster because they are typically clocked at a higher frequency compared to I/O buses. For example, current PC memory buses are clocked between 66-75 MHz, which is more than two times faster than the current generation of 33 MHz PCI buses. Typically, all I/O bus accesses also additionally traverse the memory bus and an I/O bridge that connects proprietary memory buses to standard I/O buses.

Second, memory buses offer significantly higher bandwidth than I/O buses. Current PC memory buses offer peak bandwidths greater than 400 megabytes/second. This is more than four times greater than the peak bandwidth offered by the current generation of PCI buses. Some of the Sun Enterprise servers support an even more aggressive memory bus called the UltraGigaplane, which offers a sustained bandwidth of 2.6 gigabytes/second. Memory buses can offer such high bandwidth because these buses are 64- to 256-bits wide, which is a factor of two to eight greater than current 32-bit wide PCI bus. Additionally, today's memory buses support split transactions, which improves bandwidth because a device or a cache no longer has to lock down the memory bus during the entire duration of a transaction (e.g., cache block read from main memory).

Figure 2-2 suggests that the gap between of bandwidths of memory and I/O buses will continue to exist in future. In fact, I/O bus bandwidth lags behind memory bus bandwidth by at least five years. In other words, I/O buses will take another five years to achieve the peak bandwidth offered by today's PC memory buses. Consequently, NI cards designed to I/O buses will not be able to harness the full memory bus bandwidth. Figure 2-2 also shows that SAN link bandwidth is growing at a much faster rate than the bandwidth of PC memory buses. For such SANs we will need more aggressive memory buses, such as the SUN Ultragigaplane.

Third, memory buses support optimized single-writer coherence protocols, which allows processor caches to easily cache and share memory. This is because these single-writer

Year of Introduction

**Figure 2-2.** Trends in peak SAN link bandwidth and I/O bus bandwidth. This figure shows the crossover point between peak System Area Network (SAN) link bandwidth and "standard" I/O bus bandwidth. SAN link bandwidth has been increasing by roughly 100% per year, while the I/O bus bandwidth has been increasing by roughly 32% per year. SAN references: Cray T3E [106, 102], SGI/Cray Craylink [41, 45], Myricom Myrinet [15, 56], and the rest from Figure 7.19 (Page 591) of Hennessy and Patterson's book [49]. Memory bus references: Polsson's article on History of Microcomputers [98]. I/O bus references: 32-bit/20-MHz SBus [55], 64-bit/66-MHz PCI [77], and rest from Needham's article on PCI [94].

coherence protocols provide a single and consistent image of physical memory across all processor caches. Section 2.4 shows how and why caching message data in processor and ULNI caches can help improve performance.

The performance advantages of memory buses strongly suggest that ULNIs should be placed on memory buses, just like main memory (Figure 2-1b). My simulation results in Chapter 4 with several parallel scientific applications confirms the performance advantages of memory bus NIs over I/O bus NIs.

The only disadvantage of current memory buses is that they do not usually export a standard interface to which independent vendors can design ULNIs to. However, the advent of ULNIs as "standard equipment", like memory or frame buffers, emphasizes the need for memory bus designers to export a standard interface to either systems designers internal to a company or third-party vendors manufacturing independent ULNI devices. Companies, such as Intel, IBM, and Sun Microsystems, that manufacture both microprocessors and network-centric computers can allow system designers to design ULNIs to their internal memory bus. Intel's MPP supercomputer called Teraflop [19], for example, attaches the ULNI device directly on the PentiumPro memory bus. For independent vendors finding a standard interface on the memory bus specification.<sup>1</sup> Alternatively, manufacturers of proprietary memory buses could provide special *bridges* to other open standard interfaces, such as the PCI interface.

The bridge we need converts proprietary memory bus signals to and from another specification. A standard bridge might connect to a standard I/O bus, such as PCI. A standard bridge supports many standard devices. However, it may not provide the performance or coherence access needed by ULNIs. A more aggressive bridge could convert directly to a standard I/O bus connector that supports one demanding I/O device without a physical I/O bus. This bridge can fake the I/O bus signals to offer higher performance (e.g., no arbitration time) to standard devices. The SGI Power Challenge, for example, uses this type of bridge (which they call a "personality interface") to convert between their proprietary I/O bus and a standard SCSI device. Similarly, Intel's Accelerated Graphics Port [138] is a standard bridge that offers graphics accelerators a dedicated high-bandwidth path to main memory. An even more aggressive bridge can convert to a device-specific interface that is proprietary, but less demanding and more stable between product generations than a memory bus. If network connections become "standard equipment" like frame buffers, this option provides an attractive way to obtain nearly the network performance of a memorybus ULNI without some of the cost.

<sup>1.</sup> Corollary, Inc. obtained access to the PentiumPro memory bus to build a shared-memory system called Profusion [126].

Yet another possibility would be to standardize the interface between the internal and external NIs (Section 1.1). Microprocessor vendors can provide the internal interface that communicates with the processor and third-party vendors can provide the external interface that talks to the network. This would relieve third-party vendors from having to worry about the details of a particular memory bus' coherence protocol and allow microprocessor vendors to deliver the network's performance to a user process via its own optimized internal interface.

## 2.3 Use Virtual Memory to Buffer Network Messages

Peripheral I/O devices may require large amounts of memory. For I/O devices such as 3D Graphics Accelerators, in particular, the demand for memory is increasing steadily because high quality images and image transformations require large amounts (e.g., tens of megabytes) of primary storage. The Accelerated Graphics Port (AGP) [138] was designed to counter this demand. AGP provides graphics devices with a standardized high bandwidth path to main memory, which allows graphics devices to use main memory as a large graphics buffer. This enables low-cost graphics devices because dedicated memory can incur a prohibitive cost for graphics accelerators. Because 3D Graphics accelerators can now use portions of system memory through a graphics-specific dedicated path, these accelerators have become less peripheral in nature.

Like 3D Graphics Accelerators, high-performance ULNI devices can require large amounts, that is, tens of megabytes, of memory to buffer outgoing and incoming network messages. This is because of four reasons. First, variation in performance of loosely-coupled microprocessors and SAN switches and advent of a variety user-level communication protocols often create a temporary mismatch between the rates at which network messages are generated, transferred, and consumed. Buffering smooths out these rates and helps create a balanced system.

Second, with limited buffering and bursts of messages—a common occurrence in loosely synchronized parallel applications—a processor must constantly monitor ULNI

status changes and remove messages from the limited ULNI buffers to avoid clogging up the network. This can significantly degrade performance if the processor must continuously read an uncached status register (Section 2.8).

Third, a limited amount of ULNI buffering severely restricts the degree of multiprogramming because these ULNI buffers must be divided among different processes. Alternatively, the operating system can switch the buffers among processes; but, this can be a very expensive operation.

Fourth, SANs, such as the Myricom Myrinet, requires ULNIs to perform some form of flow-control, such as all-to-all buffer reservation or return-to-sender, to guarantee end-toend reliable message delivery. To avoid clogging the network, such flow control schemes may require large amounts of ULNI buffering.

Current commercial ULNIs, such as the Myricom Myrinet's host interface, provide only around hundreds of kilobytes of message buffers in the ULNI. This amount is not enough to support large systems with a large degree of multiprogramming. Fortunately, the Myricom Myrinet host interface provides a microprocessor that can be programmed to overcome this problem, as outlined below.

The problem of limited buffering in the ULNIs can be solved by buffering network messages in the user's virtual space [72]. This provides large amounts of buffering limited only by the size of main memory (and swap space, which backs up the user virtual space). A ULNI with this capability, however, requires additional support for protection and address translation, which may require moderate to substantial changes to commodity operating systems. The problems are similar to those faced by SMP nodes today. Just like a processor, the ULNI must have access to virtual-to-physical address translations. To reduce the cost of accessing these translations every time a message is retrieved from or deposited into main memory, a ULNI can cache these translations in a structure similar to a processor TLB. ULNIs must, therefore, be prepared to service ULNI TLB misses as well

| store X to A  | store X to A | store X to A                    |

|---------------|--------------|---------------------------------|

| load Y from B | store Y to A | store Y to B                    |

| (a)           | <b>(b)</b>   | (c) NI sends message to network |

**Figure 2-3.** Three examples of side-effects in existing NI designs. The instructions shown in this figure are uncached loads and stores to ULNI registers memory-mapped to virtual addresses A and B. (a) shows that the store-load pair must be strictly in order for some NIs to work correctly (e.g., Princeton UDMA initiation), even though the instructions appear unrelated to the processor. (b) shows two consecutive stores to the same address must occur in order (e.g., TMC CM-5 NI). (c) extends (b) to show that the second store (in the general case, the "n"th store) can trigger an action in the NI, such as sending a message into the network. (a) and (b) have the side-effects that a previous store determines implicitly the next uncached load or store a NI expects. (c) has the side-effect of sending a message on a store.

as invalidate or update the TLB entries when the OS remaps a page or swaps it out to disk. However, servicing TLB misses is a complex operation because it can result in page faults, is often processor-specific, and may require OS intervention. A ULNI can reduce this complexity by interrupting and requesting the OS running on the host processor to insert the appropriate translation in the ULNI TLB. The ULNI TLB can be augmented with protection bits and process identifiers, similar to those in a modern processor TLB, and updated along with the translations to ensure protected ULNI access to main memory. Other researchers have explored these issues in detail [133, 47, 105].

Chapter 5 evaluates the impact of alternate buffering strategies on seven parallel scientific applications.

# 2.4 Cache NI Registers in Processor and NI Caches

Unlike main memory, peripheral I/O device memory, such as ULNI memory, is typically not cached in processor caches. Instead, ULNI memory is marked uncachable. This is because of three reasons. First, processor accesses to ULNI device memory often have *side-effects* (Figure 2-3) that force all such accesses to be visible to the ULNI. Hence, all processor accesses must be uncached because cached loads or stores may not be visible outside the processor, unless there is a cache miss.

Second, a ULNI device must generate coherence signals to invalidate messages in processor caches. In this respect, it behaves more like a processor cache, rather than main memory. When a message arrives and the ULNI writes new data to the message buffers, the corresponding memory locations for the message buffers in processor caches must be invalidated. Otherwise, processors can read stale data from these buffers. Unfortunately, many ULNIs reside on standard I/O buses, which usually do not support such coherence signals. Hence, ULNIs usually do not allow processors to cache ULNI memory.<sup>1</sup>

Third, caching ULNI registers in processor caches require extra support for ULNI register reuse. Conventional ULNI device registers solve the problem of register reuse using implicit *clear-on-read* semantics, where the register is cleared after an uncached load. For example, the CM-5 NI treats the read of the hardware receive fifo as an implicit "pop" operation. Clear-on-read works because processors guarantee the atomicity of individual load instructions; that is, the value returned by the device is guaranteed to be written to a register. Clear-on-read does not work well for cached ULNI registers, since most processors do not provide the same atomicity guarantees for cache blocks. Processors guarantee the load that causes the cache miss to be atomic to ensure forward progress; however, there are no guarantees for the remaining words in the block. Before subsequent loads complete, a cache conflict (e.g., resulting from an interrupt) could replace the block. With clear-on-read semantics, the remainder of the data in the cache block would be lost for-ever.<sup>2</sup>

The first and third problems—the presence of side-effects in ULNI memory accesses and the absence of clear-on-read semantics on cache blocks—can be eliminated by designing the application programming interface carefully (Section 2.7). The second problem—keeping ULNI device memory and processor caches coherent—can be solved by

<sup>1.</sup> This is different from the standard problem of "coherent I/O." A computer with coherent I/O allows processors to cache I/O space. Here, I am interested in the inverse problem, that is, caching memory space in an I/O device.

<sup>2.</sup> This problem may not arise if only one NI register (that can be accessed via a single load or store) is allocated per cache block because individual cached loads are usually guaranteed to be atomic.

placing the ULNI device on the memory bus, so that a ULNI can directly observe and participate in the system's coherence protocol, just like a processor cache in an SMP.

Caching ULNI registers in processor caches offers two advantages. First, caching status or control registers in processor caches helps remove unnecessary memory bus traffic. For example, if a processor were polling on an uncached status register, every processor poll would go across the memory bus to the ULNI device. In the absence of any message in the ULNI, unsuccessful polls that do not find a message in the ULNI device waste precious memory bus bandwidth, which could be used by other processors in an SMP node. Instead, if the processor polls on a cached memory location, which contains the ULNI status information, all unsuccessful polls will hit in the processor's cache. When a message arrives finally and the ULNI status changes, the ULNI device invalidates the cached status register in the processor's cache. On its next poll attempt, the processor will incur a cache miss, which can be satisfied directly by the ULNI.

Second, uncached accesses provide very low bandwidth compared to cache block accesses because they transfer only a few bytes of data (e.g., 1-16 bytes). In contrast, cache blocks are typically much larger (e.g., 32-128 bytes). Hence, they can exploit the full transfer bandwidth of today's memory buses. Section 2.6 discusses these issues in detail. Table 4.5 shows that a large fraction of the memory bus bandwidth can be used effectively for processor accesses to NI registers.

Like processor caches, ULNI caches can cache ULNI registers as well. Instead of allocating ULNI registers in ULNI memory, the registers can be allocated in the user's virtual space and backed up by main memory. Section 3.6 discusses details of how such registers can be mapped, accessed, and synchronized among different application processes. Like processor caches, ULNI caches can simply cache the portion of main memory that contains the ULNI registers. Such ULNI caches help improve performance in three ways. First, processor cache misses for ULNI registers can be intercepted and satisfied directly by the ULNI cache through a direct cache-to-cache transfer. Contrast this with data transfer via DMA in which messages reach the processor cache in two steps (and, consequently two memory bus crossings): from ULNI device to main memory and from main memory to the processor cache. This increase in latency may become critical for latency-bound, request-response protocols.

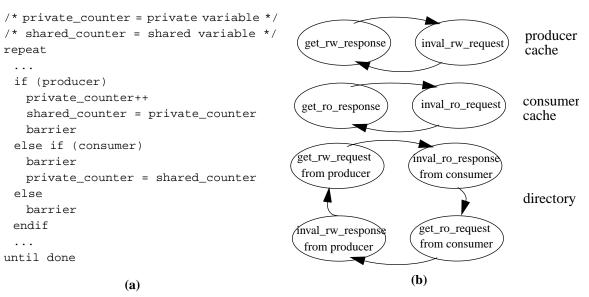

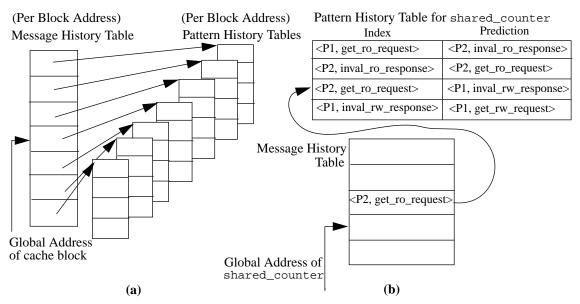

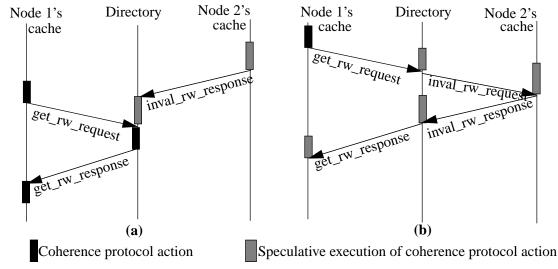

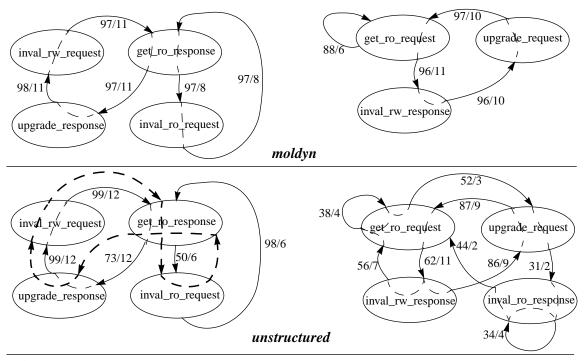

Second, when bursts of messages arrive at an ULNI, the ULNI cache may overflow; but, ULNI cache replacements to main memory will automatically buffer these messages without any processor intervention. Contrast this with register-mapped ULNIs in which processors must explicitly copy the data from the ULNI registers to the user's virtual space, which can severely degrade performance.