#### Guhan Viswanathan

Under the supervision of Associate Professor James R. Larus at the University of Wisconsin — Madison

Data-parallel programming languages provide a portable, high level abstraction to support rapid parallel program development. Data-parallel languages are widely applicable, and considerable research has been devoted to compiling them for efficient execution. Much of this work has focused on implementing a shared address space on a distributed-memory machine, particularly for programs with regular communication patterns. Compiler support for non-regular applications has been limited to iterative irregular applications, with dynamic repetitive communication patterns.

This thesis describes three new compiler, language and run-time system techniques targeting data-parallel programs with adaptive and dynamic communication patterns. These techniques have been implemented in a compiler for the language  $C^{**}$ , and include:

**Implementing conflict-free data access** C\*\*'s semantics avoid data access conflicts between parallel functions. We explore and compare two complementary implementations of conflict-free access. For parallel functions with reg-

ular data access patterns, the compiler inserts code in the program to maintain copies. When compiler data access analysis is imprecise, the compiler relies on a Loosely-Coherent Memory system to create transparent fine-grain copies.

User-defined reductions Most data-parallel languages restrict reductions, which combine values from parallel operations, to a predefined set of reduction operators. User-defined reductions extend reductions in two ways, by allowing new combining operations, and by applying reductions to user-defined data types. This thesis motivates the need for user-defined reductions, and describes the design and efficient implementation of reductions in C\*\* with only message-passing support.

Compiler-directed shared-memory communication This thesis describes how a compiler and a predictive cache-coherence protocol can implement shared-memory communication efficiently for iterative adaptive applications. The compiler uses data-flow analysis to identify points in a program where potential repetitive communication patterns exist. An incremental predictive protocol builds a communication schedule for one iteration and utilizes a schedule to pre-send data in subsequent iterations. The protocol reduces the number of remote data requests, and the total remote access latency.

by

Guhan Viswanathan

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Science)

at the

University of Wisconsin — Madison 1996

by

Guhan Viswanathan

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Science)

at the

University of Wisconsin — Madison 1996

by

Guhan Viswanathan

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Science)

at the

University of Wisconsin — Madison 1996

© Copyright by Guhan Viswanathan, 1996

All Rights Reserved

#### Abstract

Data-parallel programming languages provide a portable, high level abstraction to support rapid parallel program development. Data-parallel languages are widely applicable, and considerable research has been devoted to compiling them for efficient execution. Much of this work has focused on implementing a shared address space on a distributed-memory machine, particularly for programs with regular communication patterns. Compiler support for non-regular applications has been limited to iterative irregular applications, with dynamic repetitive communication patterns.

This thesis describes three new compiler, language and run-time system techniques targeting data-parallel programs with adaptive and dynamic communication patterns. These techniques have been implemented in a compiler for the language C\*\*, and include:

Implementing conflict-free data access C\*\*'s semantics avoid data access conflicts between parallel functions. We explore and compare two complementary implementations of conflict-free access. For parallel functions with regular data access patterns, the compiler inserts code in the program to maintain copies. When compiler data access analysis is imprecise, the compiler relies on a Loosely-Coherent Memory system to create transparent fine-grain copies.

User-defined reductions Most data-parallel languages restrict reductions, which combine values from parallel operations, to a predefined set of reduction operators. User-defined reductions extend reductions in two ways, by allowing

new combining operations, and by applying reductions to user-defined data types. This thesis motivates the need for user-defined reductions, and describes the design and efficient implementation of reductions in C\*\* with only message-passing support.

Compiler-directed shared-memory communication This thesis describes how a compiler and a predictive cache-coherence protocol can implement shared-memory communication efficiently for iterative adaptive applications. The compiler uses data-flow analysis to identify points in a program where potential repetitive communication patterns exist. An incremental predictive protocol builds a communication schedule for one iteration and utilizes a schedule to pre-send data in subsequent iterations. The protocol reduces the number of remote data requests, and the total remote access latency.

## Acknowledgments

My many years at Madison have been enriched by interactions with a bunch of wonderful people.

I have learnt a tremendous amount from my advisor, Jim Larus. Jim sets a wonderful example of how to do successful research, and I hope I have picked up some of it. I am also very grateful for his advice, and his constant support and encouragement.

I would also like to thank the other members of my committee, Mark Hill, Charles Fischer, Susan Horwitz, and Sang-tae Kim for taking the time to read the thesis and for their comments.

Much of this work would not have been possible without software developed as part the Wisconsin Wind Tunnel project. I've enjoyed interacting with many people in the group, particularly the numerous discussions with Brad, my office (and project) partner of many years, and the talks in the hall with Satish and Zhichen.

On a more personal note, I'm much indebted to my wife Vidya, both for her support, and for all the fun times together. I'd also like to thank some of my friends for enlivening those few non-working hours: Bajji, Viji and Swami, Praveen and Ranju, Madhus and Sridevi, Ranga, Guru, Bharat and Madhav.

Thanks all.

Guhan Viswanathan

University of Wisconsin — Madison September 1996

## Contents

| A              | $oxed{Abstract}$ $oxed{Acknowledgments}$ |                                               |     |  |

|----------------|------------------------------------------|-----------------------------------------------|-----|--|

| $\mathbf{A}$   |                                          |                                               |     |  |

| Li             | List of Figures                          |                                               |     |  |

| Li             | st of                                    | Tables                                        | xii |  |

| 1 Introduction |                                          |                                               |     |  |

|                | 1.1                                      | Implementing Conflict-free Data Access        | 5   |  |

|                | 1.2                                      | User-defined Reductions                       | 7   |  |

|                | 1.3                                      | Compiler-Directed Shared-Memory Communication | 8   |  |

|                | 1.4                                      | Contributions                                 | 10  |  |

|                |                                          | 1.4.1 Generality of our Techniques            | 11  |  |

|                | 1.5                                      | Thesis Structure                              | 12  |  |

| <b>2</b>       | Bac                                      | kground - Data Parallelism, C**, and Tempest  | 13  |  |

|                | 2.1                                      | Data Parallelism, Data-Parallel Languages     | 14  |  |

|                |                                          | 2.1.1 Parallelism Data Parallel Operations    | 15  |  |

|   |     | 2.1.2 The Shared Address Space                              | 17 |

|---|-----|-------------------------------------------------------------|----|

|   | 2.2 | C**                                                         | 19 |

|   |     | 2.2.1 Data Collections - Aggregates                         | 19 |

|   |     | 2.2.2 Data-Parallel Operations - Parallel Functions         | 20 |

|   |     | 2.2.3 Reductions in C**                                     | 22 |

|   | 2.3 | Tempest                                                     | 22 |

|   |     | 2.3.1 Tempest Implementations                               | 23 |

| 3 | Imp | olementing Conflict-free Data Access for Parallel Functions | 25 |

|   | 3.1 | Related Work                                                | 27 |

|   | 3.2 | Compiler Copying                                            | 28 |

|   |     | 3.2.1 No Conflicts                                          | 28 |

|   |     | 3.2.2 Single Writer, Multiple Readers                       | 29 |

|   |     | 3.2.3 Zero or One Writer                                    | 30 |

|   |     | 3.2.4 Multiple Unknown Writers                              | 31 |

|   | 3.3 | LCM                                                         | 32 |

|   | 3.4 | Performance Comparison                                      | 37 |

|   | 3.5 | Summary                                                     | 39 |

| 4 | Use | r-defined Reductions for Efficient Communication            | 40 |

|   | 4.1 | Related work                                                | 43 |

|   | 4.2 | Reductions in Data-Parallel Languages                       | 44 |

|   |     | 4.2.1 User-defined Reductions                               | 46 |

|   | 4.3 | A Motivating Example                                        | 48 |

|   |     |                                                              | vii |

|---|-----|--------------------------------------------------------------|-----|

|   |     | 4.3.1 DSMC                                                   | 49  |

|   |     | 4.3.2 Particle Movement using Parallel Prefix                | 50  |

|   |     | 4.3.3 Particle Movement using a Predefined Reduction         | 52  |

|   |     | 4.3.4 Particle Movement with User-Defined Reductions         | 52  |

|   | 4.4 | Semantics of User-Defined Reductions                         | 53  |

|   |     | 4.4.1 Data races                                             | 54  |

|   |     | 4.4.2 Reordering Combining Operations                        | 54  |

|   | 4.5 | Implementing Reductions                                      | 55  |

|   |     | 4.5.1 Basic Reductions                                       | 55  |

|   |     | 4.5.2 Bulk reductions                                        | 56  |

|   |     | 4.5.3 Local Combining                                        | 57  |

|   | 4.6 | Application Comparisons                                      | 57  |

|   |     | 4.6.1 DSMC                                                   | 59  |

|   |     | 4.6.2 Barnes                                                 | 60  |

|   |     | 4.6.3 EM3D                                                   | 61  |

|   |     | 4.6.4 Moldyn                                                 | 63  |

|   |     | 4.6.5 Discussion                                             | 65  |

|   | 4.7 | Summary                                                      | 66  |

| 5 | Cor | npiler-Directed Shared-Memory Communication for Iterative    | :   |

|   | App | olications                                                   | 68  |

|   | 5.1 | Related Work                                                 | 71  |

|   | 5.2 | A Predictive Protocol for Repetitive Communication Schedules | 73  |

|   |     | 5.2.1 The Stache Shared-Memory Protocol                      | 74  |

| $\mathbf{A}$ | C** | Bench   | nmarks                                                      | 98 |

|--------------|-----|---------|-------------------------------------------------------------|----|

| 6            | Con | clusion | n                                                           | 93 |

|              | 5.5 | Summ    | ary                                                         | 91 |

|              |     | 5.4.4   | Discussion                                                  | 90 |

|              |     | 5.4.3   | Water                                                       | 89 |

|              |     | 5.4.2   | Barnes                                                      | 87 |

|              |     | 5.4.1   | Adaptive                                                    | 85 |

|              | 5.4 | Measu   | ring the Optimizations                                      | 84 |

|              |     | 5.3.2   | Compiler Analysis to Place Directives                       | 81 |

|              |     | 5.3.1   | Parallel Function Analysis - Identifying Access Patterns    | 79 |

|              | 5.3 | Identif | ying Potentially Repetitive Patterns                        | 78 |

|              |     | 5.2.4   | Using Communication Schedules to Presend Data               | 77 |

|              |     | 5.2.3   | Building Communication Schedules in the Predictive Protocol | 76 |

|              |     | 5.2.2   | Inefficiencies in a Write-invalidate Protocol               | 75 |

# List of Figures

| 2.1 | Interleaved sequential and parallel phases in a data-parallel pro- |     |

|-----|--------------------------------------------------------------------|-----|

|     | gram's execution                                                   | 15  |

| 2.2 | Whole-array stencil operation in HPF                               | 15  |

| 2.3 | Example showing data distribution and communication (shaded el-    |     |

|     | ements) in a 4-point stencil implementation                        | 18  |

| 2.4 | MAX reduction operation in HPF                                     | 19  |

| 2.5 | Aggregate definition syntax in C**                                 | 20  |

| 2.6 | Example showing conflict-free data access semantics guaranteed by  |     |

|     | C**                                                                | 21  |

| 2.7 | Aggregate definition syntax in C**                                 | 22  |

| 3.1 | 4-point stencil                                                    | 29  |

| 3.2 | 4-point stencil with compiler-generated copying                    | 30  |

| 3.3 | Schematic representation of compiler-copying for Stencil           | 31  |

| 3.4 | 4-point threshold stencil                                          | 32  |

| 3.5 | Threshold stencil                                                  | 33  |

| 3.6 | ungtructured Parallel function with unstructured accesses          | 3/1 |

| 3.7  | Compiler-generated pseudo-code for unstructured                      | 35   |    |

|------|----------------------------------------------------------------------|------|----|

| 3.8  | Compiler-generated pseudo-code for unstructured using LCM            | 36   |    |

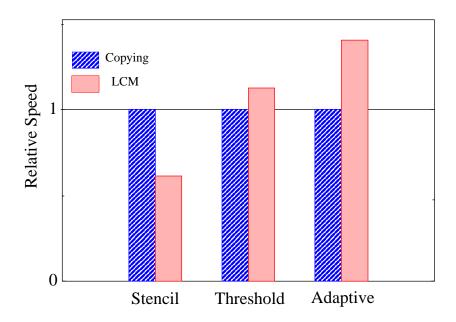

| 3.9  | Relative execution speed for compiler-copying and LCM versions       |      |    |

|      | of 3 benchmarks — Stencil, Threshold and Adaptive                    | 38   |    |

| 4.1  | Sum reduction assignment                                             | 45   |    |

| 4.2  | Minimum location user-defined reduction                              | 47   |    |

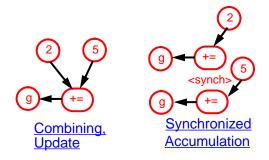

| 4.3  | Two ways of visualizing a reduction of two values to a target: Com-  |      |    |

|      | bining and Update, or Synchronized Accumulation                      | 48   |    |

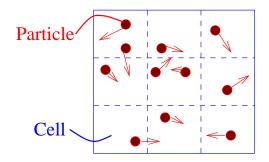

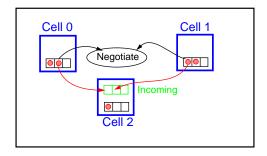

| 4.4  | Schematic of the DSMC application                                    | 49   |    |

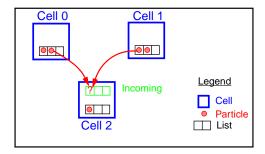

| 4.5  | Schematic of DSMC data structures and the problem of synchro-        |      |    |

|      | nized addition                                                       | 50   |    |

| 4.6  | Schematic of DSMC synchronization with parallel prefix               | 51   |    |

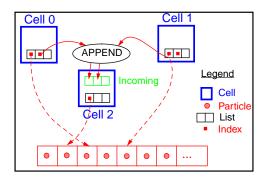

| 4.7  | Schematic of DSMC synchronization with APPEND                        | 52   |    |

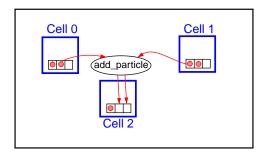

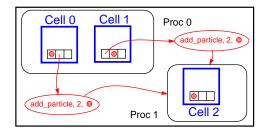

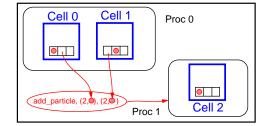

| 4.8  | Schematic of particle movement with user-defined reduction add_part: | icle | 53 |

| 4.9  | Schematic representation of basic reductions (left) and bulk com-    |      |    |

|      | munication (right) for DSMC                                          | 56   |    |

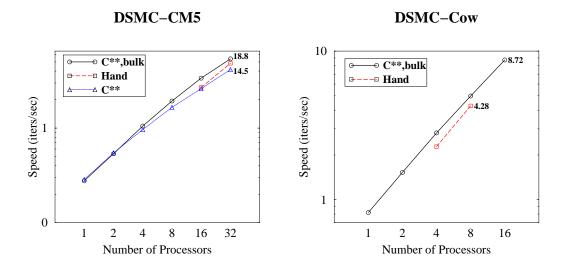

| 4.10 | Log-log scale graphs showing execution speeds of 2 or more versions  |      |    |

|      | of DSMC on the CM-5 and COW. Numbers adjoining the curves            |      |    |

|      | are speedups relative to a sequential version                        | 59   |    |

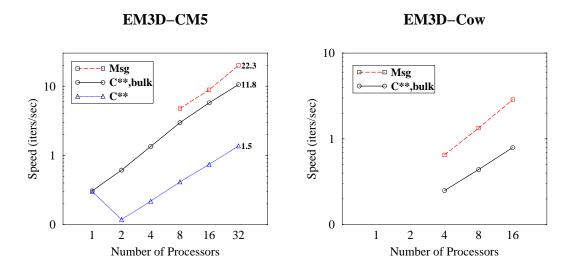

| 4.11 | Log-log scale graphs showing execution speeds of 2 or more versions  |      |    |

|      | of EM3D on the CM-5 and COW. Numbers adjoining the curves            |      |    |

|      | are speedups relative to a sequential version                        | 62   |    |

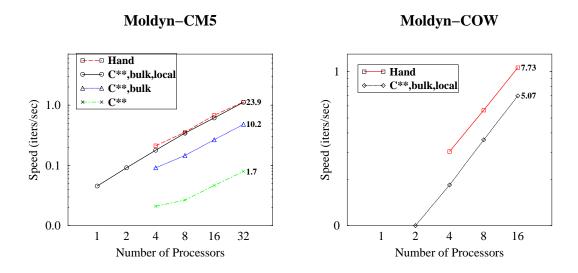

| 4.12 | Log-log scale graphs showing execution speeds of 2 or more ver-        |    |

|------|------------------------------------------------------------------------|----|

|      | sions of Moldyn's force computation phase on the CM-5 and COW.         |    |

|      | Numbers adjoining the curves are speedups relative to a sequential     |    |

|      | version.                                                               | 64 |

| 5.1  | Unstructured mesh update in C**                                        | 80 |

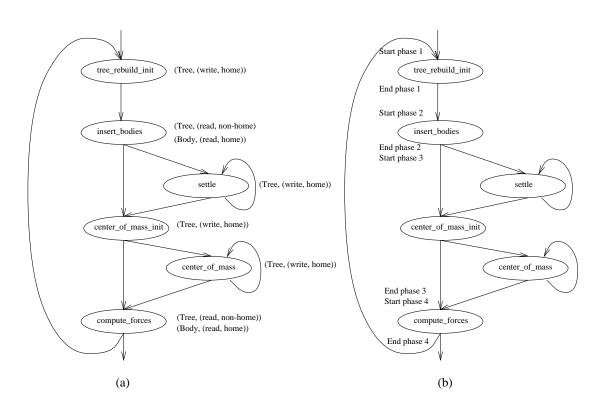

| 5.2  | Control flow graph for the main sequential loop in Barnes-Hut.         |    |

|      | CFG (a) is annotated with parallel function access patterns. CFG       |    |

|      | (b) is annotated with runtime phase directives for the predictive      |    |

|      | protocol                                                               | 82 |

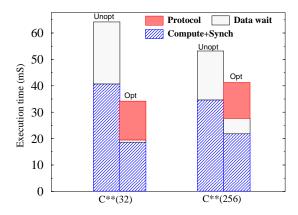

| 5.3  | Execution time for 4 C** versions of <b>Adaptive</b> — C** versions    |    |

|      | with and without optimized communication at 2 different cache          |    |

|      | block sizes. Numbers in parentheses indicate cache block sizes         | 86 |

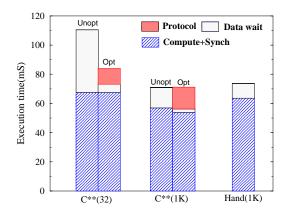

| 5.4  | Execution time for 5 versions of <b>Barnes</b> — C** versions with and |    |

|      | without optimized communication at 2 different cache block sizes,      |    |

|      | and hand-optimized SPMD. Numbers in parentheses indicate cache         |    |

|      | block sizes                                                            | 88 |

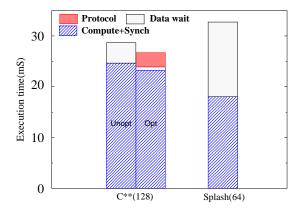

| 5.5  | Execution time for 3 versions of Water — C** with and without          |    |

|      | optimized communication, and shared-memory Splash. Numbers             |    |

|      | in parentheses indicate cache block sizes                              | 89 |

## List of Tables

| 4.1 | Comparing three approaches to particle movement                   | 53 |

|-----|-------------------------------------------------------------------|----|

| 4.2 | High-level application description and data sets. The larger data |    |

|     | sets are for COW runs                                             | 58 |

| 5.1 | Benchmark applications                                            | 85 |

| A 1 | A list of benchmarks in C**                                       | 99 |

## Chapter 1

## Introduction

Parallel computers exploit the processing power of multiple CPUs connected by a network to reduce the time it takes to execute a program. As CPU processing speeds reach their limit, parallel processing will provide an increasingly important and scalable way to utilize available processing power. Additionally, parallel computers can run applications with larger data sets than are possible on uniprocessors. Parallel processing now encompasses a wide range of platforms varying in cost and performance from multiprocessors to networks of workstations. Unfortunately, rapid advances in hardware technology have left parallel software behind. Writing programs for parallel computers is widely acknowledged to be a much more difficult task than writing sequential programs. For example, the programmer must keep track of multiple asynchronous threads of control that interact in a non-deterministic fashion.

Improved parallel programming languages reduce the difficulty of programming parallel computers by making parallel programs easy to specify, less error prone, and less machine specific. One promising approach is data-parallel languages, such as HPF [19], C\* [41], or NESL [7], which provide a portable, high level abstraction to support rapid parallel program development. These languages implement the data-parallel programming paradigm, which expresses parallelism through simultaneous operations on large sets of data [21]. Synchronization is implicit in the division of a program into sequential and data-parallel phases. In addition, a global name space of variables relieves a programmer of the burden of distributing data and managing communication. The data-parallel programming model is widely applicable — in a survey of 84 scientific applications, Fox [16] found that 85% of those programs could be expressed easily using this model — "the source of parallelism is essentially always domain decomposition or data parallelism".

The popularity of the data-parallel programming model has led to the development of a large number of data-parallel programming languages, including High Performance Fortran (HPF) [25], Fortran 90 [1], NESL [7] and pC++ [32]. In addition to language development, considerable research has been devoted to compiling high-level data-parallel programs for efficient execution, and in particular the problem of transforming shared address space operations into communication primitives of a distributed-memory machine. Much of this work has focused on regular programs, which exhibit regular patterns of communication, i.e., static communication patterns that can be identified at compile time using static compiler analysis techniques [3, 22, 40].

Compiler support for non-regular data-parallel applications on distributed-

memory machines has been limited to iterative irregular applications that fit the Inspector-Executor model. These applications specify unpredictable communication patterns that cannot be analyzed at compile time, but the patterns, once built, remain unchanged over a number of iterations. For each loop, the compiler generates an inspector phase in the loop header, which builds a communication schedule. The loop contains the executor phase, which uses the schedule to transfer data required in the iteration efficiently with messages, followed by the loop's original computation [12, 24, 46]. Since the pattern varies infrequently, the overhead of the inspector is amortized over multiple executor phases. The Inspector-Executor paradigm works well for mostly-static communication patterns, but does not extend to dynamic communication patterns.

This thesis presents three new compiler, language and run-time system techniques that enable efficient execution of a larger class of data-parallel programs, specifically, programs with dynamic adaptive communication patterns. These techniques are:

- 1. Compiler and memory-system support to enforce conflict-free data access

- 2. User-defined reductions for efficient communication, and

- 3. Compiler-directed shared-memory communication for iterative applications

A novel feature of techniques 1 and 3 is that they rely on and exploit the flexibility of user-level control over shared-memory coherence policies in a cache-coherent distributed shared-memory (DSM) system, which implements a shared-address space on distributed-memory hardware using a combination of hardware and software

techniques [29, 38]. User-defined reductions (technique 2) and compiler-directed shared-memory communication (technique 3) both optimize communication in dynamic data-parallel applications, but target distinct communication patterns, and their effect is cumulative. User-defined reductions optimize many-to-one communication with combining, whereas compiler-directed shared-memory communication optimizes one-to-many producer-consumer or migratory sharing patterns.

User-customizable DSMs enable a compiler and run-time system to tailor coherence policies to applications, both to implement higher-level functionality and to improve performance [39]. A number of such systems exist (e.g., Tempest [38], FLASH [29], TreadMarks [4], and Sequent's STiNG [34]), and they are becoming more popular. Some other compiling approaches also target flexible DSMs [8, 22], but focus on efficient DSM support for regular applications.

This thesis demonstrates that our techniques are effective. Using a suite of popular benchmark applications consisting of irregular and adaptive applications, we show that programs written in a high-level data-parallel language can be compiled to execute as fast as equivalent hand-optimized code on the CM-5, a distributed-memory multiprocessor. Our benchmark suite does not include regular applications, although the communication optimization techniques also apply to those applications. Furthermore, these three techniques focus on only two facets of data-parallel program compilation for irregular and dynamic programs, i.e., conflict-free data access and efficient communication. This thesis does not tackle other important problems, such as automatic load balancing or efficient data distributions.

We implemented these techniques in a compiler for the language C\*\* [31] that targets the Tempest interface. C\*\* is a data-parallel language that provides high-level language features like a global name space and parallelism through simultaneous operations on data. C\*\* provides coarse-grain parallelism in the form of user-defined parallel operations. Tempest [38] is a programming interface for a distributed-memory multiprocessor that provides the mechanisms to implement fine-grain cache-coherent shared memory in addition to message-passing primitives. Tempest combines good features of both message passing and shared memory; a compiler can use the fine-grain shared memory mechanisms to implement a global name space, and use custom coherence protocols or low-level communication facilities to optimize known communication patterns [28].

### 1.1 Implementing Conflict-free Data Access

The first technique targets the implementation of conflict-free data access in C\*\*'s parallel operations [30]. C\*\* supports coarse-grain user-defined parallel functions (Section 2.2) and a global name space of variables, which together give rise to the possibility of data access conflicts or data races. A data race occurs when two distinct parallel tasks access a single global data item, and one of the accesses is a write (Section 2.2.2). Data races are problematic because different temporal access orderings could generate different results, causing errors that are extremely difficult to reproduce and to correct.

C\*\* clearly defines the semantics of conflicting memory accesses to avoid dataaccess conflicts. When a data-parallel operation modifies a global data item, it receives a private copy of that data item, which is not visible to other data-parallel operations. When all operations complete, the private copies are merged into the global state. Lack of conflicts translates into nearly-deterministic execution, which is a desirable feature of some data-parallel programming languages. We explore two ways in which a compiler and run-time system can use copy-on-write to implement the high-level semantics of C\*\*. For parallel functions with regular data-access patterns that a compiler can analyze, the compiler inserts code in the program to maintain copies. For functions with accesses that a compiler cannot identify precisely (e.g., accesses through pointers), compiler-copying results in excessive and potentially expensive run-time checks. Instead, the compiler relies on a Loosely-Coherent Memory (LCM) system to create transparent fine-grain copies. LCM is driven by runtime compiler directives (e.g., to identify modified global data items) and uses a custom cache coherence protocol to create copies of cache blocks at the same global address. The LCM protocol provides controlled inconsistency of global data items during parallel execution, which matches the semantic requirements of C\*\*.

Using performance data from three variants of mesh relaxation codes, we show that these two techniques complement one another. Compiler-copying is efficient when compiler data access analysis is precise, and LCM works well when the analysis is imprecise. The benefit of providing two alternatives is that a compiler can choose the efficient alternative based on the precision of its data access analysis, and even use both in a program.

#### 1.2 User-defined Reductions

The second part of the thesis describes the design and implementation of user-defined reductions. Data-parallel languages typically allow reductions to combine values from independent parallel operations (Section 2.1.2). Reductions are extremely common in parallel applications, and can be implemented efficiently in parallel. However, most data-parallel languages restrict reductions to a predefined set of reduction operators, typically arithmetic operations on basic types. We demonstrate that parallel languages need not and should not arbitrarily limit reductions in this way. User-defined reductions extend reductions in two dimensions. First, they allow new operations to combine values, such as building a list from colliding values. Second, they allow reductions to apply to user-defined data types.

This thesis demonstrates the advantages of user-defined reductions, focusing on the benefits of extending reductions to user-defined data types. To motivate user-defined reductions, we describe and compare three real-life data-parallel implementations of inter-cell particle movement in a particle-in-cell code. The first method, which uses a parallel prefix operation, is both cumbersome to specify and inefficient in practice. The second method, which uses a predefined APPEND reduction, works well, but is not flexible, and does not directly specify a producer-consumer pattern. The third method, user-defined reductions, allows the programmer to intuitively specify particle movement, and leads to an efficient implementation.

We also present a simple implementation of user-defined reductions in C\*\*

to show that they can be implemented efficiently with message-passing support. The basic implementation uses messages to transfer reduction data, and two well-known optimizations, message vectorization and local combining, can be applied to improve reduction performance. We compared the execution time of four C\*\* applications (with reductions) against equivalent hand-optimized versions. On a 32-node CM-5 and a 16-node Cluster of Workstations (COW), both versions were comparable on 3 out of 4 benchmarks, all of which had dynamic communication patterns. On the fourth benchmark, which exhibited a repetitive static communication, the message-passing hand-optimized version was considerably faster. C\*\*'s reduction implementation does not optimize static reduction patterns, using, for example the Inspector-Executor compiling approach.

# 1.3 Compiler-Directed Shared-Memory Communication

The third technique describes how a data-parallel language compiler and a custom cache-coherence protocol can implement shared-memory communication efficiently for applications with unpredictable but repetitive communication patterns. This technique applies to a large class of scientific applications that are iterative—each iteration simulates the evolution of a physical system over time. For example, in static mesh calculations, nearest-neighbor communication is repeated in each iteration. In some irregular problems, such as molecular dynamics codes [46], communication changes infrequently, perhaps once every 20-30 iterations. In

adaptive problems, communication changes frequently, but incremental changes between iterations are small. For example, structured adaptive meshes gradually add mesh nodes for greater accuracy in each iteration [27], and gravitational N-body problems represent bodies in a quad-tree, which undergoes small structural changes between iterations.

This section shows that a compiler for a data-parallel language can cooperate with a predictive cache-coherence protocol in a distributed shared-memory (DSM) system to optimize shared-memory communication for applications with dynamic, but repetitive communication patterns. The compiler uses data-flow analysis to identify points in the program where *potential* repetitive communication patterns exist. A predictive protocol in the runtime system augments the default shared-memory protocol to build a communication schedule for one iteration and utilize a schedule to pre-send data to satisfy data requests in following iterations. As a result, the predictive protocol reduces the number of shared-memory data requests that cannot be satisfied locally, and the total remote memory access latency.

Compiler-directed shared-memory communication uses a combination of two techniques — a predictive cache coherence protocol, and simple compiler analysis — for optimizing shared-memory communication. The predictive protocol builds dynamic incremental communication schedules — new requests not satisfied by the pre-send phase are added to the schedule for subsequent iterations. This approach has the advantage that it can be applied to adaptive applications with repetitive dynamic communication patterns that a compiler cannot analyze. Simple compiler analysis automatically applies the predictive protocol for applications with

repetitive producer-consumer sharing patterns for which a sequentially-consistent memory coherence protocol would incur large overheads [9]. By contrast, compilers targeting message-passing machines must identify and fully analyze run-time communication patterns in applications. Our simple analysis only identifies program points at which potentially repetitive communication takes place, but need not identify the patterns themselves.

We measured the benefits of compiler-directed shared-memory communication by comparing the execution time of optimized and non-optimized versions of three applications (Adaptive, Water, and Barnes) on a 32-processor CM-5. In all cases, the optimized version had significantly less remote latency. For Adaptive and Water, the optimized version was faster than the best non-optimized version. For Barnes, which shows excellent spatial locality, the optimized and non-optimized versions are comparable.

### 1.4 Contributions

The important contribution of this thesis is to show that, for a larger class of scientific applications that includes irregular and dynamic applications, programs written in a high-level data-parallel language can be compiled to run as efficiently as hand-optimized code on distributed-memory multiprocessors. Ideally, we would have liked to compare the performance of data-parallel programs against equivalent message-passing versions, which typically demonstrate the best performance. However, message-passing versions are extremely difficult to develop, and we settled for the best parallel version of each application that was available to us.

Towards this goal, we present three new techniques for compiling data-parallel programs, including compiler-copying and LCM to prevent data-access conflicts, user-defined reductions for efficient communication and compiler-directed shared-memory communication for iterative applications. We describe each technique in detail, and demonstrate that they produce executable programs that run as efficiently as equivalent hand-tuned codes.

We also show that these techniques apply to a wider class of applications, i.e., those with irregular and dynamic communication patterns, than have been previously considered. For example, our suite of benchmarks includes adaptive structured mesh codes and a data-parallel implementation of the Barnes-Hut algorithm, a dynamic hierarchical gravitational N-body code (Table A.1).

#### 1.4.1 Generality of our Techniques

Although we have developed these techniques in the context of C\*\* and Tempest, they should readily extend to other data-parallel languages and DSM platforms.

All the compiler techniques developed in this thesis are also applicable to other data-parallel languages with coarse-grain data parallelism, including popular languages such as HPF [25]. Compiler copying for conflict-free data access (Chapter 3) is already required in a limited form for array assignment statements by the HPF standard. The upcoming HPF-2 standard is considering allowing user-defined reductions in HPF's coarse-grain DO INDEPENDENT loops [14]. Since C\*\*'s parallel functions and HPF's coarse-grain DO INDEPENDENT loops provide very similar functionality, our reduction implementation (Chapter 4) should di-

rectly extend to supporting HPF programs. Finally, compiler analysis for optimized shared-memory communication (Chapter 5) is designed for languages with coarse-grain data parallelism.

Two of the techniques presented in this thesis (LCM and the predictive protocol), rely on the ability to customize cache-coherence protocols in a DSM system. Many recent DSM systems provide this flexibility, although to varying degrees. Tempest and TreadMarks provide maximum flexibility by implementing all coherence actions in user-level software. By contrast, FLASH and STiNG use programmable engines to implement protocol actions, allowing the moderate level of protocol customization that is required by our techniques.

#### 1.5 Thesis Structure

This thesis contains six chapters. Chapter 2 introduces background material explaining the data-parallel model, C\*\*, and Tempest. Chapter 3 explores and contrasts two possible implementations of conflict-free data access. Chapter 4 describes the implementation and performance of user-defined reductions in C\*\*. In Chapter 5, we show how a data-parallel language compiler can cooperate with a custom protocol to implement shared-memory communication efficiently for iterative parallel applications. Chapter 6 concludes the thesis.

## Chapter 2

## Background - Data Parallelism,

## C\*\*, and Tempest

This thesis presents three new techniques for compiling data-parallel programs for efficient execution. To understand these techniques, it is necessary to understand the context in which they apply, in particular, the language input to the compiler, and the target machine. In this section, we describe these two interfaces for the compiler that we developed as part of this thesis. The compiler takes as input programs written in the data-parallel language C\*\* and generates executable programs targeting the Tempest parallel programming interface on distributed-memory multiprocessors.

This section describes C\*\* and Tempest in some detail, specifically from a language implementor's point of view. It begins with a brief description of the dataparallel programming model and data-parallel programming language features, both to fit C\*\* in the larger data-parallel context, and to show that although we have developed these techniques in the context of C\*\*, they also apply to other popular data-parallel programming languages.

## 2.1 Data Parallelism, Data-Parallel Languages

The distinguishing feature of the data-parallel programming model is in how a programmer specifies parallelism: a data-parallel program is organized around simultaneous operations on collections of data, in contrast to control-parallel programming's view of tasks, communication and synchronization [21]. In this model, the programmer builds a (typically large) data collection and invokes a single parallel operation on the collection — the compiler and run-time system ensure that the operation is replicated and applied in parallel on all elements of the collection.

The data-parallel programming model is popular because it provides a common abstraction underlying a large number of scientific applications [16]. As a result, a number of programming languages are based on the data-parallel model (Connection Machine Lisp [49], parts of HPF [19], ZPL [33], etc). In addition to support for data collections and data-parallel operations, data-parallel languages offer other high-level abstractions (e.g., a global name space) and potentially deterministic execution to support rapid high-level parallel program development.

This section outlines salient features of the data-parallel programming model and data-parallel programming languages. More detailed descriptions can be found elsewhere [17].

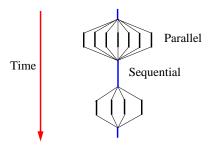

Figure 2.1: Interleaved sequential and parallel phases in a data-parallel program's execution

A(1:N,1:N) = (A(0:N-1,1:N)+A(2:N+1,1:N)+A(1:N,0:N-1)+A(1:N,2:N+1))/4.

Figure 2.2: Whole-array stencil operation in HPF

#### 2.1.1 Parallelism - Data-Parallel Operations

A data-parallel program explicitly specifies parallel execution by invoking a data-parallel operation on a data collection. Invoking a data-parallel operation creates multiple operation invocations, one for each element of the collection. The parallel operation completes only when all individual invocations complete, clearly dividing a program's execution into distinct sequential and parallel phases (Figure 2.1). Whole-array operations in HPF provide a good example of data-parallel operations. For example, the 4-point stencil in Figure 2.2 extends the primitive addition operator to apply elementwise on array data aggregates. An analogous 4-point stencil in C\*\* is outlined in Figure 2.2.2.

Data-parallel operations provide high-level abstractions for parallel processing. Parallelism and synchronization are implicit in the execution of a data-parallel operation, and the language provides no other primitives for synchronization (such as locks or mutual exclusion) that are commonly available in the Single Program Multiple Data (SPMD) style of programming.

Data-parallel operations in data-parallel languages can be broadly characterized as fine-grain or coarse-grain, depending on the maximum granularity of each parallel operation (i.e., the amount of work that can be done between synchronization points). Fine-grain data-parallel operations originally evolved from SIMD machines, such as the Connection Machine CM-2 [20], which execute individual instructions in lockstep on multiple processing units. Fine-grain data-parallel operations directly reflect this execution model in a data-parallel operation's semantics, limiting a data-parallel operation's granularity to a primitive language operation (e.g., addition, assignment). Fine-grain data-parallel operations inherit both the advantages and disadvantages of the hardware model. The model offers the simplicity of a single thread of execution and the absence of data races, but suffers from the inefficiencies of conditional statements and from the synchronization necessary to execute fine-grain operations on MIMD processors.

By contrast, coarse-grain parallel operations allow arbitrary user-defined code to execute as part of a parallel operation between synchronization points. HPF's DO INDEPENDENT loops [19] and pC++'s parallel member functions [32] are good examples of coarse-grain parallel operations. Coarse-grain parallel operations map easily to MIMD execution, but asynchronous execution in a global address space allows data races, which lead to errors that are difficult to reproduce and therefore extremely difficult to debug.

Finally, the distinction between fine-grain and coarse-grain operations is meaningless for purely functional data-parallel languages, such as NESL [7], which do not allow imperative updates to global variables.

Implementing Parallel Functions When a data-parallel operation is invoked, the compiler and run-time system are responsible for replicating the operation and applying it in parallel on each element of the data collection. On a multiprocessor machine, this task can be divided into two parts, both of which are conceptually simple. First, the total work for the parallel operation is partitioned among the processors, usually following the data distribution for the data collection. Second, each processor executes a loop iterating the data-parallel operation over all elements of the data collection that it owns.

#### 2.1.2 The Shared Address Space

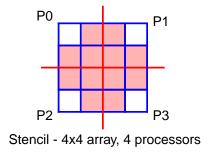

Data-parallel languages provide a global name space of variables and data-parallel programs specify communication through read and write accesses to variables in this name space, just as shared-memory parallel programs do. For example, for a 4-point stencil operation on a 4x4 array distributed blockwise among 4 processors, all interior elements of the array must be communicated between neighboring processors (Figure 2.3).

**Implementation Considerations** On a distributed-memory multiprocessor, the compiler and run-time system must implement a shared-address space, i.e. they must implement a global name space by distributing data among processors,

Figure 2.3: Example showing data distribution and communication (shaded elements) in a 4-point stencil implementation

and translate implicit communication through global variable access into explicit communication directives. Our implementation relies on a distributed shared-memory (DSM) machine, which transparently implements a shared address space, but may not do so efficiently. Efficient communication is vital to achieving good parallel application performance, and Chapters 4 and 5 explore techniques to implement implicit communication efficiently on DSMs.

#### Reductions

Communication in a shared-address space only suffices for one-to-one or one-to-many communication. Many-to-one communication causes data conflicts or collisions, when multiple values are stored in a location. Data-parallel languages typically use binary reduction operators to combine colliding values into a single value that can be stored in a location. Reductions are extremely common in parallel applications, even those written in languages that do not provide first-class support for these operations. For example, the MAX reduction shown in Figure 2.4 captures the maximum value in 2-dimensional array A in variable max.

### max = MAXVAL(A, 2)

Figure 2.4: MAX reduction operation in HPF

Most data-parallel languages restrict reduction operators to a limited set of predefined reduction functions — typically, the associative arithmetic and logical operations.

We explore the implementation of reductions in more detail in Chapter 4.

### 2.2 C\*\*

C\*\* is a data-parallel programming language based on C++ [31]. It includes a number of desirable features of data-parallel programming languages — data collections (called Aggregates), data-parallel operations (called parallel functions), a global name space of variables, and sophisticated reduction operations. This section introduces examples to briefly illustrate the syntax and semantics of C\*\* programs.

### 2.2.1 Data Collections - Aggregates

Data collections in C\*\* are called Aggregates, and form the basis for parallelism. An Aggregate declaration, which uses different syntax from class and array declarations in C++, specifies an ordered collection of values, much like a multidimensional array of objects, that can be operated on by a data-parallel operation. For example, Figure 2.5 declares a two-dimensional collection of floating point values.

The size of an Aggregate may be specified in the Aggregate declaration, or at runtime when an Aggregate object is created.

### 2.2.2 Data-Parallel Operations - Parallel Functions

C\*\* provides coarse-grain data-parallel operations called parallel functions. A parallel function is identified by the keyword parallel, and includes a parallel argument, which indicates the Aggregate object to which the parallel function is applied. Figure 2.2.2 specifies a stencil computation on the Grid Aggregate. Since the data-parallel function is replicated and applied on all elements of the two-dimensional grid, the pseudo variables #0 and #1 identify row and column positions for the grid element allotted to an invocation of the parallel function.

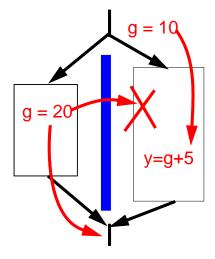

Figure 2.6: Example showing conflict-free data access semantics guaranteed by  $C^{**}$

### C\*\*'s Parallel Function Semantics

C\*\* allows coarse-grain parallel functions, but clearly defines the semantics of conflicting memory access to avoid non-deterministic data races. C\*\* specifies that all parallel function invocations start from the same global state, and incur no conflicts. When an invocation updates a global value, the new value is visible only to that invocation until the data-parallel operation completes (Figure 2.6). At that point, all changes are merged into a single consistent global state. In the stencil parallel function (Figure 2.2.2), C\*\*'s semantics specify that each point in the stencil averages old values of neighboring points, because a neighbor's changes are not visible until the operation itself completes.

```

void max_grid(parallel Grid A) parallel

{

max =%> A[#0][#1];

}

```

Figure 2.7: Aggregate definition syntax in C\*\*

# 2.2.3 Reductions in C\*\*

C\*\*, like other imperative data-parallel languages, provides reduction assignments to combine colliding values. For example, Figure 2.7 assigns the maximum of a two-dimensional grid A to variable max. Reductions use slightly different syntax from other assignments, and also have slightly different semantics. In C\*\*, the result of a reduction is available at the target of the assignment only when all data-parallel operations complete. In other words, C\*\* does not make intermediate reduction results visible to the programmer. This design choice is explored in more detail in Section 4.2.

# 2.3 Tempest

Tempest is a parallel programming substrate that provides a common programming interface across a range of distributed-memory multiprocessors [38]. A key feature of Tempest is that it provides the mechanisms to implement fine-grain user-level distributed shared memory (DSM) on top of a message-passing machine, in addition to message-passing primitives. Support for shared-memory mechanisms

on distributed memory multiprocessors is becoming increasingly popular [29].

A distributed shared-memory system implements transparent access to a shared address space which is distributed among individual processors' local memories. The system identifies all accesses to remote shared data items, and includes a memory coherence protocol that obtains and caches local copies of remote data items to allow the computation to continue.

Tempest provides a DSM interface with two additions. First, sharing in Tempest is fine-grain, with sizes between 32 and 128 bytes. Fine-grain sharing reduces false sharing, and smaller block sizes improve performance for some applications (Section 5.4). Second, and perhaps more important, Tempest allows user-level control of memory coherence protocols, i.e., it allows memory coherence actions (which obtain and release copies of remote shared data) to be implemented by the user, or in our case, by the compiler. The default memory coherence protocol in Tempest, called Stache, implements sequentially-consistent transparent shared memory using a write-invalidate protocol. One of the techniques presented in this thesis (Chapter 5) exploits user-level control over coherence protocols to augment Stache to improve performance for iterative parallel applications.

# 2.3.1 Tempest Implementations

Tempest is designed to be a portable parallel programming substrate. Currently, two implementations of Tempest exist, both named Blizzard, one for the Thinking Machines CM-5 [45], and one for a Cluster Of Workstations (COW) connected by an off-the-shelf Myrinet network [44].

Blizzard-CM5 implements the Tempest interface on the distributed-memory CM-5, using error correcting codes in memory to implement fine-grain access control [45]. The CM-5 uses 33 MHz Sparc processors connected by a custom network, which is optimized for small messages. Satisfying a remote shared-memory access for a 32-byte cache block on the CM-5 takes approximately 200 microseconds, including protocol handler time and network round-trip time.

Blizzard-COW implements Tempest on a Cluster of Workstations (COW) connected by a Myrinet [44]. Each COW node is a dual-processor SPARCStation 20, which includes two 66 MHz ROSS HyperSPARC chips, a Myrinet interface chip, and a T0 hardware add-on board to implement fine-grain access control. Round-trip network latencies for small messages on the Myrinet are on the order of 50 microseconds, and the remote shared-memory access latency for small cache blocks (64 bytes) takes approximately 77 microseconds.

# Chapter 3

# Implementing Conflict-free Data Access for Parallel Functions

C\*\* provides a number of high-level data-parallel programming language features, including a global name space and coarse-grain data-parallel functions. The interaction between these two features — unsynchronized data access in a shared address space and multiple asynchronous threads of execution — allows the possibility of data access conflicts, which are an undesirable feature of parallel program execution <sup>1</sup>.

Data access conflicts, or data races, arise when two distinct threads of execution (or, in our case, two distinct data-parallel operations) access a single global datum, and at least one of the accesses is a write access which updates the da-

<sup>&</sup>lt;sup>1</sup>This thesis does not consider synchronization races, which arise from different temporal orderings of synchronization events, since data-parallel languages do not allow explicit synchronization

tum. In a program with data access conflicts, different temporal orderings of the conflicting accesses during different runs of the program can generate different results. Data races often lead to program errors that are extremely difficult to find, primarily because the errors can only be reproduced if the same temporal access ordering is maintained across different program runs.

Unlike most other data-parallel languages that provide few mechanisms to address data access conflicts, C\*\* defines a clear semantics for conflicting data accesses in data-parallel operations. C\*\*'s semantics mandate that multiple parallel function invocations (Section 2.2.2) appear to execute instantaneously and simultaneously, so that global accesses cannot conflict. All invocations start from the global state in effect at the beginning of the parallel operation. When an invocation updates a global data item, the change is visible only to that invocation until all data-parallel operations complete. At that point, all changes are merged into the global state. In effect, each parallel function invocation receives its own copy of any modified global data items, and all copies are reconciled when the data-parallel operation completes. For example, in the 4-point stencil in Figure 2.2.2, each stencil invocation only sees old values of neighboring elements.

High-level parallel language features like conflict-free data access in C\*\* are very useful, but are unlikely to be widely used unless they can be implemented efficiently. In this chapter, we explore two different ways of implementing conflict-free data access using two variants of a copy-on-write scheme with reconciliation. Section 3.2 describes how a compiler can analyze a program to identify conflicting data items and insert code to create and reconcile copies. Compiler copying

works well for programs that a compiler can analyze, but could be expensive for dynamic programs for which compiler analysis is imprecise and may lead to unnecessary copying. In that case, Section 3.3 shows how a compiler can rely on a Loosely-Coherent Memory (LCM) system to implement fine-grain copy-on-write with reconciliation. Section 3.4 compares these two approaches and their performance on four mesh relaxation codes and shows that they complement one another. Compiler copying is more efficient for programs that permit precise analysis, and LCM incurs less overhead for programs where data access analysis is imprecise. The compiler can choose either technique to implement conflict-free data access depending on the precision of its analysis, and even use both techniques in a program. Section 3.1 compares our approaches with related work, and Section 3.5 summarizes the chapter.

# 3.1 Related Work

Data-parallel languages handle data races in a variety of ways. Fine-grain data-parallel languages, such as C\*, use a SIMD execution model to avoid read-write conflicts, and provide combining operations for write-write conflicts. Hatcher et al. [18] have looked at ways to compile fine-grain languages for MIMD machines by increasing the grain of parallelism. By contrast, C\*\* directly allows large-grain parallelism, but specifies a clear semantics for conflicting operations. Functional data-parallel languages, such as NESL [7] do not allow side effects, and avoid the problem entirely. Whole-array operations in HPF [19] require all input operands to be read before any output is written, providing semantics similar to C\*\* for

a restricted subset of the language, and are usually implemented with compiler-implemented copying. Finally, some coarse-grain parallel languages, such as Parallel Lisp [42] or HPF's DO INDEPENDENT loops [19] require the programmer to specify conflict-free parallel operations and leave the semantics undefined if conflicts occur.

The Myrias machine implemented a copy-and-reconcile operation similar to the one in LCM [5]. However, copying and reconciliation were implemented in hardware at the page granularity, and followed a fixed coherence policy. Munin [6], like LCM, allows the programmer or compiler to adapt coherence policies to data structures in an application. Unlike LCM, Munin only provides a fixed set of policies, each tailored for a specific pattern.

# 3.2 Compiler Copying

In many simple parallel applications, a compiler can precisely identify all global data accesses within a data-parallel program, and insert extra code to make copies of global values on updates if necessary. A number of compiler-copying alternatives exist depending on the precision of compiler data access analysis, and the number of distinct invocations that read or write each global data item.

### 3.2.1 No Conflicts

The simplest case occurs when the data-parallel function invocations are independent and each invocation updates a distinct portion of the global space. In other

Figure 3.1: 4-point stencil

words, no invocation attempts to read values that are possibly updated by other invocations. In this case, no action from the compiler is necessary to maintain conflict-free access.

# 3.2.2 Single Writer, Multiple Readers

Consider the 4-point stencil in Figure 3.1 that updates each interior point in a 2-dimensional grid with the average of its four neighboring points. Each grid point is updated by only one invocation, and read by four invocations operating on neighboring grid points.

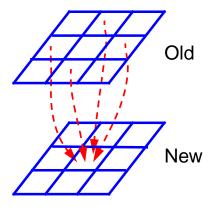

Figure 3.2 lists a simplified version of the compiler-generated SPMD code for the stencil function. To maintain conflict-free data access the compiler maintains two copies of the grid, satisfying all read accesses from the old copy and updating values in the new copy (schematically described in Figure 3.3). The reconciliation phase, which is invoked by the compiler after the parallel phase, copies values

Figure 3.2: 4-point stencil with compiler-generated copying

from the new copy into the old copy.

If the compiler can also guarantee that *all* points in the Grid are updated, the reconciliation can be accomplished with a simple pointer swap between A and new\_A.

### 3.2.3 Zero or One Writer

If only some fraction of all points in the grid is updated (e.g., in the threshold stencil in Figure 3.4), the compiler must keep track of the updated points for reconciliation (e.g., using a bit-vector), or conservatively propagate points that do not satisfy the threshold value to the new copy (Figure 3.5). The conservative

Figure 3.3: Schematic representation of compiler-copying for Stencil copy can then be optimized using the pointer swap trick of Section 3.2.2.

## 3.2.4 Multiple Unknown Writers

If the compiler cannot analyze data accesses within parallel functions precisely, it must create copies for individual data items (rather than entire arrays), and include run-time checks to access the correct copy within a parallel function using a technique similar to run-time resolution [40]. Figure 3.6 shows a parallel function with unstructured accesses (i.e., through indirection arrays). In function unstructured (Figure 3.6), the compiler must conservatively assume that the two accesses to A through indirection arrays may map to the same location.

Figure 3.7 describes how a compiler can maintain per-invocation copies for a parallel function with unstructured accesses. The compiler creates and maintains a mapping of copies using support routines for allocation, lookup and unmapping. The allocation routine, alloc\_and\_map, creates a new copy of a global data item and updates it. The lookup routines, is\_mapped and lookup\_map, determine

Figure 3.4: 4-point threshold stencil

whether a particular location is mapped and return its value respectively. The unmap routine, unmap, removes mappings for per-invocation copies in preparation for starting a new invocation. The reconciliation phase identifies all created copies (using function lookup\_alloced) and merges them into the global state.

# 3.3 LCM

Loosely-Coherent Memory (LCM) exploits program level control of memory coherence protocols (Section 2.3) to implement fine-grain copy-on-write and reconciliation to help implement C\*\*'s language semantics [30]. LCM relies on directives from the C\*\* compiler to detect the need to copy shared data, and, at runtime, creates transparent per-invocation copies at the cache block granularity that share

```

void threshold_stencil_SPMD (Grid new_A, Grid A)

{

for all points (#0, #1) assigned to me do

{

if (diff(A[#0][#1], A[#0-1][#1], A[#0+1][#1],

A[\#0][\#1-1], A[\#0][\#1+1]) > THRESHOLD)

{

new_A[#0][#1] = (A[#0-1][#1] + A[#0+1][#1] +

A[#0][#1-1] + A[#0][#1+1]) / 4.0;

}

else

new_A[#0][#1] = A[#0][#1];

}

barrier();

/* Before reconciliation phase */

for all points (#0, #1) assigned to me do

A[\#0][\#1] = new_A[\#0][\#1];

}

```

Figure 3.5: Threshold stencil

```

void unstructured (parallel Grid A, int ind[][]) parallel

{

A[ind[#0]][ind[#1]] = f(A[#0][#1]);

if (A[ind[#0+1]][ind[#1 -1]] > THRESHOLD)

{

...;

}

}

```

Figure 3.6: unstructured - Parallel function with unstructured accesses the global address of the original data item. LCM was developed by Brad Richards and is described in detail in his thesis [39].

LCM provides the compiler with three directives. The first, mark\_modification, marks a global data item that will potentially be modified and needs to be copied. When the directive is executed, it causes LCM to create a per-invocation copy of the global data item at the same global address. The second directive, flush\_copies removes per-invocation copies before starting a new invocation. The final directive, reconcile\_copies, implements a synchronized global reconciliation phase and merges all changes into the global state. Figure 3.8 shows how a compiler would use LCM directives to implement conflict-free data access for the unstructured parallel function described in Figure 3.6.

LCM transparently creates a per-invocation copy at the same address as the

```

void unstructured (Grid A, int ind[][])

{

int tmp;

for all points(#0, #1) assigned to me do {

alloc_and_map_float(&A[ind[#0]][ind[#1]]) = f(A[#0][#1]);

/* Personal copy or old value? */

if is_mapped(ind[#0+1], ind[#1-1])

tmp = lookup_map(&A[ind[#0+1]][ind[#1-1]])

else

tmp = A[ind[#0+1]][ind[#1 -1]];

if (tmp > THRESHOLD) { ...; }

unmap(&A[ind[#0]][ind[#1]]);

}

barrier();

/* Before reconciliation phase */

for all points (i, j) in A do {

if (alloced(i, j))

A[i][j] = lookup_alloc(&A[i][j]);

}

}

```

Figure 3.7: Compiler-generated pseudo-code for unstructured

```

void unstructured (Grid A, int ind[][])

{

for all points(#0, #1) assigned to me do

{

mark_modification(&A[ind[#0]][ind[#1]]);

A[ind[#0]][ind[#1]] = f(A[#0][#1]);

if (A[ind[#0+1]][ind[#1-1]] > THRESHOLD)

{

...;

}

flush_copies();

}

reconcile_copies();

}

```

Figure 3.8: Compiler-generated pseudo-code for unstructured using LCM

original data item. As a result, the compiler can refer to global variables directly, and need not insert run-time checks to differentiate per-invocation copies from the global state. It offers greater benefits for programs with dynamic behavior by removing potentially expensive run-time checks [43].

# 3.4 Performance Comparison

We compared the performance of compiler copying and LCM with three mesh relaxation programs written in C\*\* with varying degrees of dynamic behavior. Stencil performs an iterative, regular 4-point stencil for 50 iterations on a 1024x1024 mesh (Figure 3.1). Threshold performs a similar 4-point stencil computation for 50 iterations over a 512x512 mesh, but does not modify all mesh elements in each item (Figure 3.4). It modifies only points whose values has changed by more than a threshold. Adaptive is also a stencil computation over a structured mesh, but the mesh evolves over time to capture finer detail at points in the mesh where the gradient is steep. Adaptive uses dynamically allocated quad trees at mesh points to simulate subdivision of space for greater accuracy. In Adaptive, as in Stencil, all interior points in the mesh are updated in each iteration.

Figure 3.9 displays and compares the relative execution speed of compiler-copying and LCM versions of Stencil, Threshold and Adaptive. The copying versions use two copies of the entire data set, and use a pointer swap to switch between new and old versions (Section 3.2.3). Copying versions were generated automatically by the compiler for Stencil and Threshold, and by hand for Adaptive. All programs were run on a 32-processor CM-5, using the Blizzard-E version of

Figure 3.9: Relative execution speed for compiler-copying and LCM versions of 3 benchmarks — Stencil, Threshold and Adaptive

Blizzard-CM5 [45]. The compiler-copying versions used Blizzard's default Stache memory coherence protocol [38].

Stencil is a good example of a regular program on which precise compiler data access analysis is possible. In this case, LCM provides no benefit; the copying version is 1.5x faster than the LCM version. Compiler-copying is more conservative for Threshold than for Stencil and copies some data items unnecessarily (Section 3.2.3). LCM only creates copies of data items that are actually modified and improves the execution speed by a factor of 1.18x. LCM improves performance significantly over copying for Adaptive, which includes data accesses through pointers and dynamically allocated data for which compiler analysis is imprecise. Adaptive-LCM is faster than Adaptive-copying by a factor of 1.36x.

# 3.5 Summary

This chapter presented two different techniques, compiler-implemented copying and LCM, that implement C\*\*'s semantics of conflict-free data access, with the aim of avoiding data races which lead to hard-to-find errors in parallel programs. Both techniques implement C\*\*'s semantics using variants of copy-on-write schemes with reconciliation.

Compiler-implemented copying inserts code in the program to create and maintain explicit copies of global data items. For regular programs with data access patterns that a compiler can analyze, compiler copying provides an efficient alternative to implement conflict-free data access. LCM, on the other hand, relies on compiler directives to detect the need to copy shared data, and creates copies that share the same global address as the original item. LCM implements conflict-free access more efficiently for programs with dynamic data access behavior by removing the necessity for run-time checks to distinguish between copies.

LCM and compiler-copying complement one another, thus enabling the C\*\* compiler to use the best of both worlds. The compiler can generate copying code in parts of the program where its data access analysis is precise, and rely on LCM to maintain C\*\*'s semantics efficiently in other parts of the program that include dynamic behavior.

# Chapter 4

# User-defined Reductions for Efficient Communication

Communication in imperative data-parallel languages occurs through read or write operations in the shared address space. Although convenient and portable, communication in a shared address space only suffices for one-to-one or one-to-many communication. Many-to-one communication causes write-write conflicts or collisions, when multiple values are stored in a location. Data-parallel languages typically use binary reduction operators to combine colliding values into a single value that can be stored in a location. Reductions, which specify both communication and combining, are extremely common in parallel applications, even those written in languages that do not provide first-class support for these operations. Unfortunately, most data-parallel languages limit reductions to a small set of predefined reduction functions — typically, the associative arithmetic and logical operations.

The topic of this paper is user-defined reductions, which are a natural generalization of reductions in data-parallel languages. User-defined reductions extend reductions in two important ways. First, they allow new ways to combine values that may not have been anticipated by a language designer. For example, user-defined reductions can implement the tournament or location reduction [17, 25], or build a list from colliding values (e.g., sendToQueue [23]) without additional language support. Second, user-defined reductions allow a programmer to specify reductions on user-defined data types.

This paper demonstrates the advantages of user-defined reductions in a dataparallel language, focusing on the benefits, both to the programmer and to the

compiler, of extending reductions to user-defined data types. The programmer

benefits from being able to specify combining operations directly on structured

data types. By contrast, predefined reductions require the programmer to specify combining in three steps — map structured data types to primitive types,

combine primitive types, map results back to structured data types — (e.g., see

Section 4.3.3). We compare three ways in which data-parallel programmers typically specify particle movement in a particle-in-cell code, including parallel prefix

operations, predefined list-building reductions and user-defined reductions. In

comparison to the other two methods, user-defined reductions offer the benefits of

a simple, intuitive specification of direct producer-consumer particle movement.

Moreover, with simple support from the run-time system, a compiler can translate

reduction operations into direct producer-consumer data transfers on structured

data types that can be implemented efficiently using bulk messages on a message-

passing machine.

This paper also presents a simple implementation of user-defined reductions in the coarse-grain data-parallel language C\*\*, although the results should directly apply to other languages such as HPF [25] or pC++ [32]. Our reductions implementation relies on message-passing support, and applies traditional message-passing optimizations to reduce overhead. We analyze the performance of user-defined reductions by comparing the execution time of two versions each of four benchmark applications (Table 4.2), one in a data-parallel language with user-defined reductions and the other SPMD code optimized with application-specific communication for the reduction pattern on two hardware platforms, a 32-processor CM-5 and a 16-node Cluster of Workstations (COW) connected by an off-the-shelf network. For applications with dynamic communication patterns, the C\*\* versions were faster by up to 25%. For applications with mostly static communication patterns, the C\*\* version was up to 2.6x slower than the SPMD version.

User-defined reductions also allow the programmer to specify new reduction operations. The obvious benefit of this extension, which we do not explore in this chapter, lies in allowing powerful combining operations, such as the location reduction [25], or to build a list or tree with multiple values. A drawback of user-defined reductions is that they allow arbitrary user-defined code to execute in a reduction operator, which allows the possibility of non-deterministic results either due to data races, or due to reordered execution of non-commutative operations. Section 4.4 explores these language design problems in more detail, and proposes

solutions to some of them.

This chapter is organized as follows. Section 4.2 briefly describes communication and reductions in C\*\*, and shows how they can be extended to user-defined reductions. Section 4.3 uses the example of a particle-in-cell code to contrast three different specifications of particle movement in a data-parallel language, including parallel prefix operations, predefined list-building reductions and user-defined reductions. Section 4.4 explores the consequences of extending reductions with user-defined operators in a data-parallel language. Section 4.5 describes C\*\*'s reduction implementation. Section 4.6 describes our benchmarks and presents detailed performance results. Section 4.1 covers related work and Section 4.7 summarizes the chapter.

### 4.1 Related work

Many previous papers have recognized the need for powerful reduction operators. For example, Dataparallel C adds a tournament operator [17] to locate the position of the maximum value in a list of elements. In comparing the message-passing and data-parallel paradigms, Klaiber et al. [23] proposed the sendToQueue operator to remedy the inefficiency of expressing a list-building reduction in C\*. Sharma et al. [46] proposed a similar APPEND operator for DSMC, a particle-in-cell application. User-defined reductions subsume these specialized reduction operations under a common framework, and do not require compiler or run-time system changes to implement these operators.

Mukherjee et al. [35] noted that reductions form the dominant communica-

tion pattern in many irregular applications. However, they used a variety of application-specific protocols and implemented custom protocols for each application to improve communication performance. The C\*\* system uniformly handles reduction patterns by implementing them using vectorized messages and is able to run several of their applications as efficiently as the hand-tuned code.

Several applications in the HPF-2 motivating applications suite [14] note their requirement for user-defined reductions. In addition, some languages allow user-defined functions for reduction operations (e.g., Connection Machine Lisp [49], Paralation Lisp [42], and Fortran D [15]). However, we are unaware of papers describing implementations of user-defined reductions on parallel machines.

# 4.2 Reductions in Data-Parallel Languages

Recall from Section 2.1.2 that reductions augment assignment statements in a parallel operation with a combining or reduction operator. When the reduction assignment executes, the statement's combining operator combines colliding values and updates the left-hand-side with the result. For example, Figure 4.1 uses a reduction assignment to sum the values of a Grid object.

### Reduction Result Availability

In coarse-grain data-parallel languages, a task may continue after executing a reduction assignment. The language must specify the value of a reduction target (e.g., g in parallel function sum in Figure 4.1) between the reduction assignment and the end of the parallel function. Three approaches are possible:

```

float g;

void sum(parallel Grid &A) parallel

{

g = %+ A[#0][#1];

...;

}

```

Figure 4.1: Sum reduction assignment

- 1. The language may prohibit accesses to g, except as a reduction target, as does Fortran D [15]. Erroneous accesses can be identified syntactically. This approach allows the runtime system to defer updating the target. However, syntactic analysis may not identify all erroneous accesses, particularly those involving arrays or pointers.

- 2. The language may retain the old value of g after a reduction. When the dataparallel operation completes, the colliding values can be combined and used to update reduction targets. We call this approach **deferred reductions**.