# **Complexity-Effective Superscalar Processors**

by

Subbarao Palacharla

## A dissertation submitted in partial fulfillment of

the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

### UNIVERSITY OF WISCONSIN—MADISON

1998

### Abstract

The performance trade-off between hardware complexity and clock speed in the design of superscalar microarchitectures is first investigated. Using the results of this trade-off analysis, the thesis proposes and evaluates two new superscalar microarchitectures designed with the goal of achieving high performance by reducing complexity.

This thesis takes a step towards quantifying the complexity of superscalar microarchitectures. First, a generic superscalar pipeline is defined. Then the specific areas of register renaming, instruction window wakeup, instruction window selection, register file access, and operand bypassing are analyzed. Each is modeled and Spice simulated for three different feature sizes representing past, present, and future technologies. Performance results and complexity trends are expressed in terms of issue width and window size. Results show that instruction window logic and operand bypass logic are likely to be the most critical in the future.

Following the complexity analysis, we study a family of superscalar microarchitectures called the dependence-based microarchitectures. These microarchitectures exploit natural dependences occurring in programs to reduce the complexity of window logic and operand bypass logic. Simulation results show that dependence-based superscalar microarchitectures are capable of extracting similar levels of parallelism as a conventional microarchitecture while facilitating a faster clock.

Finally, we propose and evaluate the integer-decoupled microarchitecture that improves the performance of integer programs by minimally adding to a conventional microarchitecture. Floating-point units in the conventional microarchitecture are augmented to perform simple integer operations and the resulting floating-point subsystem is used to ii

support some of the computation in integer programs. Simulation results are presented that show modest speedups for a 4-way processor. The speedups are attractive, however, considering that the proposed microarchitecture requires little additional hardware.

### Acknowledgments

First and foremost, I thank my parents and family for encouragement and support during the seemingly endless stay in graduate school. I thank my dad for nudging me towards graduate school and research.

I am indebted to Jim Smith, my advisor, for taking me as his student at a crucial juncture in my graduate school career. I thank him for providing direction and for sharing his ideas. Most of all, I enjoyed his style of "loosely-coupled" advising. I also thank him for gladly answering my questions during countless walk-in meetings.

I also owe a lot to Norm Jouppi for helping me technically with the core of this dissertation. He patiently answered my questions, some stupid ones too, about VLSI circuits. I enjoyed many informative discussions about circuits and computer architecture with him. His advice and help made this thesis possible.

I am especially grateful to Guri Sohi for providing me with an office and computing facilities in Computer Sciences. I thank him for serving as a reader and for his critical comments on the thesis.

I thank David Wood, Jim Goodman, and Charles Kime for serving on my committee. I would like to especially thank David Wood for serving as a reader while on sabbatical and for making numerous useful comments that greatly improved the presentation of the thesis.

Over the past six years, I have had the privilege of technically interacting with Jim Goodman, Mark Hill, Rick Kessler, Norm Jouppi, Jim Smith, Guri Sohi, and David Wood. I thank them for teaching me most of what I know about computer architecture.

This dissertation has benefited from the work of other graduate students. Subramanya Sastry implemented the compiler support for a part of the dissertation research. Todd Austin developed the toolset on which the simulators used in this dissertation are based on. Alain Kägi always made time for helping me with Framemaker. I thank all of them.

I thank Scott Breach, Douglas Burger, Satish Chandra, Babak Falsafi, Alain Kägi, and T. N. Vijaykumar and for their friendship and company. Their camaraderie made life enjoyable and helped insulate me from occasional low points in life. Special thanks to Satish for the innumerable trips to State Street. Thanks to Amir Roth for fun discussions about anything and everything during the last year of my graduate studies. Outside of work, I thank Ambuj Shatdal, Francis Valiyaveetil, and Jignesh Patel for their company.

Finally, I would like to thank the agencies that funded my graduate studies. My work was supported in part by Wisconsin Alumni Research Foundation, NSF grants MIP-9505853, University of Wisconsin Graduate School, the U.S. Army Intelligence Center and Fort Huachuca under contract DABT63-95-C-0127 and ARPA order no. D346, Cray Research Inc., and Digital Equipment Corporation - Western Research Laboratory.

# Abstract ......i List of Figures ......ix 2.4 Complexity Analysis ...... 24

# Table of Contents

| 2.4.1.4 Model Results                                         | 38 |

|---------------------------------------------------------------|----|

| 2.4.2 Window Wakeup Logic                                     | 38 |

| 2.4.2.1 Structure                                             | 39 |

| 2.4.2.2 Delay Analysis                                        | 40 |

| 2.4.2.3 Spice Results                                         | 46 |

| 2.4.2.4 Model Results                                         | 49 |

| 2.4.3 Window Selection Logic                                  | 49 |

| 2.4.3.1 Structure                                             | 50 |

| 2.4.3.2 Delay Analysis                                        | 52 |

| 2.4.3.3 Spice Results                                         | 56 |

| 2.4.3.4 Model Results                                         | 57 |

| 2.4.4 Register file Logic                                     | 57 |

| 2.4.4.1 Structure                                             | 58 |

| 2.4.4.2 Delay Analysis                                        | 58 |

| 2.4.4.3 Spice Results                                         | 63 |

| 2.4.4.4 Model Results                                         | 65 |

| 2.4.5 Data bypass logic                                       | 66 |

| 2.4.5.1 Structure                                             | 67 |

| 2.4.5.2 Delay Analysis                                        | 68 |

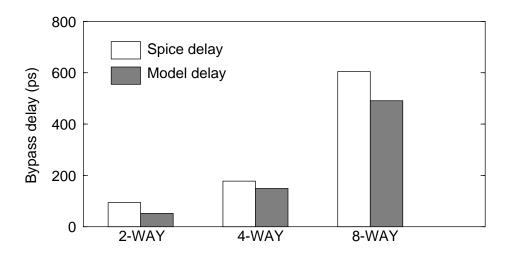

| 2.4.5.3 Spice Results                                         | 71 |

| 2.4.5.4 Model Results                                         | 73 |

| 2.4.5.5 Alternative Layouts                                   | 73 |

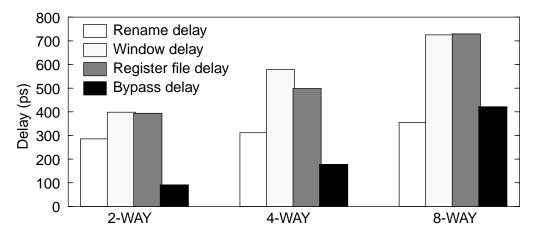

| 2.5 Pipelining Issues and Overall Delay Results               | 74 |

| 2.6 Related Work                                              | 82 |

| 2.7 Chapter Summary                                           | 83 |

| Chapter 3. Dependence-based Superscalar Microarchitectures    | 85 |

| 3.1 Concept                                                   | 86 |

| 3.2 Dependence-based Microarchitectures : An Example          | 89 |

| 3.2.1 Performance of the Fifo-based Microarchitecture         | 92 |

| 3.2.2 Complexity Analysis of the Fifo-based Microarchitecture | 94 |

| 3.2.3 Clustering the Fifo-based Microarchitecture             | 96 |

| vii                                                                             |

|---------------------------------------------------------------------------------|

| 3.2.4 Overall Performance of the Clustered Fifo-based Microarchitecture 97      |

| 3.2.5 Effect of Scaling Instruction and Data Cache Miss Latency                 |

| 3.3 Other Dependence-based Microarchitectures                                   |

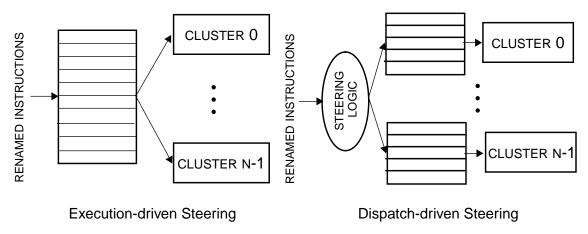

| 3.3.1 Single Window, Multiple Execution Clusters, Execution-driven Steering 100 |

| 3.3.2 Multiple windows, Dispatch-driven Steering                                |

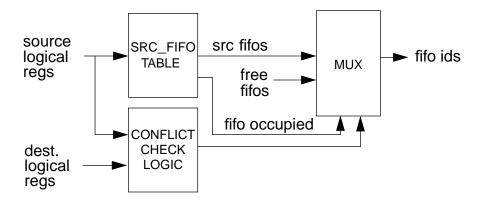

| 3.3.3 Complexity of Steering Policies                                           |

| 3.4 Experimental Evaluation 105                                                 |

| 3.4.1 Performance Relative to an Ideal Superscalar 107                          |

| 3.4.2 Effect of Increasing Number of Clusters                                   |

| 3.4.3 Effect of Increasing Inter-cluster Latency 110                            |

| 3.4.4 Inter-cluster Bypass Frequency 111                                        |

| 3.4.5 Comparing against In-order Distributed Reservation Stations 112           |

| 3.5 Related Work 113                                                            |

| 3.6 Chapter Summary 116                                                         |

| Chapter 4. Integer-Decoupled Microarchitecture 119                              |

| 4.1 Concept                                                                     |

| 4.2 Changes to the Conventional Microarchitecture                               |

| 4.3 Partitioning the Program 123                                                |

| 4.4 Basic Partitioning Scheme                                                   |

| 4.4.1 Terminology and Data Structures                                           |

| 4.4.2 Partitioning Conditions 128                                               |

| 4.4.3 Partitioning Algorithm 129                                                |

| 4.5 Advanced Partitioning Schemes                                               |

| 4.5.1 Limitations of the Basic Partitioning Scheme                              |

| 4.5.2 Cost Model                                                                |

| 4.5.3 Algorithm for Introducing Copies and Duplicating Code 134                 |

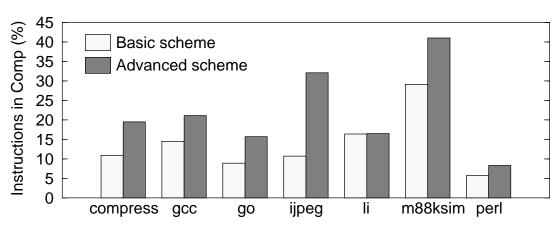

| 4.6 Experimental Evaluation 135                                                 |

| 4.6.1 Evaluation Methodology 135                                                |

| 4.6.2 Performance Results 137                                                   |

| 4.7 Related Work                                                                |

| 4.8 Chapter Summary 143                                                         |

| Chapter 5. Conclusions 145                                             |

|------------------------------------------------------------------------|

| 5.1 Thesis Summary 145                                                 |

| 5.2 Future directions 148                                              |

| 5.2.1 Quantifying the Complexity of Superscalar Microarchitectures 148 |

| 5.2.2 Dependence-based Superscalar Microarchitectures                  |

| 5.2.3 Integer-decoupled Microarchitecture                              |

| References                                                             |

| Appendix A                                                             |

| A.2 Delay Results                                                      |

| Appendix B                                                             |

| B.2 Window Wakeup Logic 171                                            |

| B.3 Window Selection Logic 174                                         |

| B.4 Register File Logic 174                                            |

| B.5 Data Bypass Logic 176                                              |

# List of Figures

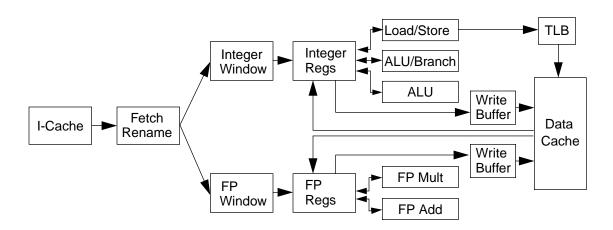

| Figure 1-1. A typical superscalar microarchitecture    2                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

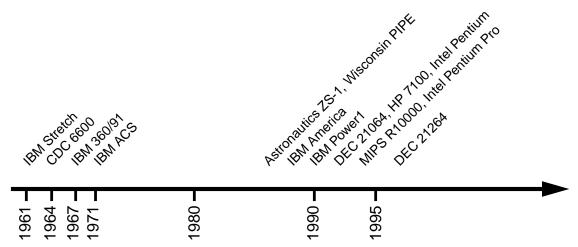

| Figure 1-2. Time line showing evolution of superscalar processors                                                                                                                      |

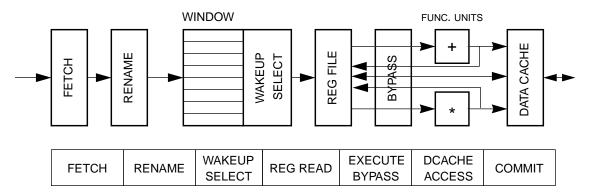

| Figure 2-1. Baseline superscalar model.    15                                                                                                                                          |

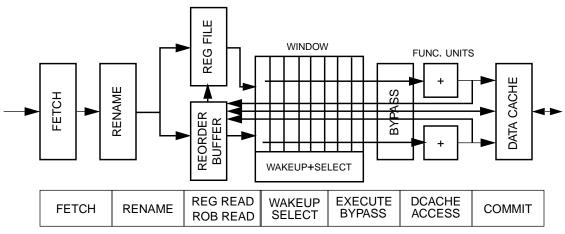

| Figure 2-2. Reservation stations-based superscalar model                                                                                                                               |

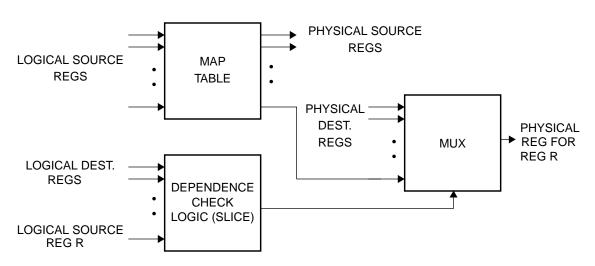

| Figure 2-3. Register rename logic    26                                                                                                                                                |

| Figure 2-4. Renaming example showing dependency checking                                                                                                                               |

| Figure 2-5. Rename map table                                                                                                                                                           |

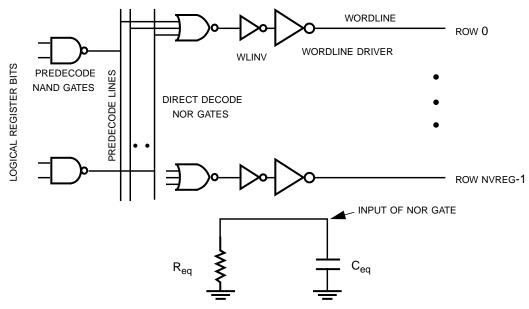

| Figure 2-6. Decoder structure and equivalent circuit       31                                                                                                                          |

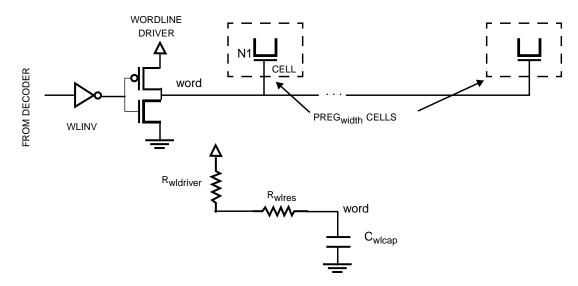

| Figure 2-7. Wordline structure and equivalent circuit                                                                                                                                  |

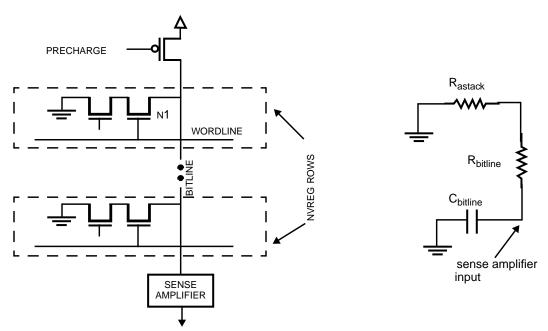

| Figure 2-8. Bitline structure and equivalent circuit    34                                                                                                                             |

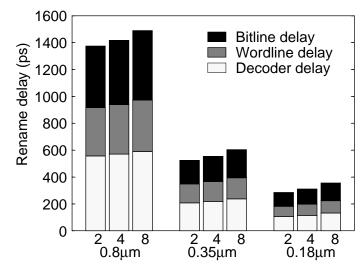

| Figure 2-9. Rename delay versus issue width                                                                                                                                            |

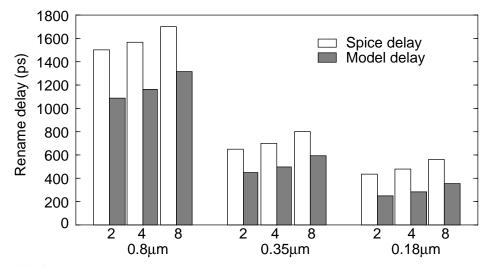

| Figure 2-10. Model delay results for rename logic                                                                                                                                      |

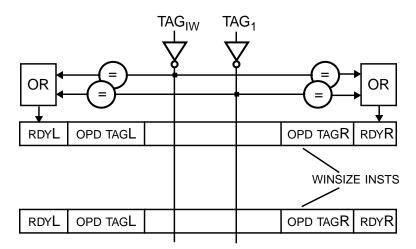

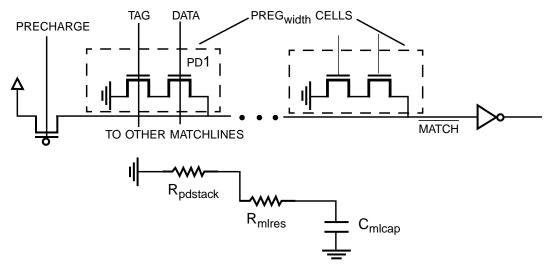

| Figure 2-11. Window wakeup logic    39                                                                                                                                                 |

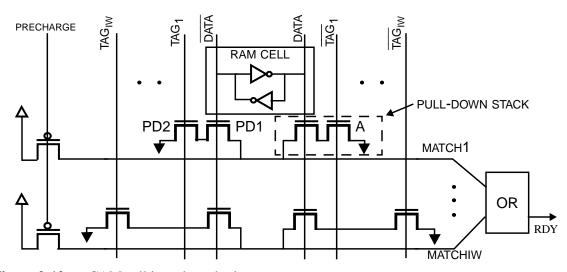

| Figure 2-12. CAM cell in wakeup logic    40                                                                                                                                            |

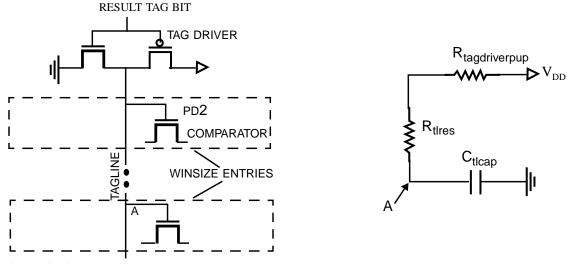

| Figure 2-13. Tag drive structure    41                                                                                                                                                 |

| Figure 2-14. Tag match structure.    44                                                                                                                                                |

| Figure 2-15. Logic for ORing individual match signals       45                                                                                                                         |

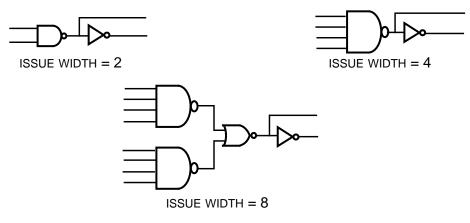

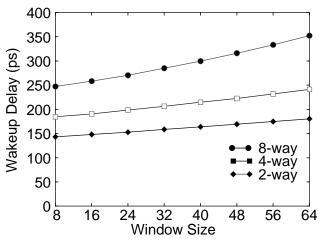

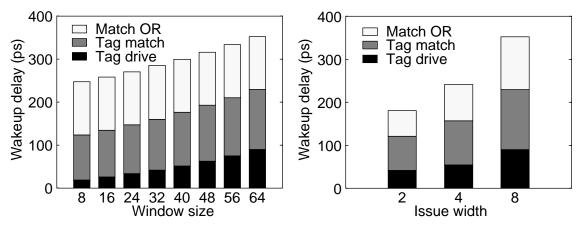

| Figure 2-16. Wakeup logic delay versus window size $\ldots \ldots \ldots \ldots \ldots 4\epsilon$                                                                                      |

| Figure 2-17. Wakeup logic delay                                                                                                                                                        |

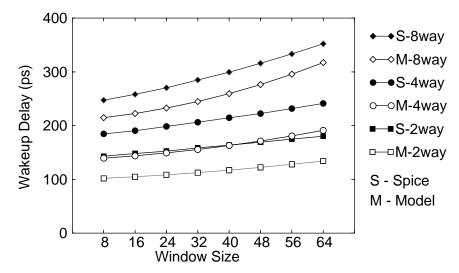

| Figure 2-18. Wakeup delay versus feature size    48                                                                                                                                    |

| Figure 2-19. Model delay results for wakeup logic       49                                                                                                                             |

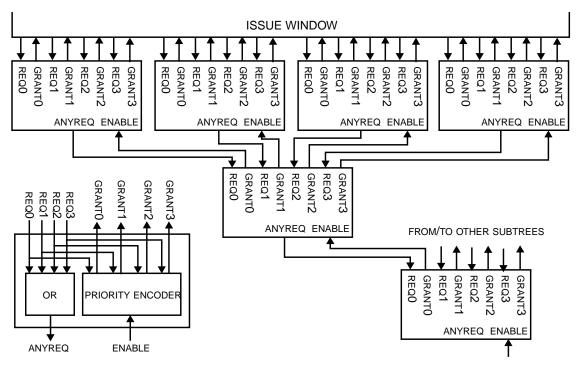

| Figure 2-20. Selection logic    51                                                                                                                                                     |

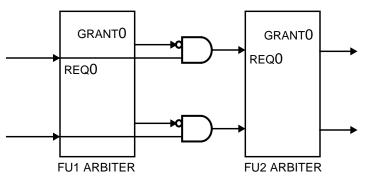

| Figure 2-21. Handling multiple functional units    52                                                                                                                                  |

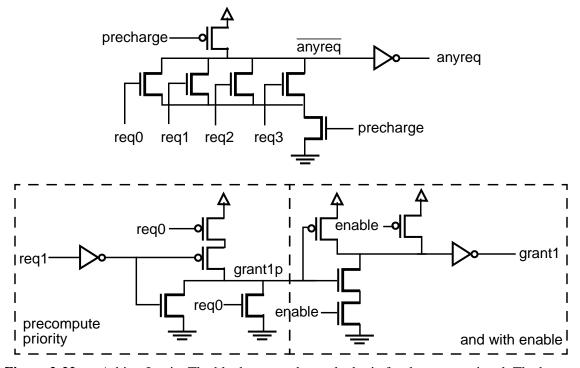

| Figure 2-22. Arbiter Logic.    55                                                                                                                                                      |

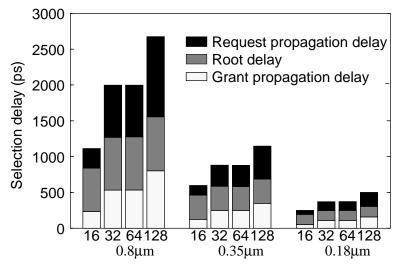

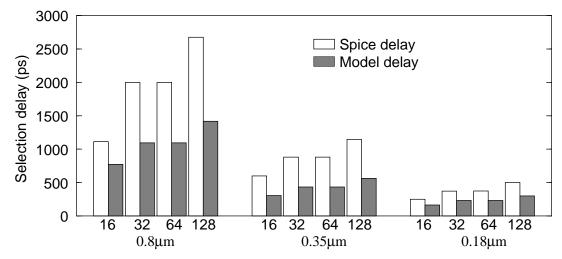

| Figure 2-23. Selection delay versus window size $\ldots \ldots \ldots$ |

| Figure 2-24. Model delay results for selection logic    57                                                                                                                             |

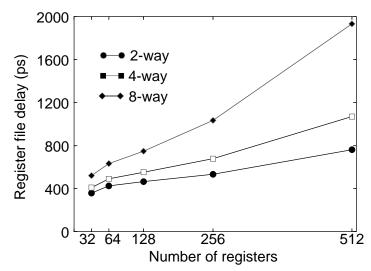

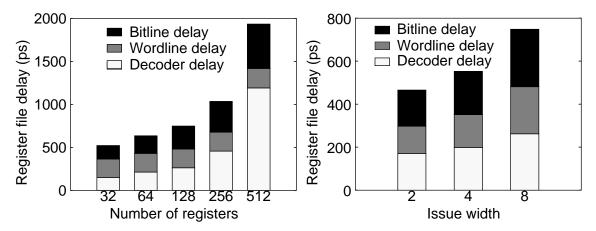

| Figure 2-25. Register file logic delay.    63                                                                                                                                          |

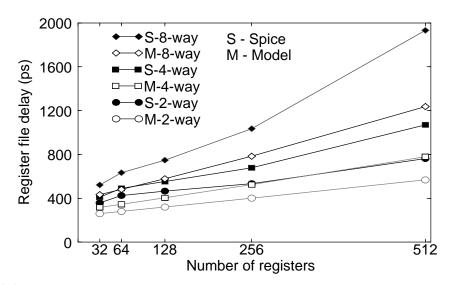

| Figure 2-26. Breakup of register file delay    65                                                                                                                                      |

| Figure 2-27. Model delay results for register file logic                        |

|---------------------------------------------------------------------------------|

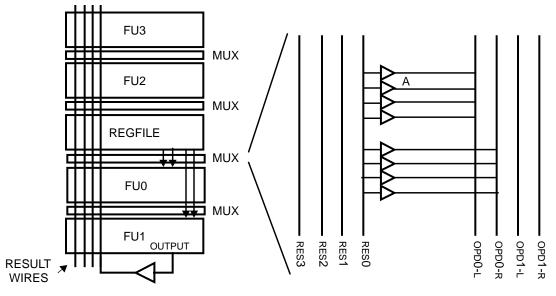

| Figure 2-28. Bypass logic                                                       |

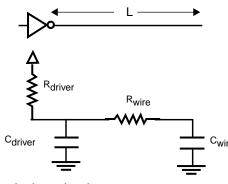

| Figure 2-29. Bypass logic equivalent circuit                                    |

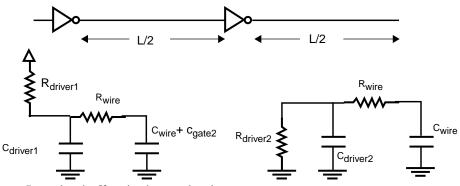

| Figure 2-30. Inserting buffers in the result wires                              |

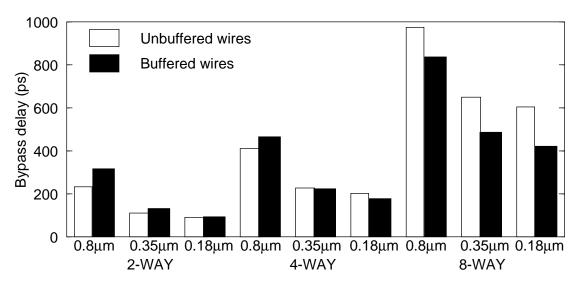

| Figure 2-31. Bypass logic delays                                                |

| Figure 2-32. Model delay results for bypass logic                               |

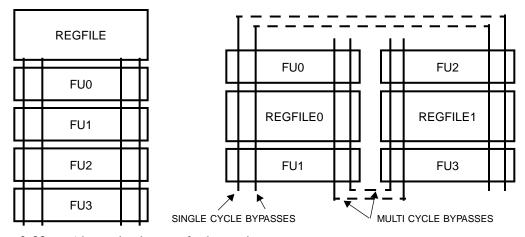

| Figure 2-33. Alternative layouts for bypassing                                  |

| Figure 2-34. Pipelining wakeup and select                                       |

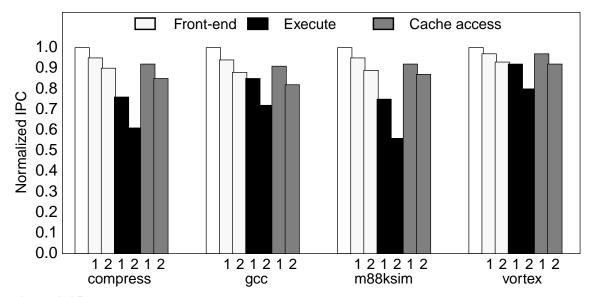

| Figure 2-35. Effect of pipelining on IPC                                        |

| Figure 2-36. Overall delay results                                              |

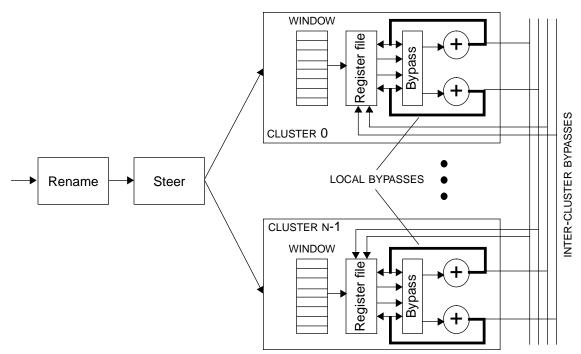

| Figure 3-1. Dependence-based superscalar microarchitecture                      |

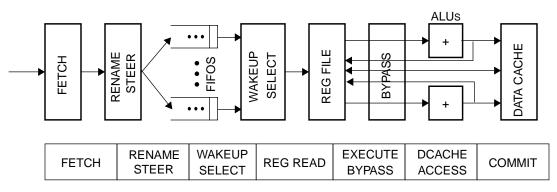

| Figure 3-2. Fifo-based microarchitecture                                        |

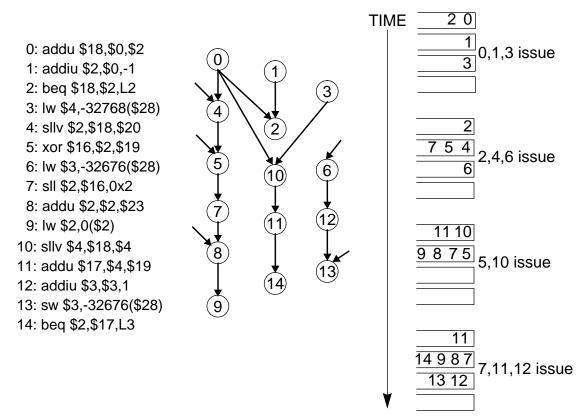

| Figure 3-3. Instruction steering example                                        |

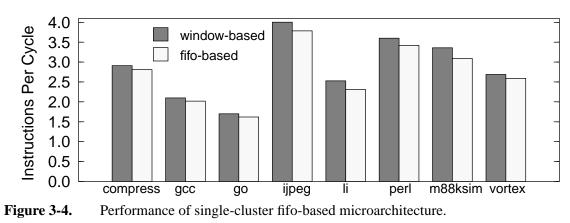

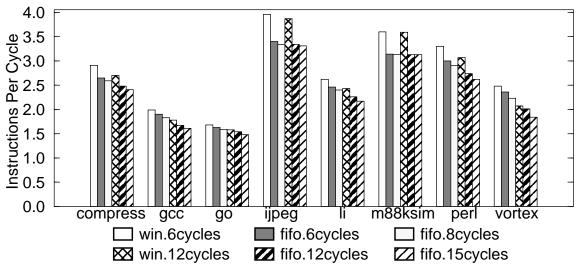

| Figure 3-4. Performance of single-cluster fifo-based microarchitecture          |

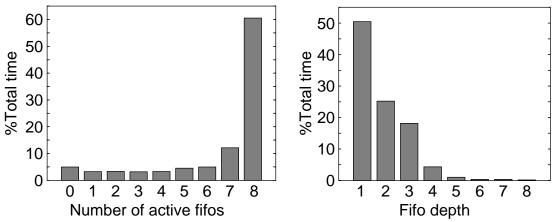

| Figure 3-5. Fifo utilization                                                    |

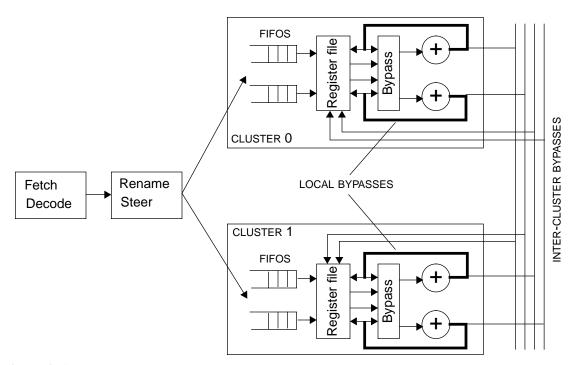

| Figure 3-6. Fifo-based microarchitecture with two clusters                      |

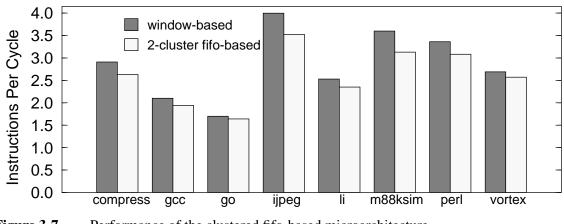

| Figure 3-7. Performance of the clustered fifo-based microarchitecture           |

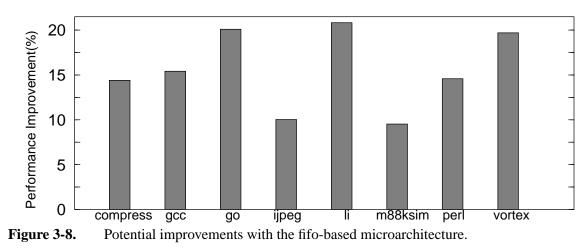

| Figure 3-8. Potential improvements with the fifo-based microarchitecture        |

| Figure 3-9. Effect of Scaling Instruction and Data Cache Miss Latency           |

| Figure 3-10. Other dependence-based microarchitectures                          |

| Figure 3-11. Fifo steering hardware                                             |

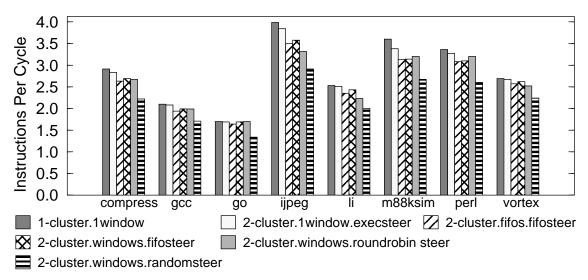

| Figure 3-12. Performance of dependence-based superscalar microarchitectures 107 |

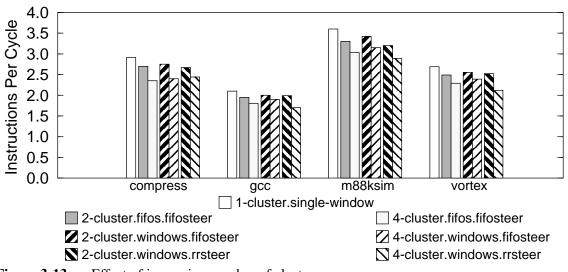

| Figure 3-13. Effect of increasing number of clusters                            |

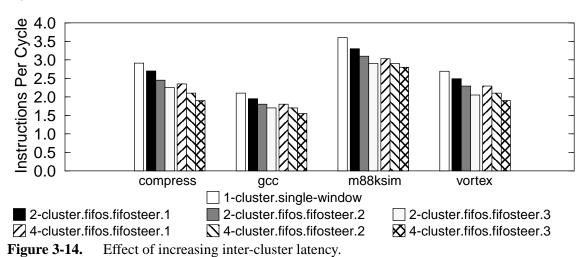

| Figure 3-14. Effect of increasing inter-cluster latency                         |

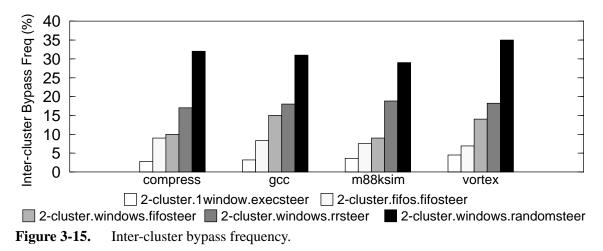

| Figure 3-15. Inter-cluster bypass frequency 111                                 |

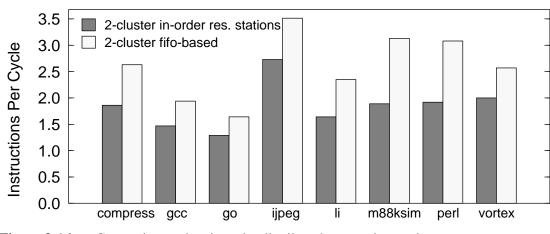

| Figure 3-16. Comparing against in-order distributed reservation stations        |

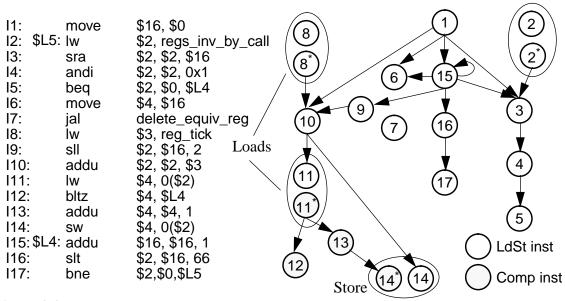

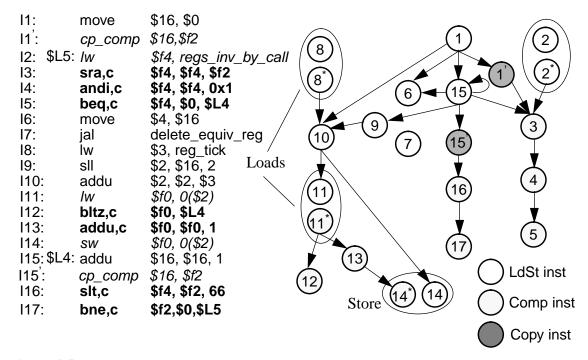

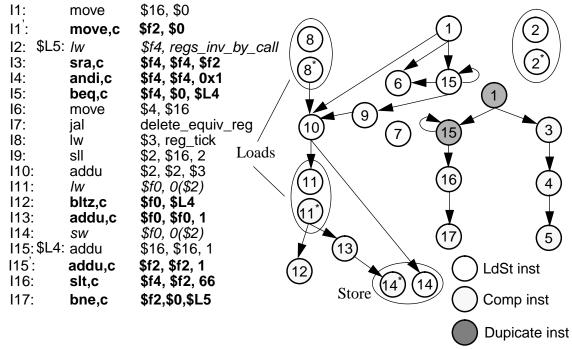

| Figure 4-1. An example program fragment 124                                     |

| Figure 4-2. Code partitioning for example fragment 125                          |

| Figure 4-3. Program slices                                                      |

х

|                                                         | xi  |

|---------------------------------------------------------|-----|

| Figure 4-4. Static dependence graph for example program | 128 |

| Figure 4-5. Partitioning with copies                    | 131 |

| Figure 4-6. Partitioning with code duplication          | 133 |

| Figure 4-7. Percentage of instructions assigned to Comp | 138 |

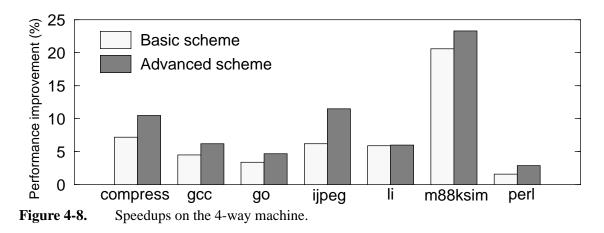

| Figure 4-8. Speedups on the 4-way machine               | 139 |

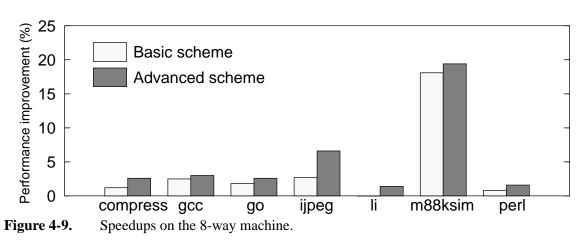

| Figure 4-9. Speedups on the 8-way machine               | 140 |

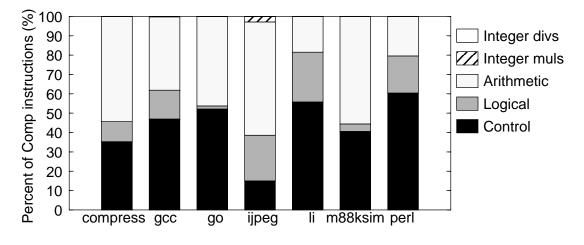

| Figure 4-10. Instruction mix of the Comp partition      | 142 |

xii

# List of Tables

| Table 2.1: Terminology.    21                                                      |

|------------------------------------------------------------------------------------|

| Table 2.2: Fan-in of decoder gates.    59                                          |

| Table 3.1: Delay of reservation table in 0.18µm technology.    95                  |

| Table 3.2: Baseline simulation model    105                                        |

| Table 3.3: Various microarchitectures simulated.    106                            |

| Table 4.1: Extra opcodes supported in the Comp subsystem.    123                   |

| Table 4.2: Machine parameters.    136                                              |

| Table 4.3: Benchmark programs.    137                                              |

| Table A.1: Spice parameters.    161                                                |

| Table A.2: Metal resistance and capacitance.    162                                |

| Table A.3: Break down of rename delay.    162                                      |

| Table A.4: Break down of window wakeup delay for 0.8µm technology 163              |

| Table A.5: Break down of window wakeup delay for 0.35µm technology 164             |

| Table A.6: Break down of window wakeup delay for 0.18µm technology 165             |

| Table A.7: Break down of selection delay.    166                                   |

| Table A.8: Overall delay results for 0.8µm technology.    167                      |

| Table A.9: Overall delay results for 0.35µm technology.    167                     |

| Table A.10: Overall delay results for 0.18µm technology.    167                    |

| Table B.1: Constants in decoder delay equation for rename logic.       169         |

| Table B.2: Constants in wordline delay equation for rename logic.       170        |

| Table B.3: Constants in bitline delay equation for rename logic.       170         |

| Table B.4: Constants in total delay equation for rename logic.    171              |

| Table B.5: Constants in tag drive delay equation for wakeup logic.       171       |

| Table B.6: Constants in tag match delay equation for wakeup logic.       172       |

| Table B.7: Constants in match OR delay equation for wakeup logic.       172        |

| Table B.8: Constants in total delay equation for wakeup logic.       173           |

| Table B.9: Constants in total delay equation for selection logic.       174        |

| Table B.10: Constants in decoder delay equation for register file logic.       174 |

xiv

| Table B.11: Constants in wordline delay equation for register file logic. | 175 |

|---------------------------------------------------------------------------|-----|

| Table B.12: Constants in bitline delay equation for register file logic.  | 175 |

| Table B.13: Constants in total delay equation for register file logic.    | 176 |

| Table B.14: Constants in total delay equation for data bypass logic.      | 176 |

# **Chapter 1**

### Introduction

#### 1.1 Motivation

Over the past decade superscalar microprocessors have become a source of tremendous computing power. They form the core of a wide spectrum of high-performance computer systems ranging from desktop computers to small-scale parallel servers to massively-parallel systems. To satisfy the ever-growing need for higher levels of computing power, computer architects need to investigate techniques that continue improving the performance of superscalar microprocessors while considering both changing technology and applications.

Superscalar microarchitectures [Joh91, SS95], on which superscalar microprocessors are based, deliver high performance by executing multiple instructions in parallel every cycle. Hardware is used to detect and execute parallel instructions. This technique of exploiting fine-grain parallelism at the instruction level to improve performance is commonly referred to as *instruction-level parallelism*. The maximum number of instructions processed in parallel, also known as the *width* of the microarchitecture, is typically four for the fastest microprocessors [Gwe96a, Kum96] available today. A typical superscalar

Figure 1-1. A typical superscalar microarchitecture.

microarchitecture, illustrated in Figure 1-1, operates as follows. Multiple instructions are fetched from the instruction cache every cycle. The instructions are then decoded, checked for dependences, renamed, and deposited in an instruction window. The instructions wait in the instruction window for their operands and functional units to become available. Hardware continuously monitors the dependences between instructions in the window and selects appropriate instructions for parallel execution. The overall hardware apparatus responsible for creating the window, monitoring dependences between instructions in the window, selecting instructions for execution from the window, and providing data operands to the instructions, henceforth collectively referred to simply as *issue logic*, is one of the most performance-critical components in a superscalar processor. The issue logic largely determines the amount of instruction-level parallelism that can be extracted. Hence, optimizing this logic is of paramount importance.

The net performance of a superscalar microarchitecture is directly proportional to the product —*Instructions Per Cycle* × *Clock Frequency*. Instructions Per Cycle or IPC is the sustained number of instructions executed in parallel every cycle. IPC depends on a number of factors including the inherent parallelism in the program, the width of the microarchitecture, the size of the instruction window, and other characteristics of the scheme used for extracting parallelism. Clock Frequency is the speed at which the microarchitecture is

clocked and is determined by the delays associated with the significant critical paths in the microarchitecture.

For the past decade, the general approach for improving the performance of superscalar microprocessors has been to build microarchitectures with increasingly complex issue logic that can boost the IPC factor in the performance equation. The increase in complexity results from a wider microarchitecture, a bigger instruction window, and more complex issue methods. However, there is a potential problem with continuing this strategy. While complex issue logic might be able to extract more parallelism, it can easily limit the clock speed of the microarchitecture. Microarchitectures with more complex issue logic typically require longer wires and deeper levels of logic to implement, and hence, can require longer critical paths in the microarchitecture. Thus, there is a danger of squandering the gains in IPC to a slow clock, resulting in reduced benefits or even no benefit in overall performance. Furthermore, technology trends suggest that wire delays will increasingly dominate total delay as feature sizes are reduced. These factors suggest that straightforward scaling of current microarchitectures for higher IPCs might not be the most appropriate approach for delivering higher performance in future. In summary, there is a trade-off between issue logic complexity, instructions per cycle (IPC), and clock speed that needs to be carefully examined while designing improved superscalar microarchitectures. This thesis examines this trade-off.

The above discussion underscores the need for investigating superscalar microarchitectures that judiciously use hardware complexity for exploiting significant levels of instruction-level parallelism while permitting a fast clock. We call such microarchitectures *complexity-effective superscalar microarchitectures*. These microarchitectures attempt to maximize the product of IPC and Clock Frequency rather than push the envelope for each term separately. This thesis proposes and evaluates two such complexity-effective superscalar microarchitectures called *dependence-based microarchitectures* and *integer-decoupled microarchitectures*. It must be mentioned that the complexity of a design can have different, sometimes conflicting meanings. To a verification engineer, design A is more complex than design B if the time taken to verify design A is greater than that for design B. On the other hand, a logic designer typically measures complexity in terms of the number of gates required to implement a design. In this thesis, complexity is measured as the delay of the critical path through a piece of logic, and the longest path through any of the pipeline stages determines the clock speed. Complexity, as we define it, is largely independent of the number of gates required or the time to verify the design. Instead, complexity is dependent on a number of factors that could affect the delay of the critical paths in the design such as the number of logic stages, the length of wires, the degree of fan-out of a particular signal, and the number of associative compares performed every cycle.

While designing for complexity-effectiveness is a desirable goal, the question that immediately arises is: how do we quantify the complexity of a microarchitecture? It is commonplace to measure the IPC of a new microarchitecture, typically by using simulation. Such simulations count clock cycles and provide IPC in a direct manner. However, the complexity of a microarchitecture is much more difficult to determine — to be very accurate, it requires a full implementation in a specific technology. What is very much needed are fairly straightforward measures of complexity that can be used by microarchitects at a fairly early stage of the design process. Such methods would allow the determination of complexity-effectiveness. This thesis takes a step in the direction of characterizing complexity and complexity trends.

#### **1.2 Historical Perspective**

This section briefly outlines the evolution of ILP processors, especially superscalar processors, while highlighting major trends in design trade-offs involving hardware complexity and performance. Figure 1-2 illustrates the evolution of ILP processors with a time line.

4

Figure 1-2. Time line showing evolution of superscalar processors.

Pipelining [Kog81] is the most prevalent technique for exploiting instruction-level parallelism. Pipelining enables overlapped execution of multiple instructions by breaking instruction processing into segments, just like an assembly line. It was first implemented in the IBM Stretch [Buc62] in 1961. Ever since, pipelining has been adopted by almost all high-performance designs.

The 1960s saw two pioneering machines that laid the foundation for much of the ILP techniques in wide use today. These were the CDC 6600 [Tho61,Tho63] and the IBM 360/91 [AST67] machines delivered in 1964 and 1967 respectively. The CDC 6600 implemented an impressive repertoire of architectural techniques, especially for its time — a clean load/store instruction set that enabled efficient pipelining, multiple functional units, and scoreboarding logic for dynamic scheduling. In the IBM 360/91 floating-point subsystem, the designers implemented a more sophisticated issuing scheme known as *Tomasulo's algorithm* [Tom67] after its inventor. The issuing schemes of most current superscalar microprocessors can be viewed as variants of Tomasulo's scheme. Even though the two designs implemented out-of-order execution, they were both single issue machines. Out-of-order execution was used to overlap execution of long-latency operations, tolerate slow memory accesses, and, in the case of the 360/91, mitigate the performance drawbacks of having few (8) floating-point registers.

Soon after, both IBM and CDC reverted back to simpler in-order issue, pipelined machines with a fast clock. The follow-on machines, the CDC 7600 and the IBM 360/85, issued instructions strictly in order. The exact reasons for this reversal are not known, but issues like the difficulty of debugging complex issue methods and the extra hardware cost are likely considerations on which the decision was based. Also, the use of a cache in the IBM 360/85 to tolerate memory latency probably made out-of-order execution less attractive. Two decades later, mushrooming transistor budgets, advanced CAD tools, and the market for high-performance, would trigger the resurgence of 6600 and 360/91-like schemes in the context of superscalar microprocessors.

The 1970s was not an eventful decade for ILP processors. All commercial machines still had a peak fetch rate of one instruction per cycle. However, during this time, some of the initial research in the area of multiple-instruction issue [TF70,RF72,Sch71] was carried out. Schorr describes an exploratory design [Sch71] capable of fetching, decoding, and executing multiple instructions every cycle. The design, later to be known as the IBM ACS (Advanced Computer System), was partitioned into the *index* unit that performed addressing operations and the *arithmetic* unit that executed arithmetic instructions. The arithmetic unit had a window of eight instructions out of which three instructions could be issued for execution every cycle. Unfortunately, the project was cancelled due to the incompatibility of the ISA with the S/360 ISA and other problems.

The late 1970s saw the emergence of a new paradigm for ILP called VLIW — Very Long Instruction Word — that grew out of early microcode machines [Wil51] and systems built by Floating Point Systems [Cha81]. VLIWs rely on the compiler to pack independent operations into a long instruction word which are then executed on multiple, independent functional units. The arguments in favor of VLIW are two-fold. First, since the compiler has a larger scope than the hardware to look for independent operations, VLIWs should be able to exploit more parallelism than superscalars. Second, since complex issue hardware is no longer required, VLIW processors can be clocked much faster than superscalar processors. However, even though a few commercial VLIW processors were built, the para-

digm has not gained widespread acceptance. There are a number of reasons. First, to match hardware techniques, the paradigm requires sophisticated compiler technology that implements advanced techniques like software pipelining, global scheduling to move instructions across branches, trace scheduling [Fis81], and memory disambiguation. While advanced VLIW compilers [Ell85] that focussed on floating-point codes have been developed, it is not clear how well they perform on integer code where branches occur frequently and memory disambiguation is hard. Second, exposing hardware details to the compiler results in binaries that might not be portable across implementations. Third, the sophisticated transformations tend to result in increases in code size that can potentially degrade overall performance.

The lack of ILP innovation continued into the early 1980s. This was the period when most microprocessor designers were busy implementing RISC concepts [PS81] in the form of simple pipelining, and new ILP techniques did not receive much attention. However, the second half of the 1980s saw renewed ILP activity both in the superscalar and VLIW areas. The commercial implementations of the VLIW concept — Trace [CNO<sup>+</sup>88] by Multiflow and Cydra 5 [RYYT89] by Cydrome — were delivered during this time. However, these implementations had limited success in penetrating commercial markets. At the same time, three experimental superscalar prototype [S<sup>+</sup>87,GHL<sup>+</sup>85,Gro90] efforts were underway. These were the Astronautics ZS-1, the Wisconsin PIPE, and the IBM America machines. All three of them, implemented a limited form of multiple issue integer instructions, including memory access related instructions, were issued in parallel with floating-point instructions. The ZS-1 and the PIPE used architectural queues to communicate values between the two classes of instructions. The America design used register renaming to achieve the same effect. All the designs still used in-order issue to execute instructions within each class. This simplified issue logic while allowing a limited form of out-of-order execution.

The early 1990s saw a number of superscalar implementations [KM89, D<sup>+</sup>92,K<sup>+</sup>93,Hsu94] — Intel i860, DEC 21064, HP 7100, MIPS R8000, and others. All of

them, with the exception of the Power1, were simple in-order implementations that achieved multiple-issue by executing instructions of different types (load/store, branch, floating-point) in parallel. The IBM Power1 [Gro90] based on the earlier America design implemented register renaming and sophisticated instruction fetch mechanisms. Other vendors continued on the path of simple in-order implementations with a faster clock. This gave rise to the "speed demons" (simple implementations with a fast clock) versus "braini-acs" (complex implementations with a slow clock) controversy [Gwe93].

The mid 1990s saw some convergence between the two camps. Almost all vendors moved towards designs implementing complex out-of-order microarchitectures based on the 6600 and 360/91 schemes as well as ideas explored in academia [SP88,Soh90,HP86,DT92,YP92]. At the time of the writing of this thesis, every major microprocessor vendor has a product implementing sophisticated dynamic scheduling.

In 1996, Digital Equipment Corporation, long considered to be the bastion of the speed demons, announced plans for a product (DEC 21264 [Gwe96a]) implementing an out-of-order microarchitecture with a relatively fast clock (600 MHz). An interesting feature that stands out in this design is the microarchitectural changes employed to facilitate a fast clock. The integer subsystem is partitioned into two clusters. Instructions are steered from a central window to the clusters. Each cluster has its own copy of the register file. In addition to reducing the number of register file ports, clustering also makes possible fast bypassing between units in the same cluster. These features are described in more detail in Chapter 3. The research presented in this thesis has been highly influenced by this design.

In summary, the superscalar approach<sup>1</sup> has evolved over the years into the mainstream of processor implementations and each generation of designers had to deal with the trade-off between hardware complexity and performance.

<sup>1.</sup> There have been other ILP paradigms, some very successful in their own niche market, that have not been touched upon in this section. Some of these paradigms are vectors [Rus78], superpipe-lining [JW89], autotasking[ABHS89], multiprocessing[FJD80], and dataflow [DM74].

#### **1.3 The Conventional Microarchitecture**

As discussed earlier, current superscalar processors, like the MIPS R1000 [Yea96] and the DEC 21264 [Gwe96a], are typically based on the microarchitecture shown in Figure 1-1. The issue and execution resources in the machine are partitioned into integer and floating-point subsystems. The integer subsystem contains a number of load/store, branch, and functional units that operate on integer operands. The floating-point subsystem is similar to the integer subsystem except it does not contain load/store units, and it operates on floating-point operands. Instruction windows in each subsystem buffer instructions and implement dynamic scheduling as discussed earlier.

The microarchitecture presented in Figure 1-1 will be referred to as the conventional microarchitecture throughout the rest of this thesis. It will be used as a baseline for performance comparisons.

#### **1.4 Thesis Contributions**

#### 1.4.1 Quantifying the Complexity of Superscalar Microarchitectures

The main contribution of this thesis is the development of simple models that both quantify the complexity of superscalar microarchitectures and identify complexity trends. Measurement of implementation complexity of microarchitectural features is going to be increasingly crucial for computer architects to understand and master. While much work remains to be done in this area, the work presented in this thesis is an important starting point.

The structures in a baseline superscalar microarchitecture whose complexity grows with increasing instruction-level parallelism are identified and analyzed. Each is modeled and Spice simulated for three different feature sizes representing past, present, and future technologies. Simple analytical models are developed that quantify the delay of these structures in terms of microarchitectural parameters of window size and issue width. The

impact of technology trends towards smaller feature sizes is studied. In particular, the impact of poor scaling of wire delays in future technologies is analyzed.

In addition to delays, we study the performance effects of pipelining critical structures. Even if the delay of a structure is relatively large, it may not increase the complexity of the design because the structure's operation can be spread over multiple pipestages. Our analysis identifies structures that are more performance critical. The operation of these structures should be accommodated within a single cycle to avoid significant degradation in IPCs achieved, especially for programs with limited parallelism.

Our analysis shows that the issue window logic and data bypass logic are going to be the most critical structures in future. The delay of the issue window logic increases at least linearly with both issue width and window size. The functioning of this logic involves broadcasting of multiple tags on long wires spanning the window — an operation that does not scale well in future technologies. Furthermore, the delay of the window logic must fit in a pipestage to avoid performance degradation. Hence, this logic can be a key limiter of clock speed as we move towards wider issue widths, large window sizes, and advanced technologies in which wire delays dominate total delay. Another structure that can potentially limit clock speed especially in future technologies is the data bypass logic. The result wires that are used to bypass operand values increase in length as the number of functional units is increased. This results in a quadratic dependence of the bypass delay on issue width. Utilizing buffers helps mitigate the problem to an extent, but a linear increase in delay with issue width still persists. Just like the window logic, data bypass logic must also complete within a single cycle for performance reasons. Hence, bypass delays could ultimately become significant and force architects to consider more decentralized organizations.

#### 1.4.2 Dependence-based Superscalar Microarchitectures

This thesis studies a new family of complexity-effective microarchitectures called dependence-based superscalar microarchitectures that address two major sources of com-

plexity — window logic and data bypass logic — in conventional microarchitectures. Dependence-based microarchitectures use two main techniques to achieve the dual goals of high IPC and a fast clock. First, the machine is *partitioned* into multiple clusters each of which contains a slice of the instruction window and execution resources of the whole processor. This enables high-speed clocking of the clusters since the narrow issue width and the small instruction window of each cluster keeps critical delays small. The second technique involves *intelligent steering* of instructions to the multiple clusters so that the full width of the machine is utilized while minimizing the performance degradation due to slow inter-cluster communication.

A number of design alternatives and steering heuristics for dependence-based microarchitectures are proposed and evaluated using simulations. Among the designs presented, one that is particularly attractive is what we call the *fifo-based microarchitecture*. This microarchitecture implements the instruction window as a collection of a small number of fifos and steers dependent chains of instructions to the same fifo. Simulations show little slowdown as compared with a completely flexible issue window when performance is measured in clock cycles. Furthermore, because only instructions at fifo heads need to be awakened and selected, issue logic is simplified and the clock cycle is faster —consequently overall performance is improved. For example, our results show that, due to the clock speed advantage, the overall performance of a 2X4-way<sup>1</sup> fifo-based microarchitecture is 14% higher than that of a typical 8-way superscalar even though the proposed microarchitecture degrades IPC performance by 8% relative to the typical microarchitecture. By grouping dependent instructions together, the fifo-based microarchitecture also helps minimize the performance degradation due to slow bypasses in future wide-issue machines.

<sup>1.</sup> A 8-way microarchitecture comprising two clusters — each consisting of four fifos feeding four functional units.

# 1.4.3 Integer-decoupled Microarchitecture

This thesis proposes another complexity-effective microarchitecture called the *integer-decoupled microarchitecture* that improves the performance of integer programs and can be integrated into a conventional microarchitecture with little or no increase in complexity. The integer-decoupled microarchitecture starts with a conventional microarchitecture and augments the floating-point units to perform simple integer operations. Some integer instructions, those not used for computing addresses and accessing memory, are then offloaded to the augmented floating-point subsystem by the compiler. Consequently, for integer programs, the integer-decoupled microarchitecture provides a larger window for dynamic scheduling as well as extra issue and execution bandwidth at no increase in complexity.

We evaluate the potential performance improvements with the integer-decoupled microarchitecture. Our results show that a modest to significant fraction of the total dynamic instructions in our benchmark programs can be off-loaded to the augmented floating-point subsystem. In doing so, the integer-decoupled microarchitecture provides speedups from 3% to 23% over a 4-wide (2 integer and 2 floating-point units) conventional microarchitecture. Furthermore, the results show that only simple integer operations need to be supported in the floating-point subsystem. This minimizes the additional hardware cost.

#### **1.5 Thesis Organization**

The remainder of this thesis is organized as follows. Chapter 2 describes the simple models that we developed, along with the methodology used, for quantifying the complexity of superscalar microarchitectures. Chapter 3 proposes and evaluates dependence-based superscalar microarchitectures. Chapter 4 introduces and investigates the integer-decoupled microarchitecture. Finally, Chapter 5 gives conclusions and suggests future directions to explore. The appendices includes detailed experimental results for Chapter 2.

### Chapter 2

# Quantifying the Complexity of Superscalar Microarchi-

### tectures

The complexity of a microarchitecture is difficult to determine — to be very accurate, it would require a full implementation in a specific technology. What is very much needed are fairly straightforward measures, possibly only relative measures, of complexity that can be used by microarchitects at a fairly early stage of the design process. This chapter presents work that takes a step in that direction. Simple models that quantify the complexity of superscalar microarchitectures are developed and used to identify long-term complexity trends.

We start by identifying those portions of a microarchitecture whose complexity grows with increasing instruction-level parallelism. Of these, we focus on register rename logic, window logic, register file logic, and data bypass logic. We analyze potential critical paths in these structures and develop models for quantifying their delays. We study the manner in which these delays vary with microarchitectural parameters like window size (the number of instructions from which ready instructions are selected for issue) and issue width (the number of instructions that can be issued in a cycle). We also study the impact of the technology trend towards smaller feature sizes. In particular, we analyze how the poor scaling of wire delays in future affects the overall delay of critical structures.

In addition to delays, we study the performance effects of pipelining critical structures. Even if the delay of a structure is relatively large, it may not increase the complexity of the design because the structure's operation can be spread over multiple pipestages. We analyze structures to identify those whose operation must be accomplished within a single cycle to avoid significant degradation in the number of instructions committed every cycle.

The rest of this chapter is organized as follows. Section 2.1 describes the sources of complexity in a baseline microarchitecture. Section 2.2 describes the methodology we use to study the critical structures identified in Section 2.1. Section 2.3 briefly discusses technology trends. Section 2.4 presents a detailed analysis of each structure and how the delay of the structure varies with microarchitectural parameters and technology parameters. Section 2.5 discusses pipelining issues for each of the structures and presents overall delay results. Finally, Section 2.6 lists related work, and Section 2.7 summarizes the chapter.

#### 2.1 Sources of Complexity

Before delving into specific sources of complexity, we describe the baseline superscalar model assumed for the study. We then list the basic structures that are the primary sources of complexity. Finally, we show how these basic structures are present in one form or another in most current implementations even though these implementations might appear to be different superficially. On the other hand, we realize that it is impossible to capture all possible microarchitectures in a single model and any results provided here have some obvious limitations. We can only provide a fairly straightforward model that is typical of most current superscalar processors, and suggest that techniques similar to those used here can be extended for other, more advanced models as they are developed.

14

Figure 2-1. Baseline superscalar model.

Figure 2-1 illustrates the baseline model and the associated pipeline. The fetch unit fetches multiple instructions every cycle from the instruction cache. Branches encountered by the fetch unit are predicted. Following instruction fetch, instructions are decoded and their register operands are renamed. Register renaming involves mapping the logical register operands of an instruction to the appropriate physical registers. Renamed instructions are then deposited in the issue window, where they wait for their source operands and the appropriate functional unit to become available. As soon as these conditions are satisfied, the instruction is issued and executes on one of the functional units. The operand values of an instruction are either fetched from the register file or are bypassed from earlier instructions in the pipeline. The data cache provides low latency access to memory operands via loads and stores.

The issue window is responsible for monitoring dependences between instructions in the window and issuing instructions to the functional units. The window logic consists of two components — the *wakeup* logic and the *select* logic. The first component is responsible for "waking up" instructions waiting in the issue window for their source operands to become available. Once an instruction is issued for execution, the tag corresponding to its result is broadcast to all the instructions in the window. Each instruction in the window compares the tag with its source operand tags. Once all the source operands of an instruction are available the instruction is flagged *ready* for execution. The select logic is responsible for selecting instructions for execution from the pool of ready instructions. An

instruction is said to be ready if all of its source operands are available. As pointed out earlier, the wakeup logic is responsible for setting the ready flag.

#### 2.1.1 Basic Structures

The most important criterion used for identifying a basic structure for our study is that the delay of the structure should be a function of either issue window size or issue width or both. For example, we consider register renaming to be a basic structure because its delay depends on the number of ports into the mapping table which in turn is determined by the issue width. On the other hand none of the functional units are included in the study because their delay is independent of both the issue width and the window size. In addition, our decision to study a particular structure was based on two observations. First, we are primarily interested in dispatch and issue-related structures because these structures form the core of a microarchitecture and largely determine the amount of parallelism that can be exploited. Second, some of these structures rely on broadcast operations on long wires and hence, their delays might not scale as well as logic-intensive structures in future technologies with smaller feature sizes. Hence, we believe that these structures are potential cycle-time determinants in future wide-issue designs in advanced technologies.

The structures we consider are:

- *Register rename logic*

- Window wakeup logic

- Window selection logic

- Register file logic

- Data bypass logic

There are other important pieces of logic that are not considered in this thesis, even though their delay is a function of issue width. These are:

• Caches.

Instruction and data caches provide low latency access to instructions and memory operands, respectively. In order to provide the necessary load/store bandwidth [SF91] in a superscalar processor, the cache has to be banked or duplicated. The access time of a cache is a function of the size of the cache and the associativity of the cache. Wada et al. [WRP92] and Wilton and Jouppi [WJ94] have developed detailed models that estimate the access time of a cache given its size and associativity.

• Instruction fetch logic

Besides the instruction cache, there are other important parts of fetch logic whose complexity varies with dispatch width. First of all, as instruction issue widths grow beyond the size of a single basic block, it will become necessary to predict multiple branches every cycle. Then, non-contiguous blocks of instructions will have to be fetched from the instruction cache and compacted into a contiguous block prior to renaming. Rotenberg et al. [RBS96] describe the logic required for these operations. However, delay models remain to be developed. And, although they are important, they are not considered here.

Finally, it must be pointed out once again that in real designs there may be structures not listed above that influence the overall delay of the critical path. However, our realistic aim is not to study all of them but to analyze in detail some important ones that have been reported in the literature. We believe that our basic technique can be applied to others, however.

#### 2.1.2 Current Implementations

The structures identified above were presented in the context of the baseline superscalar model shown in Figure 2-1. The MIPS R10000 [Yea96], and the DEC 21264 [Gwe96a] are two implementations of this model. Hence, the structures identified above apply to these two processors.

On the other hand, the Intel Pentium Pro [Gwe95b], the PowerPC 604 [SDC95], and the HAL SPARC64 [Gwe95a] are based on the reservation model shown in Figure 2-2. There are two main differences between the two models. First, in the baseline model all the register values, both speculative and non-speculative, reside in the physical register file. In the reservation station model, the reorder buffer holds speculative values and the register file

Figure 2-2. Reservation stations-based superscalar model.

holds only committed, non-speculative data. Second, operand values are not broadcast to the window entries in the baseline model - only their tags are broadcast; data values go to the physical register file. In the reservation station model, completing instructions broadcast result values to the reservation stations. Issuing instructions read their operand values from the reservation station.

The point to be noted is that the basic structures identified earlier are also present in the reservation station model and are as critical as in the baseline model. The only notable difference is that the reservation station model has a smaller physical register file (equal to the number of architected registers) and might not demand as much bandwidth (as many ports) as the register file in the baseline model, because in this case some of the operands come from the reorder buffer and the reservation stations.

While the discussion of potential sources of complexity is in the context of a baseline superscalar model that is out-of-order, it must be pointed out that some of the critical structures identified apply to in-order processors too. For example, the register file logic, and the data bypass logic are also present in in-order superscalar processors.

#### 2.2 Methodology

Each structure was studied in two phases. In the first phase, a representative CMOS circuit was selected for the structure. This was done by studying designs published in the literature<sup>1</sup> and by collaborating with engineers at Digital Equipment Corporation. In cases where there was more than one possible design, we performed a preliminary study of the designs to select one that was most promising. In one case, register renaming, we had to study (simulate) two different schemes.

In the second phase, the circuit was implemented and optimized for speed. Circuits were designed mostly using static logic. We believe that power and robustness considerations will make static logic more attractive than dynamic logic in future. However, in situations where dynamic logic helped boost the performance significantly, dynamic logic was used. For example, in the window wakeup logic, a dynamic 7-input NOR gate was used for comparisons instead of a static gate. A number of optimizations were applied to improve the speed of the circuits. First, all the transistors in the circuit were manually sized so that overall delay improved. Second, logic optimizations like two-level decomposition were applied to reduce fan-in requirements. Static gates with a fan-in greater than four were avoided. Third, in some cases transistor reordering was used to shorten the critical path. Some of the optimization sites will be pointed out when the individual circuits are described.

We used the HSPICE circuit simulator [Met87] from MetaSoftware to simulate the circuits. In order to simulate the effect of wire parasitics, parasitics were added at appropriate nodes in the Hspice model of the circuit. These parasitics were computed by calculating the length of the wires based on the layout of the circuit and using the values of  $R_{metal}$  and  $C_{metal}$  — the resistance and parasitic capacitance of metal wires per unit length.

<sup>1.</sup> Mainly proceedings of the ISSCC — International Solid-State and Circuits Conference.

To study the effect of reducing the feature size on the delays of the structures, we simulated the circuits for three different feature sizes: 0.8µm, 0.35µm, and 0.18µm respectively. The process parameters for the 0.8µm CMOS process were taken from Johnson and Jouppi's synthetic model [JJ90]. These parameters were used by Wilton and Jouppi [WJ94] to study the access time of caches. Because process parameters are proprietary information, we had to use extrapolation to come up with process parameters for the 0.35µm and 0.18µm technologies. We used the 0.8µm process parameters from Johnson and Jouppi's synthetic model [JJ90], 0.5µm process parameters from MOSIS, and process parameters used in the literature as inputs. The process parameters assumed for the three technologies are listed in Appendix A. Layouts for the 0.35µm and 0.18µm technologies were obtained by appropriately shrinking the layout for the 0.8µm technology.

Finally, basic RC circuit analysis was used to develop simple analytical models that captured the dependence of the delays on microarchitectural parameters like issue width and window size. The relationships predicted by the Hspice simulations were compared against those predicted by our model. In most of the cases, our models were accurate in identifying the relationships.

#### 2.2.1 Caveats

The above methodology does not address the issue of how well the assumed circuits reflect real circuits for the structures. However, by basing our circuits on designs published by microprocessor vendors, we believe that the assumed circuits are close to real circuits. In practice, many circuit tricks can be employed to optimize critical paths for speed. However, we believe that the relative delay times between different configurations should be more accurate than the absolute delay times. Because we are mainly interested in finding trends in the manner in which delays of the structures vary with microarchitectural parameters like window size and issue width, and how the delays scale as the feature size is reduced, we believe that our results are valid.

20

It must also be pointed out that while the absolute delay times presented in this thesis track the resulting clock speed, they cannot be directly converted into clock speeds. There are two reasons for this. First, we do not include the delay of inter-stage latches and the delay resulting from clock skew in our measurements. These two components can be responsible for a non-trivial fraction of the total delay [NH97], especially for high frequency designs. Second, the delay of a design can show considerable variance with process parameters and temperature of operation. Commercial designs are required to operate over a range of process parameters and physical temperatures. Our designs were simulated for a single set of process parameters and a single temperature point ( $25 \,^{\circ}$ C).

#### 2.2.2 Terminology

Table 2.1 defines some of the common terms used in the rest of this chapter. The remaining terms will be defined when they are introduced.

| Symbol                 | Represents                                |

|------------------------|-------------------------------------------|

| IW                     | Issue width                               |

| WINSIZE                | Window size                               |

| NVREG                  | Number of logical registers               |

| NPREG                  | Number of physical registers              |

| NVREG <sub>width</sub> | Width of logical register tags            |

| NPREG <sub>width</sub> | Width of physical register tags           |

| DATA <sub>width</sub>  | Width of datapath                         |

| R <sub>metal</sub>     | Resistance of metal wire per unit length  |

| C <sub>metal</sub>     | Capacitance of metal wire per unit length |

Table 2.1: Terminology.

#### 2.3 Technology Trends

Feature sizes of MOS devices have been steadily decreasing. This trend [Ass97] towards smaller devices is likely to continue at least for the next decade. In this section, we briefly

discuss the effect of shrinking feature sizes on circuit delays. The effect of scaling feature sizes on circuit performance is an active area of research  $[D^+74, MF95]$ . We are only interested in illustrating the trends in this section.

Circuit delays consist of logic delays and wire delays. Logic delays result from gates that drive other gates. Wire delays are the delays resulting from driving values on wires.

# 2.3.1 Logic Delays

The delay of a logic gate can be written as

$$Delay_{gate} = (C_L \times V)/I$$

where  $C_L$  is the load capacitance at the output of the gate, V is the supply voltage, and I is the average charging/discharging current. I is a function of  $I_{dsat}$  — the saturation drain current of the devices forming the gate. As the feature size is reduced, the supply voltage has to be scaled down to keep the power consumption at manageable levels. Because voltages cannot be scaled arbitrarily they follow a different scaling curve from feature sizes. For submicron devices [Rab96], if S is the scaling factor for feature sizes, and U is the scaling factor for supply voltages, then  $C_L$ , V, and I scale by factors of 1/S, 1/U, and 1/U respectively. Hence, the overall gate delay scales by a factor of 1/S. Therefore, gate delays decrease uniformly as the feature size is reduced.

#### 2.3.2 Wire Delays

If L is the length of a wire, then the intrinsic RC delay of the wire is given by

$$Delay_{wire} = 0.5 \times R_{metal} \times C_{metal} \times L^2$$

where  $R_{metal}$ ,  $C_{metal}$  are the resistance and parasitic capacitance of metal wires per unit length respectively and L is the length of the wire. The factor 0.5 is introduced because we use the first order approximation that the delay at the end of a distributed RC line is (RC)/2 (we assume the resistance and capacitance are distributed uniformly over the length of the wire).

In order to study the impact of shrinking feature sizes on wire delays we first have to analyze how the resistance,  $R_{metal}$ , and the parasitic capacitance,  $C_{metal}$ , of metal wires vary with feature sizes. We use the simple model presented by Bohr [Boh95] to estimate how  $R_{metal}$  and  $C_{metal}$  scale with feature size. Note that both these quantities are per unit length measures. Using Bohr's model [Boh95],

$$\begin{split} R_{metal} &= \rho / (width \times thickness) \\ C_{metal} &= C_{fringe} + C_{parallelplate} \\ &= 2 \times \varepsilon \times \varepsilon_0 \times (thickness) / (width) + 2 \times \varepsilon \times \varepsilon_0 \times (width) / (thickness) \end{split}$$

where *width* is the width of the wire, *thickness* is the thickness of the wire,  $\rho$  is the resistivity of metal, and  $\varepsilon_0$  are permittivity constants.

The average metal thickness has remained relatively constant for the last few generations while the width has been decreasing in proportion to the feature size. Hence, if *S* is the scaling factor for feature sizes, the scaling factor for  $R_{metal}$  is *S*. The metal capacitance has two components: fringe capacitance and parallel-plate capacitance. Fringe capacitance is the result of capacitance between the side-walls of adjacent wires and capacitance between the side-walls of the wires and the substrate. Parallel-plate capacitance is the result of capacitance between the bottom-wall of the wires and the substrate. Assuming that the thickness remains constant, it can be seen from the equation for  $C_{metal}$  that the fringe capacitance becomes dominant as we move towards smaller feature sizes. Rahmat et al. [RNOM95] show that as feature sizes are reduced, the fringe capacitance will be responsible for an increasingly larger fraction of the total capacitance. For example, they show that for feature sizes less than 0.1µm, the fringe capacitance contributes 90% of the total capacitance. In order to accentuate the effect of wire delays and to be able to identify their effects, we assume that the metal capacitance is largely determined by the fringe capacitance and therefore the scaling factor for  $C_{metal}$  is also S.

Using the above scaling factors in the equation for the wire delay, we can compute the scaling factor for wire delays as,

Scaling Factor =

$$S \times S \times (1/S)^2$$

= 1

Note that the length scales as 1/S for local interconnects. In this study we are only interested in local interconnects. This might not be true for global interconnects like the clock because their length also depends on the die size.

Hence, as feature sizes are reduced, wire delays remain constant. This, coupled with the fact that logic delays decrease uniformly with feature size, implies that wire delays will dominate total delays in future. In reality, the situation is further aggravated for two reasons. First, not all wires reduce in length perfectly (by a factor of *S*). Second, some of the global wires, like the clock, actually increase in length due to bigger dice that are made possible with each generation.

McFarland and Flynn [MF95] studied various scaling schemes for local interconnect and conclude that a *quasi-ideal* scaling scheme closely tracks future deep submicron technologies. Quasi-ideal scaling performs ideal scaling of the horizontal dimensions but scales the thickness more slowly. The scaling factor for RC delay per unit length for their scaling model is  $(0.9 \times S^{1.5} + 0.1 \times S^{2.5})$ . In comparison, for our scaling model, the scaling factor for RC delay per unit length is a more conservative, and simpler,  $S^2$ .

# 2.4 Complexity Analysis

In this section we discuss the critical structures in detail. The presentation of each structure is organized as follows. First, we describe the logical function implemented by the

structure. Then, we present possible schemes for implementing the structure and describe one of the schemes in detail. Next, we analyze the overall delay of the structure in terms of microarchitectural parameters like issue width and window size using simple delay models. Finally, we present Spice simulation results, identify trends in the results and discuss how the results conform to the delay analysis performed earlier.

### 2.4.1 Register Rename Logic

The register rename logic is used to translate logical register designators into physical register designators. Logically, this is accomplished by accessing a map table with the logical register designator as the index. Because multiple instructions, each with multiple register operands, need to be renamed every cycle, the map table has to be multi-ported. For example, a 4-wide issue machine with two read operands and one write operand per instruction requires 8 read ports and 4 write ports into the mapping table. The high level block diagram of the rename logic is shown in Figure 2-3. The map table holds the current logical to physical mappings. In addition to the map table, dependence check logic is required to detect cases where the logical register being renamed is written by an earlier instruction in the current group of instructions being renamed. The dependence check logic detects such dependences and sets up the output MUXes so that the appropriate physical register designators are generated. The shadow table is used to checkpoint old mappings so that the processor can quickly recover to a precise state from branch mispredictions. At the end of every rename operation, the map table is updated to reflect the new logical to physical mappings created for the result registers of the current rename group.

Figure 2-3. Register rename logic.

### 2.4.1.1 Structure

The mapping and checkpointing functions of the rename logic can be implemented in at least two ways. These two schemes, called the RAM scheme and the CAM scheme, are described next.

### **RAM** scheme

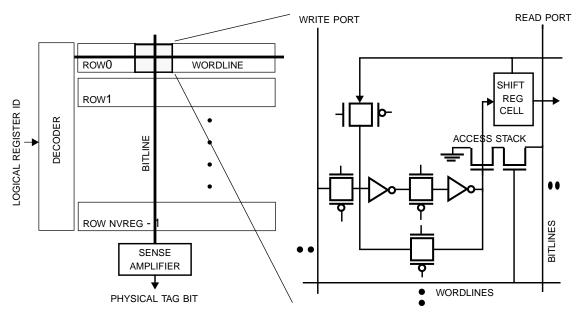

In the RAM scheme, as implemented in the MIPS R10000 [Yea96], the map table is a RAM where each entry contains the physical register that is mapped to the logical register whose designator is used to index the table. The number of entries in the map table is equal to the number of logical registers. A single cell of the table is shown in Figure 2-5. A shift register, present in every cell, is used for checkpointing old mappings.

The map table works like a register file. The bits of the physical register designators are stored in the cross-coupled inverters in each cell. A read operation starts with the logical register designator being applied to the decoder. The decoder decodes the logical register designator and raises one of the word lines. This triggers bit line changes which are sensed by a sense amplifier and the appropriate output is generated. Precharged, double-ended bit lines are used to improve the speed of read operations. Mappings are checkpointed by copying the current contents of each cell into the shift register. Recovery is performed by writing the bit in the appropriate shift register cell back into the main cell.

# CAM scheme

An alternative scheme for register renaming uses a CAM (content-addressable memory) to store the current mappings. Such a scheme is implemented in the HAL SPARC [AMG<sup>+</sup>95] and the DEC 21264 [Kel96]. The number of entries in the CAM is equal to the number of physical registers. Each entry contains two fields. The first field stores the logical register designator that is mapped to the physical register represented by the entry. The second field contains a valid bit that is set if the current mapping is valid. The valid bit is required because a single logical register designator might map to more than one physical register. When a mapping is changed, the logical register designator is written into the entry corresponding to a free physical register and the valid bit of the entry is set. At the same time, the valid bit used for the previous mapping is located through an associative search and cleared.

The rename operation in this scheme proceeds as follows. The CAM is associatively searched with the logical register designator. If there is a match and the valid bit is set, a read enable wordline corresponding to the CAM entry is activated. An encoder (ROM) is used to encode the read enable word lines (one per physical register) into a physical register designator. Old mappings are checkpointed by storing the valid bits from the CAM into a checkpoint RAM. To recover from an exception, the valid bits corresponding to the old mapping are loaded into the CAM from the checkpoint RAM. In the HAL design, up to 16 old mappings can be saved.

The CAM scheme is less scalable than the RAM scheme because the number of CAM entries, which is equal to the number of physical registers, increases with issue width. In order to support such a large number of physical registers, the CAM will have to be appropriately banked. On the other hand, in the RAM scheme, the number of entries in the map

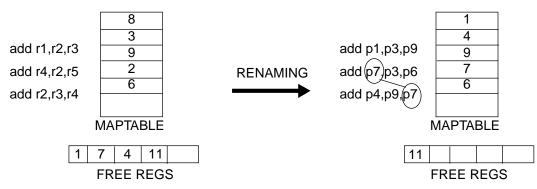

**Figure 2-4.** Renaming example showing dependency checking. The first entry of the map table corresponds to logical register r1.

table is independent of the number of physical registers. However, the CAM scheme has an advantage with respect to checkpointing. In order to checkpoint in the CAM scheme, only the valid bits have to be saved. This is easily implemented by having a RAM adjacent to the column of valid bits in the CAM. In other words, the dimensions of the individual CAM cells is independent of the number of checkpoints. On the other hand, in the RAM scheme, the width of individual cells is a function of the number of checkpoints because this number determines the length of the shift register in each cell.

The dependence check logic proceeds in parallel with the map table access. Every logical register designator being renamed is compared against the destination register designators (logical) of earlier instructions in the current rename group. If there is a match, then the tag corresponding to the physical register assigned to the earlier instruction is used instead of the tag read from the map table. For example, in the case shown in Figure 2-4, the last instruction's operand register r4 is mapped to p7 and not p2. In the case of more than one match, the tag corresponding to the latest (in dynamic order) match is used. We implemented the dependence check logic for issue widths of 2, 4, and 8. We found that for these issue widths, the delay of the dependence check logic is less than the delay of the map table, and hence the check can be hidden behind the map table access.

**Figure 2-5.** Rename map table. This figure shows the map table of the rename logic on the left and a single cell of the map table on the right.

### 2.4.1.2 Delay Analysis

We implemented both the RAM scheme and the CAM scheme. We found the performance of the two schemes to be comparable for the design space we explored. To keep the analysis short and since the RAM scheme is more scalable, we will only discuss the RAM scheme here.

A single cell of the map table is shown in Figure 2-5. The critical path for the rename logic is the time it takes for the bits of the physical register designator to be output after the logical register designator is applied to the address decoder. The delay of the critical path consists of three components: the time taken to decode the logical register designator, the time taken to drive the wordline, the time taken by an access stack to pull the bitline low plus the time taken by the sense amplifier to detect this bitline change and produce the corresponding output. The time taken for the output of the map table to pass through the MUX in Figure 2-3 is ignored because this is very small compared to the rest of the rename logic and, more importantly, the control input of the MUX is available in advance

because the dependence check logic is faster than the map table. Hence, the overall delay is given by,

$$Delay = T_{decode} + T_{wordline} + T_{bitline}$$

Each of the components is analyzed next.

### **Decoder delay**

The structure of the decoder is shown in Figure 2-6. We use predecoding to improve the speed of decoding. The predecode gates are 3-input NAND gates and the row decode gates are 3-input NOR gates. The output of the NAND gates is connected to the input of the NOR gates by the predecode lines. The length of these lines is given by,

$$PredeclineLength = (cellheight + 3 \times IW \times wordline_{spacing}) \times NVREG$$