## DYNAMIC INSTRUCTION REUSE

by

## AVINASH SODANI

A dissertation submitted in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

University of Wisconsin-Madison

2000

©opyright by A vinash Sodani 2000 All Rights Reserved

# Abstract

Traditionally, improvements in processor microarchitecture have come from observing program characteristics and devising mechanisms to exploit them. This thesis presents a new phenomenon exhibited by programs and proposes a novel microarchitectural technique for exploiting it to improve processor performance. The phenomenon, called *dynamic instruction repetition*, is that instructions in programs often execute repeatedly with the same input values and produce the same results over and over again. The new microarchitectural technique proposed in this thesis exploits this phenomenon to reduce the work that needs to be done in executing programs. This technique, called *dynamic instruction reuse*, detects that instructions are producing the same results repeatedly, and instead of re-executing them, reuses the results from the instructions' previous executions. This technique improves performance because of several reasons, one of which is its ability to collapse data dependences by completing dependent instructions simultaneously.

This thesis makes two main contributions:

- It studies the phenomenon of instruction repetition, presenting numerous characterization results and performing detailed analyses to better understand the causes of this phenomenon.

- 2. It introduces and studies the concept of dynamic instruction reuse. It presents four instruction reuse schemes. These schemes reuse results of instructions from a hardware table called the *Reuse Buffer (RB)*, where the results are stored previously. The validity of these

old results is established by checking whether the current operand values are the same as those used to calculate the old results. The thesis also studies the size and associativity requirements for the storage needed for saving instruction results, and presents four new policies for managing this storage efficiently. Finally, this thesis studies the interactions of instruction reuse with other key microarchitectural features in processors.

The experimental results show that there is abundant instruction repetition in programs, and that significant percentage of this repetition can be reused. Although the resultant performance improvements are not commensurately high, they are still significant in many cases.

# Acknowledgements

I would like to thank my advisor, Guri Sohi, for his guidance and support during my graduate studies, and for the invaluable training I received as his student. His influence is sure to stay with me for a long time and help me in my career in many ways. As his student, I also cherished the freedom he offered to explore and develop new ideas. This freedom kept my interest alive in my research all through out the Ph.D.

I would like to thank Mark Hill, Jim Goodman, Charles Fischer, Jim Smith, and David Wood for serving on my preliminary and defense committees. Their incisive evaluation of my work helped me focus my research in the correct direction. Mark Hill and Jim Goodman also severed as readers for this thesis. This thesis benefitted immensely from their efforts.

Many people helped me during my years in graduate school. Andy Glew, Andreas Moshovos, Shubu Mukherjee, and T.N. Vijaykumar were always willing to offer advice. I also learnt a lot about making good talk slides from Andreas. It was a pleasure sharing an office with Andy. The numerous discussions I had with him on variety of topics helped me develop a better appreciation for fields beyond computers.

This thesis work would not have been possible without the love, support, and constant encouragement from my family. The immense pride that my parents and brothers take in my smallest of achievements was a constant source of motivation. My wife Shilpa cheerfully put up with my spending countless hours at work. It was her love and support that made the final and, arguably, the most strenuous year of graduate school much easier to withstand.

# Contents

| Abstract . | i                                                 |

|------------|---------------------------------------------------|

| Acknowle   | dgements                                          |

| Chapter 1  | . Introduction                                    |

| 1.1 S      | cenarios for Instruction Repetition and Reuse     |

| 1.1        | .1 Scenario 1: Squash Repetition and Reuse        |

| 1.1        | 2 Scenario 2: General Repetition and Reuse        |

| 1.2 T      | hesis Contributions                               |

| 1.2        | .1 Instruction repetition                         |

| 1.2        | 2 Instruction Reuse                               |

| 1.3 R      | elated Work                                       |

| 1.4 T      | hesis Outline                                     |

| Chapter 2  | . Experimental Framework17                        |

| 2.1 S      | imulators                                         |

| 2.1        | .1 Functional simulator                           |

| 2.1        | 2 Timing simulator                                |

| 2.2 P      | rocessor Microarchitecture                        |

| 2.3 B      | enchmarks                                         |

| 2.3        | 1 Description                                     |

| 2.3        | 2 Compilation                                     |

| 2.3        | 3 Execution                                       |

| Chapter 3  | . An Empirical Analysis of Instruction Repetition |

| 3.1 Q      | Pualitative Description of Causes of Repetition   |

| 3.2 Q      | uantitative Analyses: Introduction and Rationale  |

| 3.3 D      | Pefinitions                                       |

|    | 3.4  | Expe  | erimental Setup                                                   |

|----|------|-------|-------------------------------------------------------------------|

|    | 3.5  | Stati | stical Analysis: Characterizing Instruction Repetition            |

|    | 3.6  | Ana   | lysis to Understand the Causes of Repetition                      |

|    |      | 3.6.1 | Global Analysis                                                   |

|    | -    | 3.6.2 | Function Level Analysis                                           |

|    |      | 3.6.3 | Local Analysis                                                    |

|    | 3.7  | Disc  | ussion and Further Investigations                                 |

|    |      | 3.7.1 | Global Analysis                                                   |

|    |      | 3.7.2 | Function Level Analysis                                           |

|    | -    | 3.7.3 | Local Analysis                                                    |

|    | 3.8  | Sum   | mary and Conclusions                                              |

| Ch | apte | r 4.  | Dynamic Instruction Reuse77                                       |

|    | 4.1  | Instr | ruction Reuse                                                     |

|    | 4.2  | Reus  | se Buffer                                                         |

|    | 4.3  | Sche  | emes for Instruction Reuse                                        |

|    | 2    | 4.3.1 | Scheme Sv: Reuse based upon operand values                        |

|    | 2    | 4.3.2 | Scheme Sn: Reuse based upon register names                        |

|    | 4    | 4.3.3 | Scheme Sn+d: Reuse using register names and dependence chains 85  |

|    | 4    | 4.3.4 | Scheme Sv+d: Reuse using register values and dependence chains 89 |

|    | 4    | 4.3.5 | Summary of schemes                                                |

|    | 4.4  | Mici  | roarchitecture with a Reuse Buffer                                |

|    | 4.5  | Reus  | se Schemes: Optimizations, Constraints and Variations             |

|    | 4    | 4.5.1 | Optimizations                                                     |

|    | 2    | 4.5.2 | Constraints                                                       |

|    | 4    | 4.5.3 | Variations                                                        |

|    | 4.6  | Inva  | lidations in RB: Issues and Alternatives                          |

|    | 4    | 4.6.1 | Non-load invalidations                                            |

|    | 4    | 4.6.2 | Dependent instruction invalidations                               |

|    | 4.7  | Expe  | erimental Evaluation                                              |

v

|        | 4.7.1 | Experiments and Results                                   |

|--------|-------|-----------------------------------------------------------|

| 4.8    | Rela  | ated Work and Discussion                                  |

| 4.9    | Sun   | nmary and Conclusions                                     |

| Chapte | er 5. | Reuse Buffer Characterization and Management              |

| 5.1    | Exp   | erimental Setup                                           |

| 5.2    | Cha   | racterizing RB: Size                                      |

| 5.3    | Cha   | racterizing RB: Associativity                             |

|        | 5.3.1 | Effect of storing multiple instances in RB on reuse rates |

|        | 5.3.2 | Overall effect of associativity on reuse rates            |

| 5.4    | RB    | Management                                                |

|        | 5.4.1 | Insertion Policy                                          |

|        | 5.4.2 | Replacement Policy                                        |

|        | 5.4.3 | FiF: Farthest in Future Replacement Policy                |

| 5.5    | Eva   | luation of Management Policies                            |

|        | 5.5.1 | Direct measures of policy operation                       |

|        | 5.5.2 | Stability of distances in FiF 164                         |

|        | 5.5.3 | Reuse Rates                                               |

|        | 5.5.4 | Performance                                               |

| 5.6    | Sun   | nmary and Conclusions                                     |

| Chapte | er 6. | Sensitivity Analysis                                      |

| 6.1    | Exp   | erimental Setup                                           |

| 6.2    | Cau   | ses for Sensitivity of IR                                 |

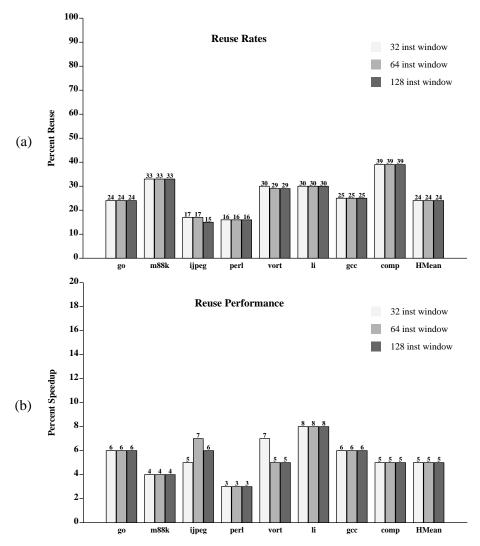

| 6.3    | Inst  | ruction Window Size                                       |

|        | 6.3.1 | Possible impacts on reuse rates                           |

|        | 6.3.2 | Possible impact on reuse performance                      |

|        | 6.3.3 | Results                                                   |

| 6.4    | Pipe  | eline Width                                               |

|        | 6.4.1 | Possible impact on reuse rates                            |

|        | 6.4.2 | Possible impact on reuse performance                      |

vi

|            |                                          | vii |

|------------|------------------------------------------|-----|

| 6.4.3      | Results                                  |     |

| 6.5 Pip    | beline Length                            |     |

| 6.5.1      | Possible impact on reuse rates           |     |

| 6.5.2      | Possible impact on reuse performance     |     |

| 6.5.3      | Results                                  |     |

| 6.6 Br     | anch Prediction                          |     |

| 6.6.1      | Possible impact on reuse rates 193       |     |

| 6.6.2      | Possible impact on reuse performance 194 |     |

| 6.6.3      | Results                                  |     |

| 6.7 Me     | emory Latency                            |     |

| 6.7.1      | Possible impact on reuse rates           |     |

| 6.7.2      | Possible impact on reuse performance 198 |     |

| 6.7.3      | Results                                  |     |

| 6.8 Re     | use Latency                              |     |

| 6.8.1      | Pipeline with reuse latency              |     |

| 6.8.2      | Possible impact on reuse rates           |     |

| 6.8.3      | Possible impact on reuse performance     |     |

| 6.8.4      | Results                                  |     |

| 6.9 Su     | mmary and Conclusions                    |     |

| Chapter 7. | Conclusions                              |     |

| 7.1 Th     | esis Summary                             |     |

| 7.1.1      | Analysis of Instruction Repetition       |     |

| 7.1.2      | Instruction Reuse                        |     |

| 7.2 Fu     | ture Work                                |     |

| 7.2.1      | Reuse at higher granularity              |     |

| 7.2.2      | Compiler support for reuse               |     |

| 7.2.3      | Low power                                |     |

| 7.2.4      | Other uses of IR                         |     |

| 7.2.5      | Further developing the FiF policy        |     |

| Bibliography |                    |     | viii |

|--------------|--------------------|-----|------|

| Appendix A.  | Additional Results | 227 |      |

# Chapter 1

# Introduction

Over the past decade, microprocessors have become immensely powerful. This growth in performance has been made possible not only by improvements in semiconductor technology (resulting in higher clock frequencies) but also by advancements in the processor microarchitecture (resulting in more work performed per clock cycle). With computers becoming ubiquitous and the way increasingly complex tasks being entrusted upon them, the need for faster processors is likely to grow unabated in the near future. To satisfy this requirement, it is important not only to improve the semiconductor technology, but also to innovate in the field of microarchitecture.

Microarchitectural innovations are often inspired by commonly observed behavior of programs. Designers have frequently introduced new microarchitectural features for exploiting patterns in program behavior to improve processor performance. Some examples of commonplace microarchitectural features in modern processors that exploit program behavior are caches, branch prediction, and the out-of-order execution paradigm. These features exploit different traits in programs and, hence, improve processor performance in different ways. Caches exploit locality of memory references, a property exhibited by most programs, to reduce memory access time. Branch prediction exploits regularity in branching behavior, another property exhibited by programs, to streamline instruction-fetch. The out-of-order execution paradigm exploits the presence of significant amounts of instructions-level parallelism in programs to hide the latency of long-running operations. Thus, as shown by these example, the knowledge of program characteristics is central to improving processor microarchitecture. To further improve processor microarchitecture, we need to seek out new program characteristics and devise mechanisms to exploit them.

In this thesis, we present a new phenomenon exhibited by programs and propose a novel microarchitectural technique for exploiting this phenomenon to improve processor performance. The phenomenon is that in programs, instructions often execute repeatedly with the same inputs and, therefore, produce the same results over and over again. That is, if an instruction executes with operand values v1 and v2 and produces an output v3, then during program execution this instruction may execute with v1 and v2 as inputs and produce v3 as output many times. We call this phenomenon dynamic instruction repetition, or simply, instruction repetition.

The microarchitectural technique that we propose exploits this phenomenon to reduce the amount of work that needs to be done for executing a program. This technique detects that instructions are producing the same results repeatedly, and instead of re-executing them, reuses the results from their previous executions. The repetition is detected by ascertaining that the current operand values of the instructions are the same as those used to compute the previous results. We call this technique *dynamic instruction reuse*, or simply, *instruction reuse*.

What are the benefits of reusing instructions? There are several. First, a reused instruction need not be executed. Hence, the pipeline resources (e.g., issue window entry, functional

units, data cache ports) that would have been used for its execution can now be used for processing other waiting instructions. Second, when an instruction is reused, its results become known earlier than they would have through regular execution. This permits other instructions that are dependent on these results to execute sooner. Third, as we shall illustrate shortly, this mechanism allows useful work to be salvaged from the work that is discarded due to misspeculation in processors. This helps alleviate the penalty of such mis-speculations. Fourth, reuse collapses data dependences: dependent instructions, which would normally execute sequentially, can be reused in parallel. Hence, reuse has the potential to break the dataflow limits on the execution times of instructions.

In this thesis, we study the phenomenon of instruction repetition and develop the instruction reuse technique for exploiting it. We present an overview of the contributions of this thesis in Section 1.2. However, before that, to develop a better feel for instruction repetition, we illustrate why this phenomenon occurs, in the next section. In Section 1.3, we describe the related work, and finally, in Section 1.4, we conclude this chapter by presenting the outline of the rest of the thesis.

## **1.1 Scenarios for Instruction Repetition and Reuse**

Instructions get repeated because of two main reasons: (i) speculative execution, and (ii) the nature of the program itself. We present two scenarios to illustrate these reasons below. In each example, we also mention how exploiting that form of repetition may improve performance.

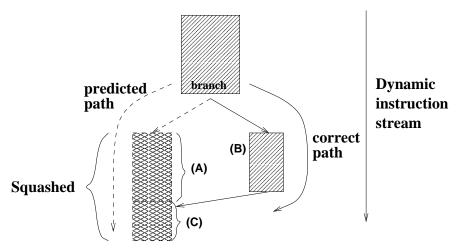

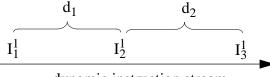

Figure 1.1 Scenario where execution on the (mis)predicted path converges with the execution on the correct path. In such cases certain instructions from part (C) need not be re-executed when encountered on the correct path.

### 1.1.1 Scenario 1: Squash Repetition and Reuse

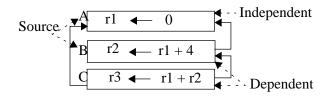

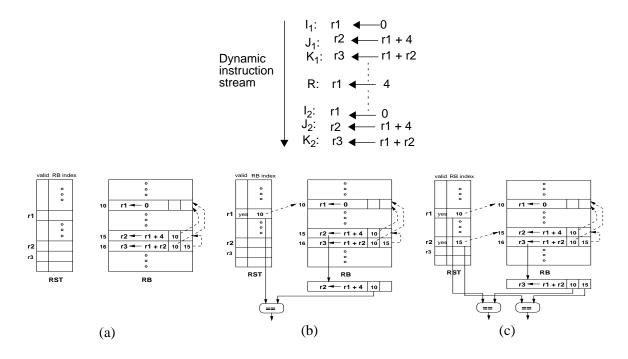

**Squash Repetition:** In the first scenario, the instructions are repeated because of the speculative execution of programs. When executing instructions speculatively, processors discard executed instructions on mis-speculations. These discarded instructions are sometimes executed again, resulting in repetition. For example, consider the scenario shown in Figure 1.1. When a branch instruction is encountered, its outcome is predicted, and instructions from the predicted basic block (block A) are executed speculatively. In addition to executing instructions from block A, the processor may execute instructions from another block (C), which is control independent of the branch. If the branch were mispredicted, instructions executed from both blocks A and C would be discarded, and execution would resume at block B, from where it would proceed to block C. Instructions in block C that were discarded, but whose operands are not affected by instructions in either blocks A or B, would end up being *repeated*. Since this repetition is engendered by squashes, we term it as *squash repetition*. **Squash Reuse:** In the above example, if results of the instructions in block C were buffered, then they could be reused after detecting that their operands are the same as at the time of the first execution. Since this reuse is enabled by squash repetition, we call it *squash reuse*.

**Benefits:** This form of reuse alleviates the mis-speculation penalty, but to understand why, we need to see what constitutes the mis-speculation penalty. The mis-speculation penalty consists of two components: (i) the cycles that are wasted executing instruction on the wrong path, and (ii) the cycles that are spent filling up the pipeline after the squash. Squash reuse alleviates both these components as follows. First, since it reuses work that was performed on the wrong path, not all cycles used in executing the discarded instructions are wasted. Second, when the reuse takes place just after the squash, it hides the pipeline-fill latency for the reused instructions, alleviating the second component.

### **1.1.2 Scenario 2: General Repetition and Reuse**

**General Repetition<sup>1</sup>:** In this scenario, repetition occurs because of the very nature of programs — *i.e.*, because of the way programs are written. To understand this statement, let us consider two practices pervasively employed while writing programs and see how they may generate instruction repetition. First, we write programs to be *generic* in nature — *i.e.*, we don't write them for fixed input values; rather, we write them so that they are capable of operating on a variety of input values. But, if during execution, the program encounters the same

<sup>1.</sup> An anecdote: Our initial purpose for coming up with the instruction reuse technique was to reduce the branch mis-prediction penalty by recovering useful work from squashes. The fact that instructions are repeated in general was discovered, quite serendipitously, while we were studying the reuse techniques for the above purpose. In fact, after discovering that many non-squashed instructions also get repeated, I actually spent a considerable amount of time trying to filter out these "unwarranted" repetition to stop them from clouding the squash reuse results!

inputs values repeatedly (e.g., the same keywords in *gcc* or the same letters in *compress*) then it is likely that the instructions within the program will also execute with the same input values repeatedly. This will result in repetition of instructions. Second, we express computation in programs in a *concise* manner. That is, if we have to perform an operation on an array, we don't write a separate statement for each element of the array; instead, we express the task using a loop, where each iteration performs the operation on a single (or a small number) of array elements. To allow computation to be expressed in this manner, we need to include the loop-control instructions (instructions that will "unroll" the computation dynamically) with each loop. These loop-control instructions may be repeated (along with other dependent instructions) when the loop is invoked repeatedly. (This repetition may occur even when the loop body may be performing a totally different computation).

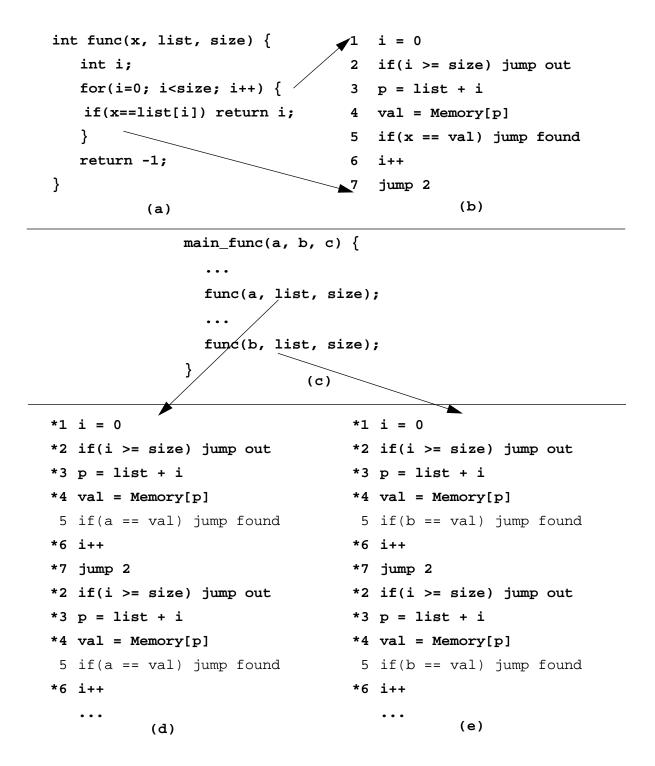

We illustrate the above situation with an example shown in Figure 1.2. In this example, the function func searches for a value x in a list of a particular size. The function main\_func calls func several times, searching for a different element in the same list with each call. When func is called, it iterates through the list, element by element, searching for the value until the end of the list, and exits when the value is found. Instructions corresponding to the loop in func are shown in Figure 1.2(b). Figure 1.2(d) shows the dynamic instances of these instructions which are generated by the first call to func. In each iteration of the loop, instruction 2 is dependent upon the size parameter, instructions 3 and 4 are dependent upon the list parameter, instruction 5 is dependent upon the list as well as the value being searched for, and instruction 6 is dependent on the induction variable. If func is called again (Figure 1.2(e)) on the same list (and same size), but with a different search

Figure 1.2 Example illustrating that often times instructions perform the same computation over and over again. The dynamic instructions marked "\*" would perform the same computation for both the calls to function func shown in the figure.

key, then all the different dynamic instances of instructions 1-4 and 6 will produce the same outcomes as they did the previous time the function was called.<sup>2</sup> Only the dynamic instances of instruction 5 produce results that might differ from the previous call to func. This *repetition* of the results of the dynamic instances of instructions 1-4 and 6 is directly attributable to the fact that func was written to be a generic list search function, but in this particular case, only one of its parameters changed between different calls to it. Even if func was called with all its parameters being different for each call, the different dynamic instances of the instruction 6 (i=0, i=1, i=2, ...) in the second call to func would end up producing the same values as they did in the first call to func, a consequence of using loops to express the desired computation in a concise manner. (Actually, if the size parameter was also different, then only min(sizel, size2) dynamic instances of instruction 6 would produce the same values.).

Since, the form of repetition as exemplified above occurs because of the general nature of programs, we call it *general repetition*.

**General Reuse:** In the above example, if we buffered the (size) dynamic instances of instructions 1-4 and 6, we will be able to reuse them when they get repeated. This form of reuse that is enabled by general repetition, we call *general reuse*.

**Benefits:** To see how the performance might benefit from general reuse, let us consider the advantages of reusing instances of instructions 1-4 and 6 in the above example. First, the dynamic instances of instructions 1-4 and 6 do not have to pass through all the different phases of execution (ALU, result bus, register write, etc.), thereby reducing the demand for processor resources. (In the above case, accesses to the data cache are also eliminated — these

<sup>2.</sup> a total of size dynamic instances of instructions 2-4 and 6

end up becoming accesses to the buffer which holds previous instruction results.) Second, the critical path to carry out the total computation involved in func can be cut down considerably. Without dynamic instruction reuse, the critical path through the computation, as expressed above, would be size+3 steps, size steps to generate all the dynamic instances for the induction variable i, plus 3 steps to executed instructions 3, 4, and 5 of each iteration (which form a dependence chain). In other words, the height of the dataflow graph for the above computation is size+3 steps. In the best case, the critical path, *i.e.*, the height of the dataflow graph through the computation, is reduced to only 1 step with instruction reuse. This is because the outcomes of all the dynamic instances of instructions 1-4 are already known, and all the dynamic instances, being independent of one another, could all execute at the same time. Although, in practice, the available buffer space would place a limit on how much of the computation can be collapsed, the above example goes to show the potential that instruction reuse has for breaking the dataflow limit "inherent" in programs.

## **1.2 Thesis Contributions**

In this thesis, we make two main contributions: (i) we study the phenomenon of instruction repetition; and (ii) we introduce and study the concept of dynamic instruction reuse. Each of these contributions are elaborated below.

### **1.2.1 Instruction repetition**

We perform an elaborate study of the phenomenon of instruction repetition. The purpose is to develop a better understanding of the phenomenon, so that we can exploit it effectively. The study consists of two parts. In the first part, we perform a thorough characterization of the phenomenon. Here we answer questions such as what percentage of all dynamic instructions get repeated, what percentage of all static instructions generate repeated instances, what fraction of static and dynamic instructions account for most of the repetition, and so on.

Although the above characterization gives us various statistical facts about the phenomenon, it does not provide us with much insight into its causes. In the second part of the study, we perform an empirical analysis of the phenomenon to better understand what may be causing it. For this purpose, we categorize the instructions in programs based on the type of data used (e.g., external input, internal data) and the type of work performed (e.g., address calculations, function prologue and epilogue), and then determine the amount of instruction repetition arising for each category. This breakdown gives us an idea about the primary sources of repetition, and thereby, its causes.

We draw numerous observations from our results. Of these, two are especially interesting. First, we observe that the phenomenon of instruction repetition is pervasive — more that 75% of dynamic instructions are repeated for several benchmarks. Second, we see that for most benchmarks, the majority of the repeated instructions use data that originate from within the program itself rather than from external inputs. This observation suggests that the phenomenon of instruction repetition may be more a property of the program itself than of input data.

### **1.2.2 Instruction Reuse**

The second and the main contribution of this thesis is the concept of instruction reuse — *i.e.*, the idea that the previous work by instructions can be non-speculatively reused when they perform the same work again. The bulk of this thesis is devoted to developing and understand-

ing this concept. The work on instruction reuse can be divided into three categories: (i) devising and studying reuse schemes; (ii) studying the storage issues for instruction reuse; and (iii) investigating the sensitivity of instruction reuse performance to other microarchitectural features existent in processors. We elaborate next on each of these categories.

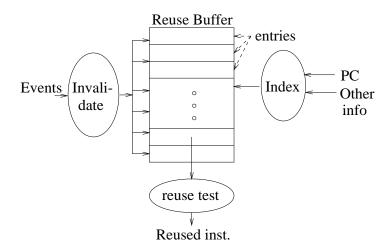

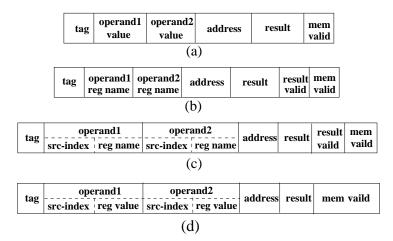

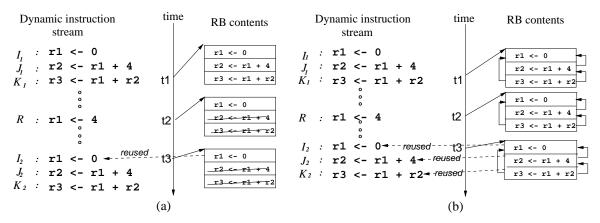

#### 1.2.2.1 Instruction reuse schemes

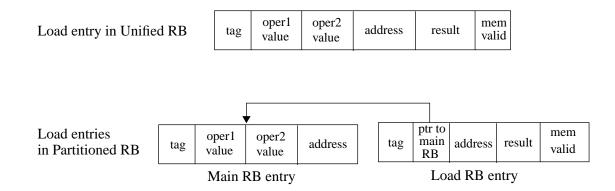

We present four schemes for implementing instruction reuse. These schemes preserve results of instructions (along with other information needed to establish their validity at a later time) in a hardware table called the *Reuse Buffer (RB)*. When an instruction is encountered again, its results from RB are reused if they are still valid. The validity of the results is established by checking whether the current operand values are same as those used to calculate the results. The four schemes differ in the type of information they use to establish the sameness of operands. The scheme  $S_v$  uses operand values; the scheme  $S_n$  uses operand names; and the schemes  $S_{v+d}$  and  $S_{n+d}$  use the dependence between instructions, along with the operand values and operand names, respectively. The use of dependence information facilitates the reuse of dependent chain of instructions.

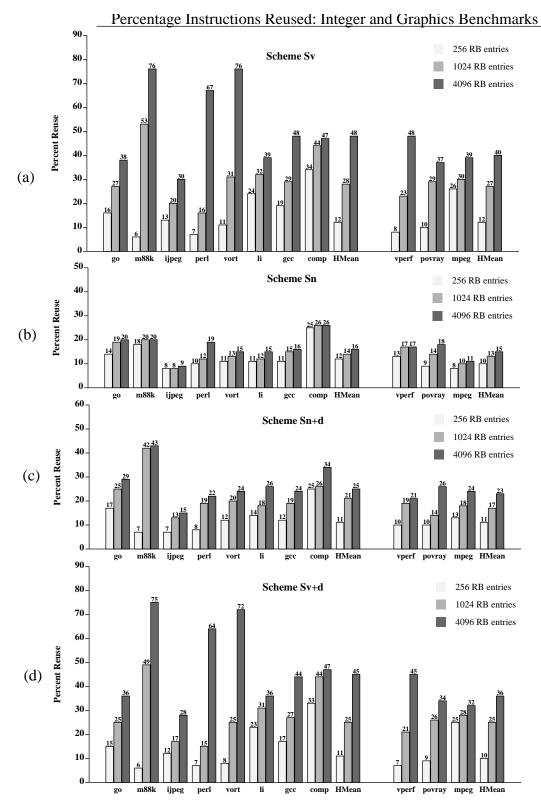

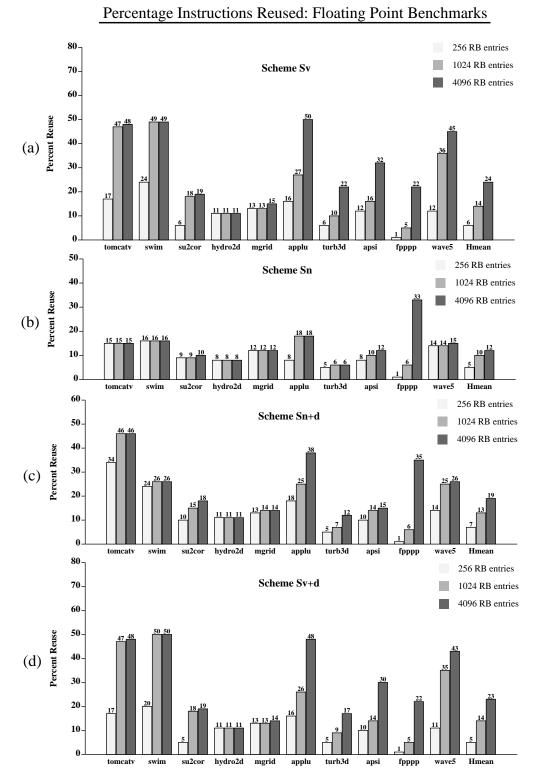

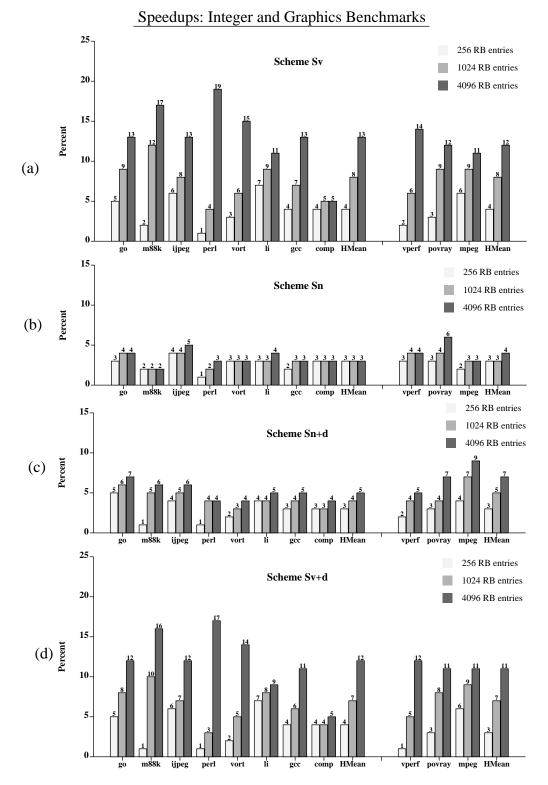

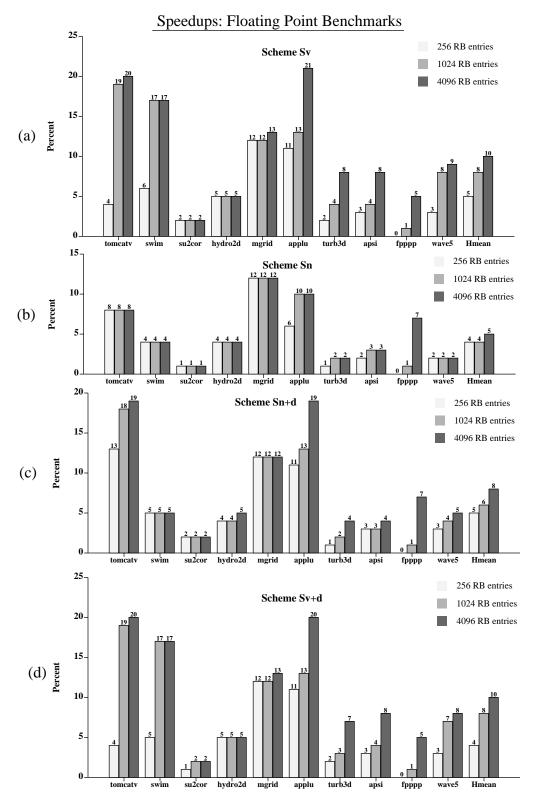

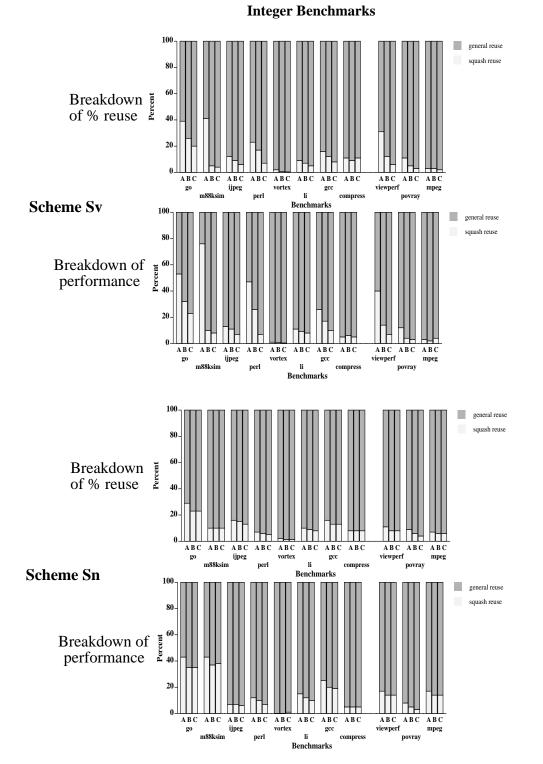

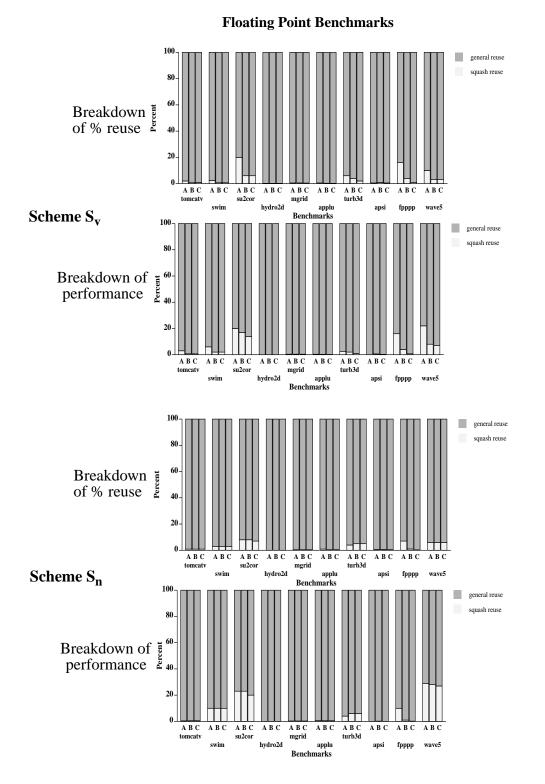

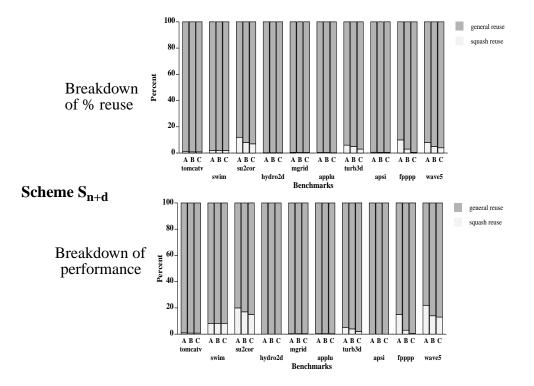

We evaluate the concept of instruction reuse with extensive simulations. We present results such as the number of instructions reused and the amount of performance gained by reuse. We show reuse characteristics such as the reusability of different instruction types and the contribution of different instruction types to total reuse. We also present a break down of total reuse into general and squash reuse. Our results show that a significant percentage of dynamic instructions in programs get reused, with more than 50% of dynamic instructions getting reused in several cases, and that the performance improvement due to reuse is also significant for several benchmarks, being more than 15% in many cases.

#### 1.2.2.2 Storage issues for instruction reuse

One important part of the instruction reuse technique is the RB, which stores the results of instructions. To a large extent, the number of instructions that can be reused depends on how many valid results the RB can hold. We conduct a detailed study to better understand the requirements of this structure. This study is divided into two parts. First, we characterize the RB with respect to its three main parameters: size, associativity, and management policies. We present how the amount of instructions reused varies with each of these parameters. We present the maximum reuse rates, obtained using a management policy similar to the Belady's optimal management policy, for a range of RB sizes and associativities. This optimal numbers give us an upper bound on the reuse rates for different RB sizes and associativities — or, alternatively, tells us the minimum RB size and associativity required to capture a certain amount of reuse.

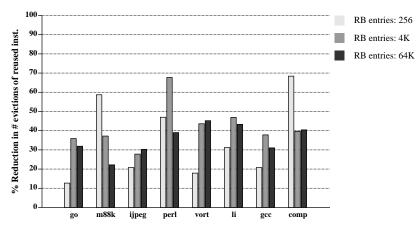

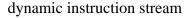

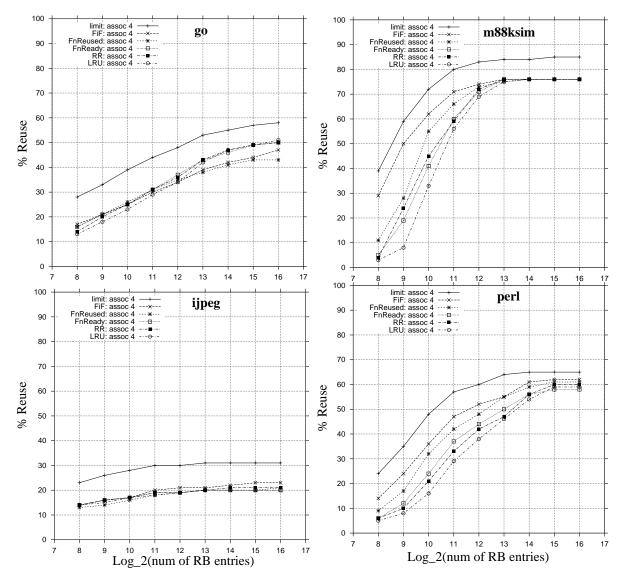

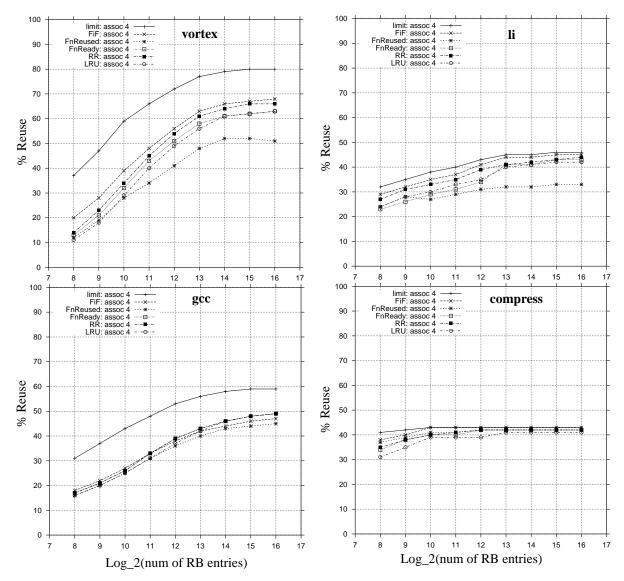

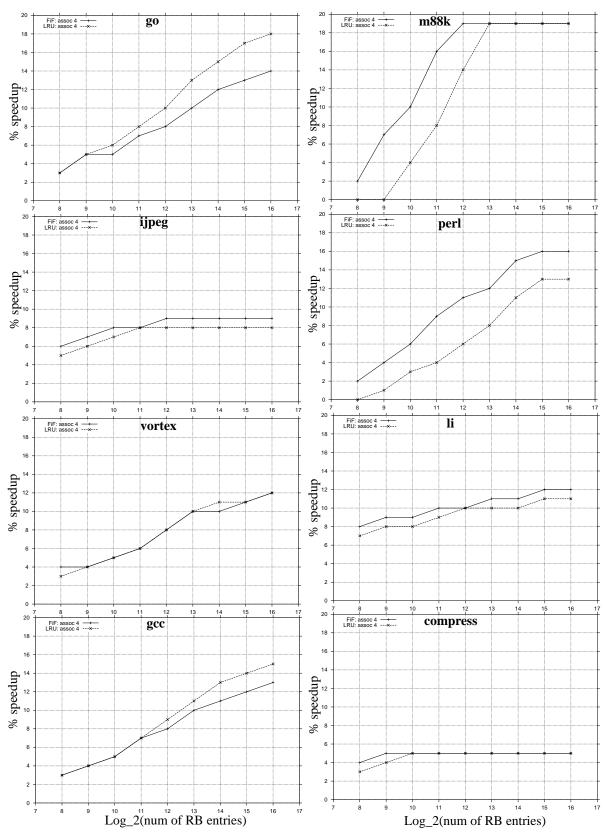

The second part of this study is motivated by the results of the first part, which show that a significant gap exists between the optimal and the actual reuse rates. This gap indicates that there is potential to improve the reuse rate further by efficient management of the RB. To bridge this gap, we devise and study four management policies for managing the RB efficiently. Two of these polices, *FnReused* and *FnReady*, attempt to improve RB utilization by controlling insertions in RB — *i.e.*, by inserting only the likely reusable instructions. The third policy, *RR*, attempts to improve RB utilization by controlling eviction from RB — *i.e.*, by evicting the likely unreusable instructions before the reusable ones. The fourth policy, a novel management policy called *Farthest in Future (FiF)*, attempts to improve RB utilization by

managing it along the lines of the Belady's optimal management policy. This policy determines how far in the future each instruction is likely to get reused. The RB is then managed by scheduling instructions in it using this distance-to-reuse information, giving priority to the instructions that have shorter distance values. The FiF is a general management policy that can also be used for managing other forms of storage, e.g., caches; however, in this thesis, we only use the FiF for managing the RB, leaving the task of evaluating it for other storage structures as future work.

The success of these new policies in improving RB utilization is mixed. For some benchmarks, we see a significant improvement (over the existing policies) in reuse rates using the new policies; for others the improvements with the new policies are small (or slightly negative). Due to its general nature, the FiF policy performs better than other policies in most cases. However, policies FnReady and RR may be comparatively inexpensive to implement, and, hence, the improvements in reuse rates caused by them may be noteworthy.

#### 1.2.2.3 Sensitivity analysis

It is important to not only study how a new microarchitectural technique performs by itself, but also to understand how it interacts with other microarchitectural features. To cultivate such an understanding for instruction reuse, we study its sensitivity to various key processor parameters, such as (i) instruction window size, (ii) pipeline width, (iii) pipeline length, (iv) branch prediction accuracy, (v) memory latency, and (vi) reuse latency. This study consists of two parts. In the first part, we first present a detailed qualitative discussion on how and why instruction reuse may be sensitive to each of the parameters. In the second part, we present several simulation results to provide a quantitative measurement of the amount of sensitivity.

## **1.3 Related Work**

The idea of not having to redo computation is not new — it has been used before in several different contexts. A technique called *memoization* [29, 5, 8] has been used for functional and logic programs [47, 30]. The outcome of a function (or a rule) is saved in a table. If the function or the rule is encountered again with the same parameters then the result from the table is used instead of re-evaluation. Memoization is also used to reduce the running time of optimizing compilers, where the same data dependence test is carried out repeatedly.

The observation that the instructions produce the same results repeatedly and that this phenomenon is widespread in ordinary programs has been made more recently by several researchers. Lipasti et al. [27, 26] observed that many instructions produce the same values as their last instance (or last few instances). They termed this recurrence of instruction results as value locality. Similar results were also reported by Mendelson and Gabbay [18, 19]. The phenomenon of instruction repetition — where not only the results but also the instruction operands are repeated — was first reported by us [43] (although the phenomenon was not termed as such in that paper).

Several researchers have studied the repetition of values elaborately. The study that we will present later in this thesis was first reported in [44]. Calder et al. [12] presented several statistical results on this phenomenon. Sazeides and Smith [40] tracked the creation, propagation, and termination of value locality in to better understand its causes.

Many ways of exploiting this phenomenon have also been proposed. Several researchers

[27, 26, 19, 39, 48] have suggested exploiting this phenomenon for predicting results of instructions in advance and performing dependent computation in parallel. We propose exploiting this phenomenon for reducing the amount of work that needs to be performed for executing instructions using instruction reuse technique. This technique was first reported by us in [43]. In the software arena, researchers have proposed exploiting this phenomenon using dynamic software optimizations, such as function memoization and code specializations [6, 17, 21], and static compiler optimizations, such as partial redundancy elimination [32, 10, 9].

Several researchers have performed work [23, 36, 37, 34] that is related to our method of exploitation. This prior work presents different techniques that obviate re-execution of repeating instructions by reusing their previous results. However, there are several important differences between our technique and theirs in terms of, for example, the ability to collapse the chain of dependent instructions or the type of instructions targeted. However, these differences and the mechanics of these techniques themselves can be best understood after we discuss the details of our technique. Hence, we defer the discussion on this subject until the *Related Work* section in Chapter 4.

Since our initial publication of the concept of instruction reuse [43], significant amount of work has been done in this area. The reuse concept has been extended to basic-block level [24] and trace-level [20]. Molina et al. [31] extended the instruction reuse technique to do computation reuse, *i.e.*, reuse of work done by other static instructions. Chou et al. [14] studied a different microarchitecture technique for performing squash reuse. Connors and Hwu [16] studied how compiler assistance can be used for reusing large regions of code. Reusability of instructions in other application domains, such as multi-media, has also been studied [15].

## **1.4 Thesis Outline**

The rest of the thesis is laid out as follows. In Chapter 2, we describe our experimental framework. In Chapter 3, we present an empirical analysis of the phenomenon of instruction repetition. In Chapter 4, we present the instruction reuse technique. In Chapter 5, we present a characterization of the RB and study policies to manage it efficiently. In Chapter 6, we study the sensitivity of instruction reuse to other microarchitectural features. Finally, in Chapter 7, we summarize this thesis and provide directions for future work.

# Chapter 2

# **Experimental Framework**

In this chapter, we describe the experimental framework used in this thesis. All our experiments are performed using two processor simulators. We describe these simulators in the next section and mention the types of experiments for which they are used. Then, in Section 2.2, we describe the base processor microarchitecture that we simulate. Finally, in Section 2.3, we describe our suite of benchmarks and present some of their execution characteristics.

## 2.1 Simulators

The experiments in this thesis can be divided broadly into two categories: (i) one that studies program behavior and program structure for understanding instruction repetition (performed in Chapter 3); and (ii) the other that evaluates and studies the technique of instruction reuse (performed in Chapters 4 to 6). For each of these categories, we use a different type of simulator: a *functional* simulator for the former and a *timing* simulator for the latter. Both of these simulators are written in C, using several components from a preliminary version of the now publicly available *Simplescalar* toolset [11]. These simulators are execution-driven and they interpret an instruction-set derived from the MIPS-1 ISA [25]. We describe these simulators and their purpose in greater detail next.

### 2.1.1 Functional simulator

The functional simulator only models the architectural behavior of the processor at instruction level — *i.e.*, it simply reads and executes the instructions from the program binary (without modelling any microarchitectural details or any execution times).

This simulator is used for several purposes in our studies. As mentioned before, we use it in Chapter 3 for analyzing the dynamic behavior of programs — collecting various run-time statistics and tracking different sources of dynamic repetition. We also use the functional simulator in several other ways, such as, verifying the timing simulator on-the-fly, implementing perfect branch prediction, and skipping initial parts of the benchmarks during timing simulations; we discuss more about these uses later in this chapter.

### 2.1.2 Timing simulator

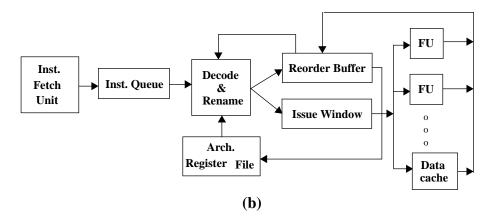

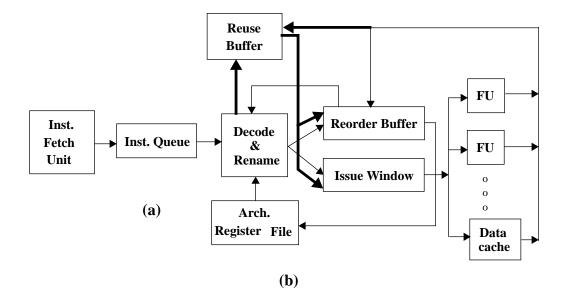

The timing simulator is used to evaluate and study the Instruction Reuse (IR) technique. This simulator models the microarchitectural behavior of an out-of-order, superscalar processor (shown in Figure 2.1) at the cycle-by-cycle level.

We developed the simulator for the out-of-order engine and the IR technique. These two components were then integrated with many other supporting components from the Simples-calar toolset — e.g., loader, memory-module, cache-module, branch predictors, and syscall-module — to give us a complete simulator. The design of the out-of-order simulator was influenced by the required support for IR. As we will see in Chapter 4, IR interacts with several parts of the pipeline. So that we can simulate these interactions faithfully, we model the base pipeline faithfully: instructions (and values) flow through the pipeline cycle-by-cycle and the various micro-operations are performed in appropriate pipe-stages (we do not fake them).

Also, to study squash reuse, we model the speculative execution and mis-speculation recovery faithfully: the processor is allowed to execute down the mispredicted path until the misprediction is detected and then the recovery is made by squashing the pipeline, just as it would be in a real pipeline.

For some experiments in Chapter 6, we require a perfect branch predictor — *i.e.*, a predictor that predicts all branches correctly. We implement the perfect branch predictor using the functional simulator. This simulator executes instructions before they enter the timing simulator, generating their results — and, hence, the branch results (when these instructions are branches) — in advance. We simulate perfect branch prediction by using the branch result generated ahead of time as predictions.

We also use the functional simulator to validate the timing simulator on-the-fly. Since the timing simulator is much more complex than the functional simulator, it is more susceptible to errors than the latter. Sometimes, these errors may cause the timing simulator to generate incorrect results. We detect such errors with the help of the functional simulator as follows. We run the timing and the functional simulator simultaneously. Every instruction that emerges from the timing simulator pipeline is executed on the functional simulator, and the results obtained from the timing simulator are compared with those obtained from the functional simulator are different.

The above validation only verifies the functional correctness of the timing simulator; it does not verify its timing correctness. Verifying that the timing results are correct is a hard problem, and there is no straightforward way of doing so. We take several steps to ensure that the timing results of our simulator are consistent:

• During the process of writing the simulator, we used several self-constructed micro-

benchmarks for testing the behavior of the pipeline. Most of the micro-benchmarks were strings of 5 to 10 instructions, which were generated manually, and injected into the pipeline. This approach allowed us to verify that the flow of instructions through the pipeline was as would be expected from the dependences between them. This was helpful in validating the various pipeline interactions.

- In our simulator, we have several independent counters that count different events during execution (e.g., the number of instructions executed, the number of instruction squashed, etc.). We placed several *assertions* in our simulators to check the various invariances that can be derived from these counters, such as,

- # instr executed # executed instr squashed = # instr committed + # executed instr in pipeline

# loads from D-cache + # loads satisfied by stores in store-buffer # executed load squashed

= # loads committed + # executed load in the pipeline

These invariances were checked every cycle. They helped link the different parts of the simulator, and ensured that changes made in one part were consistent with other parts. These invariances were especially useful in catching inconsistencies introduced due to fresh changes to the simulator.

• In our simulator, instructions actually flow through the pipeline; we do not fake the process. Such a design helps uncover many timing (or interaction) errors since it reduces the number of interaction errors that are completely silent (as may be the case if we were doing trace-based simulation). An error in pipeline interactions often causes wrong instruction or data to flow through the pipeline. This can either cause wrong execution that gets detected by our functional verifier or causes other forms of errors such as segment fault or deadlock, which again can be detected and fixed.

- Instruction reuse technique, for which the timing simulator is used, has a good property from the point of view of validation. It not only affects the timing but also the functionality of the simulator. (In this regard, it differs from other performance enhancing techniques, such as cache or prefetchers, which only affect the timing). If we reuse an instruction incorrectly, the processor will end up using an incorrect value, leading to incorrect program execution. This, again can be detected by either our functional verifier or through other non-silent ways such as deadlocks or segment faults. The error can then be fixed accordingly. The fact that all our simulations with IR were functionally correct lends high confidence to the reuse rate results.

- We implemented several *sanity-check* routines in our simulator that were called periodically (every 10,000 cycles) to check the consistency of the simulator data structures. For example, we check that the *number of unresolved branches* == *number of checkpoints taken for branch recovery*, or *depth of the retstack* > *number of returns in pipeline*. These sanity-check routines helped check the consistency of the data structures, making sure that the simulation was proceeding correctly.

- Finally, we performed extensive debugging using the debugger, *gdb*, single-stepping through every newly written piece of code to verify the timing information it generates. Next, we describe the microarchitecture and parameters of the simulated processor.

### 2.2 Processor Microarchitecture

The pipeline and the microarchitecture of the processor that we simulated in our timing

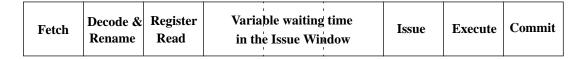

simulator are shown in Figure 2.1 (a) and (b), respectively. The pipeline consists of six stages: *Fetch, Decode & Rename, Register Read, Issue, Execute*, and *Commit*. All stages except the *Execute* stage are a single cycle in length; the *Execute* stage is of variable length, depending upon the latency of the executing instruction. In Figure 2.1 (a), we also depict the variable number of cycles that an instruction may have to wait before being issued. This pipeline structure is typical of currently available dynamically-scheduled processors (like, Pentium-III, HP-PA8500).

Next, we describe the various microarchitectural operations performed for processing an instruction. The *Instruction Fetch Unit* (IFU) fetches instructions from the I-cache (part of IFU) and places them in the *Instruction Queue* (IQ). The IFU also prepares the address of the

**(a)**

Figure 2.1 (a) Stages in the pipeline. (b) Microarchitecture modelled in the simulator.

next fetch using the branch prediction engine (also part of IFU). The instructions are read from the IQ by the Decode and Rename (D&R) unit. This unit decodes the instructions and renames their operands; it also allocates entries for them in the *Reorder Buffer* (ROB) [42] and the Issue Window (IW). In the Register Read stage, the register operand values are read from the architected register file or from the ROB, whichever contains the latest version of the register. The instructions and the operand values are placed in the pre-allocated IW entries; if an operand value is not ready, a tag (ROB index) identifying its producer is stored instead. This tag is used to snoop the value when it is broadcast after the producer finishes execution. The instructions are also placed in the pre-allocated ROB entries, where they await in-order retirement. The issue logic selects and dispatches ready instructions (i.e., instructions whose all operand values are available) from the IW to Function Units (FU) for execution. Load instructions are issued to the data cache only when there are no store instructions with unknown addresses ahead in the pipeline. If a load address matches the address of a store ahead in the pipeline, the store value is bypassed to the load (and the data cache access for the load is obviated). After an instruction completes execution, its results are written back into its ROB entry and are also broadcast to the IW entries where they are snooped by the instructions awaiting these results. Instructions are retired when they become the head of the ROB and the architectural state of the machine (register file and memory) are updated with their results.

The baseline configuration of the timing simulator is shown in Table 2.1

| Instruction fetch                        | 4 insts per cycle. Only one taken branch per cycle. Cannot fetch across cache line boundaries in the same cycle.                                                                                                                                                                                 |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| L1 Instruction cache                     | 64K bytes, 2-way set assoc., 32 byte line, 6 cycles miss latency.                                                                                                                                                                                                                                |  |  |

| Branch predictor                         | Gshare [28], with 10-bit history register and 16K entry counter table. Return Stack with 64 entries.                                                                                                                                                                                             |  |  |

| Out-of-Order<br>execution mecha-<br>nism | Issue of 4 operations/cycle, 64 entry RUU (which is the ROB and the IW combined) [46], 64 entry load/store queue. Max of 16 unresolved branches. Loads executed only after all preceding store addresses are known. Values bypassed to loads from matching stores ahead in the load/store queue. |  |  |

| Architected registers                    | 32 integer, hi, lo, 32 floating point, fcc.                                                                                                                                                                                                                                                      |  |  |

| Functional units<br>(FU)                 | 4-integer ALUs, 2 load/store units, 2-FP adders, 1-Integer MULT/DIV, 1-FP MULT/DIV.                                                                                                                                                                                                              |  |  |

| FU latency<br>(total/issue)              | int alu-1/1, load/store 1/1, int mult 3/1, int div 20/19, fp adder 2/1, fp mult 4/<br>1, fp div 12/12, fp sqrt 24/24.                                                                                                                                                                            |  |  |

| L1 Data cache                            | 64K bytes, 2-way set assoc., 32 byte line, 6 cycles miss latency. Dual ported, non-blocking.                                                                                                                                                                                                     |  |  |

| L2 cache                                 | Perfect (all accesses hit)                                                                                                                                                                                                                                                                       |  |  |

Table 2.1Base simulator parameters

## 2.3 Benchmarks

### 2.3.1 Description

The benchmark suite we use in this thesis consists of 21 programs: 8 SPEC '95 integer programs [4], 10 SPEC '95 floating-point programs, and 3 self-picked graphics programs. Table 2.2 shows the names and inputs for all the benchmarks. Since the three graphics benchmarks —*Viewperf+Mesa, MPEG-2 decoder,* and *POV-Ray* — are not as well-known as other benchmarks, we describe them further here. *Viewperf,* a benchmark developed by SPECopc<sup>sm</sup> [2], measures the performance of graphics systems that implement the OpenGL<sup>®</sup> API [1] by

| Benchmarks     | Inputs                          | Total<br>dynamic<br>inst. | #dynamic<br>inst.<br>simulated | # initial<br>dynamic<br>inst.<br>skipped |  |

|----------------|---------------------------------|---------------------------|--------------------------------|------------------------------------------|--|

|                | SpecInt '95                     |                           |                                |                                          |  |

| go             | null.in (ref)                   | 35.7B                     | 1B                             | 500M                                     |  |

| m88ksim        | ctl.in (ref)                    | 38.8B                     | 1B                             | 500M                                     |  |

| ijpeg          | vigo.ppm (train)                | 1.44B                     | 944M                           | 500M                                     |  |

| perl           | scrabbl.pl, scrabbl.in (train)  | 556M                      | 556M                           | -                                        |  |

| vortex         | vortex.in (train)               | 2.67B                     | 1B                             | 500M                                     |  |

| li             | au.lsp puzzle0.lsp xit.lsp      | 10.2B                     | 1B                             | 500M                                     |  |

| gcc            | reload.i                        | 921M                      | 921M                           | -                                        |  |

| compress       | bigtest.in (ref)                | 42.3B                     | 1B                             | 2.5B                                     |  |

|                | SpecFP '95                      |                           |                                |                                          |  |

| tomcatv        | train input with ITER = 50      | 2.44B                     | 1B                             | 500M                                     |  |

| swim           | train input with X=10, Y=10     | 849M                      | 849M                           | -                                        |  |

| su2cor         | train input with LSIZE= 8 8 8 8 | 4.6B                      | 1B                             | 500M                                     |  |

| hydro2d        | train input with ISTEP=10       | 4.67B                     | 1B                             | 500M                                     |  |

| mgrid          | train input with NTIMES=1       | 368M                      | 368M                           | -                                        |  |

| applu          | train input                     | 642M                      | 642M                           | -                                        |  |

| turb3d         | train input with nsteps=4       | 6.4B                      | 1B                             | 500M                                     |  |

| apsi           | train input                     | 2.67B                     | 1B                             | 500M                                     |  |

| fpppp          | train input                     | 499M                      | 499M                           | -                                        |  |

| wave5          | train input                     | 3.54B                     | 1B                             | 500M                                     |  |

|                | Graphics                        |                           | 1                              |                                          |  |

| Viewperf+Mesa  | Viewset: AWadvs-02              | 2.58B                     | 1B                             | 500M                                     |  |

| Mpeg-2 decoder | hhilong.m2v                     | 1.80B                     | 1B                             | 500M                                     |  |

| POV-Ray        | swirlbox.pov                    | 1.08B                     | 1.08B                          | -                                        |  |

rendering and manipulating 3D images using this API. *Mesa* [35] is a publicly available implementation of the OpenGL API that we used with Viewperf. *MPEG-2 decoder* [33] decodes and plays a movie encoded in MPEG-2 video format. *POV-Ray* [3] is a scene rendering application that creates 3-D images, with realistic lighting effects, using a rendering technique called ray-tracing.

Some benchmarks have command line parameters other than the inputs specified in Table 2.2. These parameters are listed in Table 2.3.

## 2.3.2 Compilation

All C benchmarks were cross-compiled to the Simplescalar ISA using *gcc* (version 2.6.3) with the following optimization flags: -O3, -funroll-loops, and -finline-functions. The assembler and the linker used were *gas* (version 2.5.2) and *gld* (version 2.5), respectively. The Fortran benchmarks were first converted to C using AT&T's *f2c* program and then compiled using

| Benchmarks     | Command line parameters                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m88ksim        | -c                                                                                                                                                                                              |

| ijpeg          | -compression.quality 90 -compression.optimize_coding 0 -compres-<br>sion.smoothing_factor 90 -difference.image 1 -difference.x_stride 10 -<br>difference.y_stride 10 -verbose 1 -GO.findoptcomp |

| gcc            | -quiet -funroll-loops -fforce-mem -fcse-follow-jumps -fcse-skip-blocks -<br>fexpensive-optimizations -fstrength-reduce -fpeephole -fschedule-insns -<br>finline-functions -fschedule-insns2 -O  |

| viewperf+mesa  | -pg DYN -rm POLYGON -nf 10 -cp FRAME -zb -nll 2 -bf -tx advs2.mtv<br>-magf LINEAR -minf LINEAR_MIPMAP_LINEAR -te MODULATE -<br>xws 720 -yws 720 -grab grab1.scr                                 |

| MPEG-2 decoder | -f -00 rec%d                                                                                                                                                                                    |

| POV-Ray        | -W320 -H200 -F +D -Q4                                                                                                                                                                           |

the C compiler. To allow for graphics display, we cross-compiled and linked the X11 library with the graphics benchmarks.

Since we used the f2c translator it is likely that the Fortran benchmarks were not as optimized as they would have been had they been compiled using a Fortran compiler. This can affect our results is some ways. Due to (probable) inefficient compilation, these programs may contain redundancies. This may increase the amount of repetition we see. Moreover, the translation may add many "support" instructions in the binary, which may also increase the amount of repetition we observe. Consequently, the amount of reuse we capture may also be more than what we would see for Fortran benchmarks compiled with a Fortran complier. However, more instructions in the translated code can also hurt reuse rate, because with more instructions there will be more contention in the RB and the reusable instructions may be evicted before being reused. Unfortunately, we have no way of discerning the amount of inefficiency induced by using f2c. However, the points discussed above should be borne in mind while interpreting the floating point results in this thesis.

## 2.3.3 Execution

In this section, we describe how we run our simulations. In Table 2.2, we show the number of dynamic instructions present in a complete run of each benchmark (for the input shown in column 2). To finish the simulations within a reasonable period, we only simulate a part of the complete run for benchmarks with large dynamic instruction counts. The actual number of instructions simulated is shown in column 4 (# instructions simulated). To ensure that our simulated portion of the benchmark does not entirely consist of the initialization phase, we skip the first 500M instructions (for most benchmarks), executing them on a fast functional simula-

tor, before simulating the 1B instructions. In Column 5, we show the number of instructions skipped for each benchmark. In the case of *compress*, we skip the first 2.5 billion instructions since *compress* has an unusually long initialization phase in which it internally generates the input file.

In Table 2.4, we present five baseline results for all benchmarks to show their relative characteristics. These results are base IPC (instructions per cycle), I- and D-cache miss rates, branch prediction rate, and the return stack hit rate (number of returns predicted correctly). These results were obtained using the base processor described in this chapter with the configuration shown in Table 2.1. Overall, most benchmarks have an IPC between 2 and 3. The I-cache misses are low for most benchmarks, except for *fpppp*. The D-cache misses are low for SpecInt '95 and graphics benchmarks (except for *compress*), but are relatively high for the SpecFP '95 benchmarks. The branch prediction rates and the return stack hit rates are high for most benchmarks, except for *go* and *ijpeg*.

In Table 2.5, we show the second set of inputs for our benchmarks. We use these inputs in Chapter 3 to investigate the sensitivity of the phenomenon of instruction repetition to program inputs.

|                | D IDC    | Cache       | Misses  | Branch                                       | Return            |  |

|----------------|----------|-------------|---------|----------------------------------------------|-------------------|--|

| Benchmarks     | Base IPC | I-Cache     | D-cache | <ul> <li>Prediction</li> <li>Rate</li> </ul> | Stack Hit<br>Rate |  |

|                |          | SpecInt '95 | 5       |                                              |                   |  |

| go             | 1.74     | 0.13%       | 0.89%   | 76%                                          | 100%              |  |

| m88ksim        | 2.43     | 0.00%       | 0.01%   | 95%                                          | 100%              |  |

| ijpeg          | 2.69     | 0.00%       | 0.63%   | 88%                                          | 99.9%             |  |

| perl           | 2.46     | 0.00%       | 0.98%   | 96%                                          | 99.8%             |  |

| vortex         | 2.78     | 0.19%       | 1.07%   | 98%                                          | 100%              |  |

| li             | 2.30     | 0.00%       | 1.28%   | 96%                                          | 99.8%             |  |

| gcc            | 2.05     | 0.29%       | 0.17%   | 91%                                          | 100%              |  |

| compress       | 2.28     | 0.00%       | 9.56%   | 91%                                          | 100%              |  |

|                | I        | SpecFP '95  | 5       |                                              |                   |  |

| tomcatv        | 2.87     | 0.00%       | 4.89%   | 98%                                          | 99.9%             |  |

| swim           | 2.56     | 0.00%       | 5.97%   | 98%                                          | 100%              |  |

| su2cor         | 2.34     | 0.00%       | 7.45%   | 94%                                          | 100%              |  |

| hydro2d        | 2.40     | 0.00%       | 10.03%  | 99%                                          | 99.3%             |  |

| mgrid          | 2.41     | 0.00%       | 2.23%   | 96%                                          | 100%              |  |

| applu          | 2.69     | 0.00%       | 3.78%   | 93%                                          | 100%              |  |

| turb3d         | 2.77     | 0.00%       | 1.74%   | 94%                                          | 100%              |  |

| apsi           | 2.11     | 0.01%       | 1.11%   | 96%                                          | 100%              |  |

| fpppp          | 1.63     | 4.04%       | 0.05%   | 94%                                          | 100%              |  |

| wave5          | 2.21     | 0.00%       | 2.75%   | 97%                                          | 100%              |  |

|                |          | Graphics    |         |                                              |                   |  |

| Viewperf+Mesa  | 2.10     | 0.32%       | 0.97%   | 94%                                          | 100%              |  |

| Mpeg-2 decoder | 2.87     | 0.00%       | 0.76%   | 94%                                          | 100%              |  |

| POV-Ray        | 2.16     | 0.59%       | 0.46%   | 94%                                          | 100%              |  |

Table 2.4Base IPC, I- and D-cache misses, branch prediction rates, and the return stack hitrates, for all benchmarks. Cache misses are percentages over total cache accesses. Branchprediction rates are percentages over total number of dynamic conditional branches. Returnstack hit rate are percentages over number of dynamic returns

| SpecInt '95    | Second set of inputs    | SpecFP '95 | Second set of inputs                |

|----------------|-------------------------|------------|-------------------------------------|

| go             | 2stone9.in              | tomcatv    | ref input                           |

| m88ksim        | train.in                | swim       | ref input with X= 100, Y= 100       |

| ijpeg          | specmun.ppm             | su2cor     | test input                          |

| perl           | primes.pl, primes.in    | hydro2d    | test input with MPROW = 200         |

| vortex         | vortex.in (ref)         | mgrid      | test input                          |

| li             | au.lsp tak2.lsp xit.lsp | applu      | test input                          |

| gcc            | amptjp.i                | turb3d     | test input with itest = 0           |

| compress       | test.in (train)         | apsi       | train input with $x = 32$ , $z = 8$ |

| Graphics       | Second set of inputs    | fpppp      | test input                          |

| Viewperf+Mesa  | Viewset: CDRS-04        | F          | test input with grid 625x20         |

| Mpeg-2 decoder | mei16v2.m2v             | wave5      | particle dist 2500 50               |

| POV-Ray        | mist.pov                |            |                                     |

Table 2.5

Second set of input for the benchmarks

# Chapter 3

# **An Empirical**

# **Analysis of Instruction Repetition**

In Chapter 1, we described the phenomenon of instruction repetition. Before we can discuss the methods for exploiting this phenomenon, we need to develop a better understanding of the phenomenon itself. We not only need to be aware of its various characteristics — such as percent of total dynamic instructions repeated, or groups of instructions generating most repetition — but we also need to understand the underlying causes that give rise to this phenomenon. Only after gaining such an understanding will we be able to exploit this phenomenon effectively.

To achieve this goal we perform two main tasks in this chapter: (i) we supply various characteristics regarding the phenomenon of repetition and (ii) we present an empirical analysis of instruction repetition to better explain what may be giving rise to this phenomenon. We begin by, first, qualitatively describing the causes of repetition and then introducing the different types of analyses we perform in this chapter.

# **3.1** Qualitative Description of Causes of Repetition

What causes instruction repetition? In Chapter 1, we briefly addressed this question and stated that instruction repetition occurs because of the repeating nature of input values and the structure of programs themselves. In this chapter, we elaborate further. To understand why program inputs and structure may cause repetition, let us consider how a typical program is written. In Figure 3.1, we show a piece of code: a function, *func*, that searches for an element x in an array *list* of size *size* (same as the code example used in Section 1.1.2). The structure of

```

int func(x, list, size) {

int i;

for(i=0; i<size; i++) {

if(x==list[i]) return i;

}

return -1;

}</pre>

```

Figure 3.1 A code fragment to exemplify the typical structure of a program. This example also occurs in Figure 1.2 of Chapter 1.

this program reveals the following characteristics about the way we write programs: (i) we write programs to be *generic* in nature: *i.e.*, we often don't write them for particular input values only; instead we write them to be capable of handling a variety of input values (e.g., different values of x or *list* in the above function); (ii) we express computation *concisely* using loops — e.g., in the above case, we did not write a unique statement for checking each element of the list; instead, we wrote one static check statement and used a loop to apply it to every element on the list; and, (iii) we break our programs into separate modules, like func-

tions, to simplify a complex task. Another common feature in programs (not exemplified explicitly in the above example) is data structures: we normally organize the program data, based on their logical grouping, into arrays, structs, lists, etc. For supporting such manners of programming, there exists several "extra" instructions in a program apart from the "computation" instructions which perform the actual task of the program. For supporting loops in programs, we have instructions that "run" the loop and help generate the dynamic program from the concise representation. To support the use of functions in programs, we have instructions that save and restore register state when entering and exiting a function. Similarly, to support complex data-structures, we need a fair amount of computation (and, hence, instructions) to access the individual elements in these data-structures.

How do these program characteristics engender repetition? We describe five ways. First, a program often encounters the same input data values repeatedly, causing the code which was written to be generic in nature to perform the same computation again. For example, programs that scan through text files (like *gcc*, *compress* and *grep*) may encounter repeated occurrences of the same items such as words, spaces, and characters. In the example shown in Figure 3.1, the function may be called repeatedly to search for different elements in the same list, which may result in instructions operating on the list value to perform the same computation repeatedly. Second, the loop-control instructions, which perform the task of unravelling the concisely expressed computation, may get repeated when the job of unravelling the computation is performed repeatedly for different invocations of the same piece of code (e.g., the loop control instructions would get repeated when the same loop is invoked again). These instructions would get repeated even if the computation performed is entirely new. Third, the instructions devoted to accessing the elements of a complex data-structure may get repeated when the

same elements are accessed repeatedly, even if the value being accessed is different. Fourth, the register save-restore code of a function may get repeated if the registers do not change between two calls to the function. Finally, many instructions in programs have immediate values as operands, e.g., simple initialization instructions or groups of instructions loading a large constant in a register. These instructions (and instructions dependent on them) get repeated on re-execution since their operands are constants.

## **3.2 Quantitative Analyses: Introduction and Rationale**

After identifying the causes of repetition qualitatively, we are now ready to analyze the phenomenon quantitatively. But, at this point, we are faced with the dilemma as to what sort of analysis should we conduct. What sort of investigation would satisfyingly reveal the nature of the phenomenon? Unfortunately, a direct answer to this question in not possible, at least not at present, and we make no attempt to obtain such an answer. Instead, we perform several different types of analyses, each providing a different way of looking at the phenomenon, and, hopefully, all together providing a better understanding about the nature of the phenomenon. These analyses fall into two broad categories: a category that attempts to characterize the phenomenon and a category that attempts to isolate the contribution of different "parts" of programs to the phenomenon.

To characterize instruction repetition, we carry out analyses similar to what others [12, 39] have carried out for related phenomenon: we analyze the instructions of a program as a whole. We call this a *statistical* analysis. Here we ask questions of the form: how much repeatability exists? how many static instructions account for a certain fraction of the repeatability? etc.

While a statistical analysis allows us to characterize the phenomenon, it fails to give us insight into the causes of instruction repetition. Answers to questions of the form: how much of the repeatability is due to repeated inputs? how much can be attributed to instructions that unwind the dynamic computation? etc. are not available. To answer these questions, we need to categorize both the instructions that are executed as well as the instructions that are repeated, into different classes (e.g., instructions that operate upon external inputs, or those that operate upon global variables).

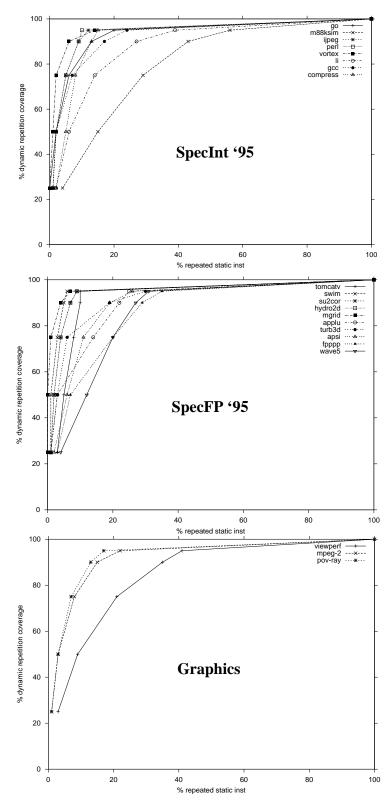

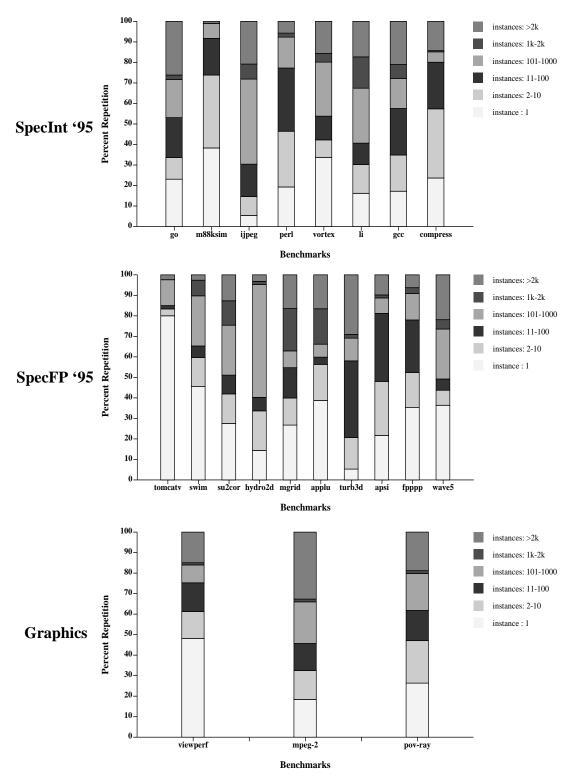

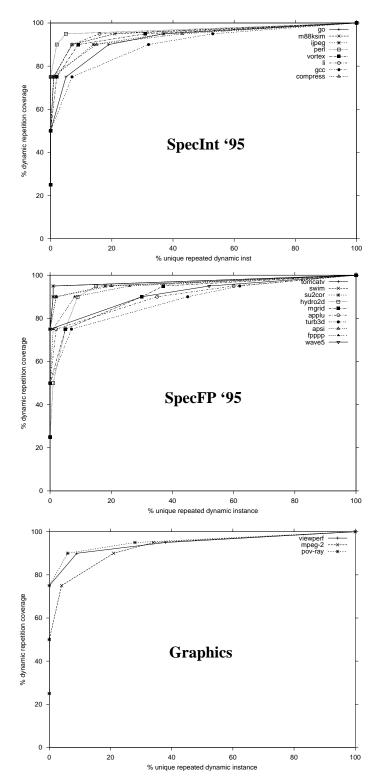

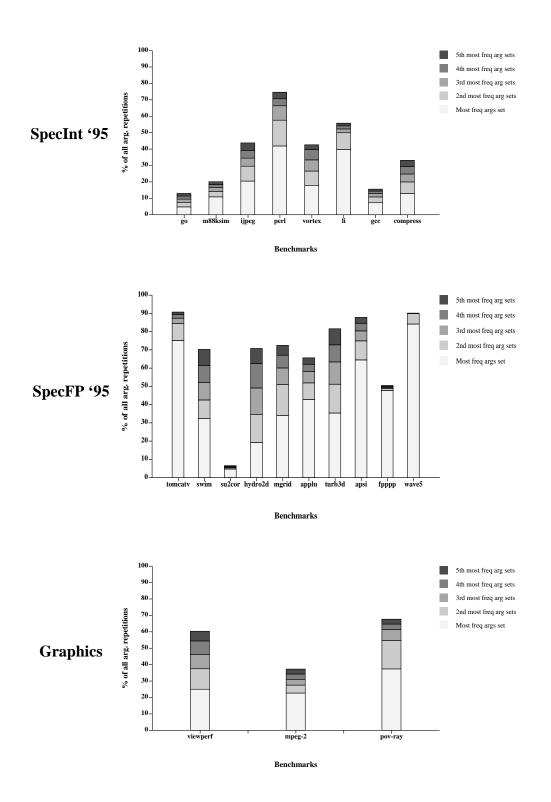

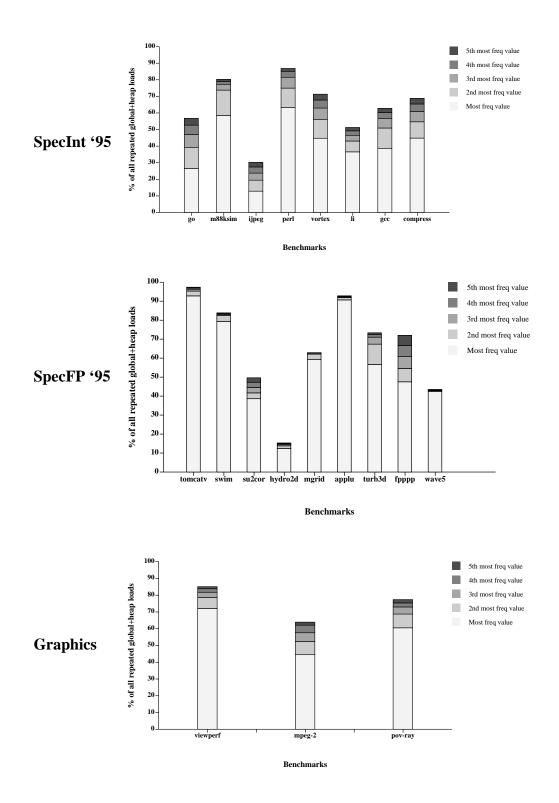

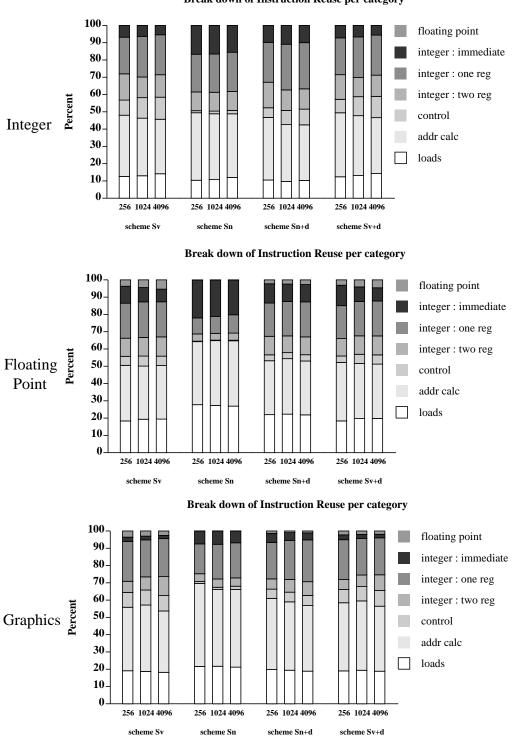

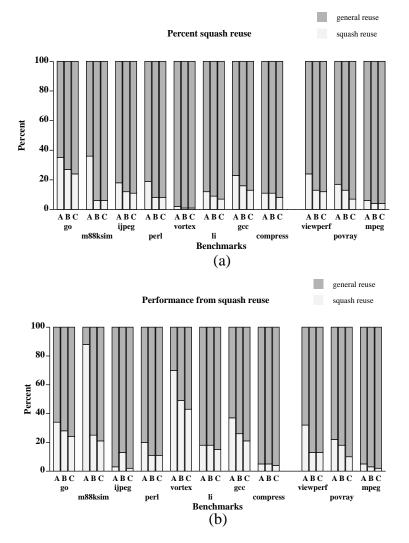

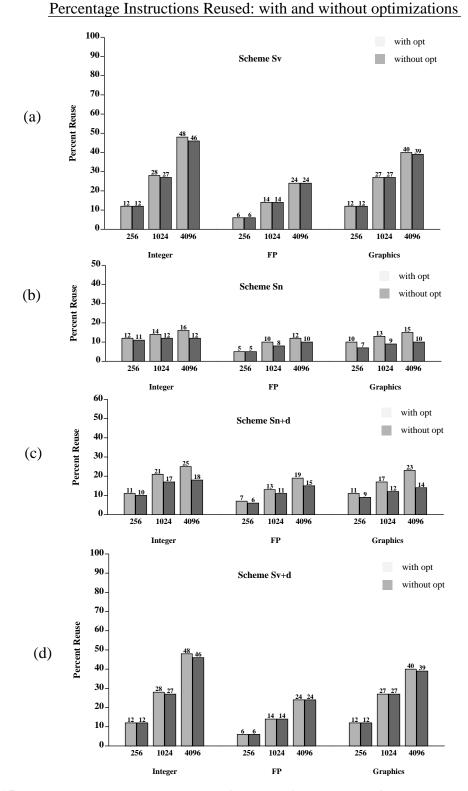

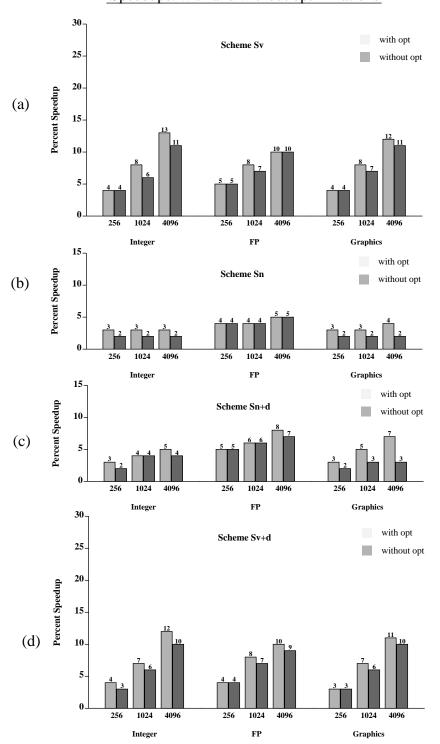

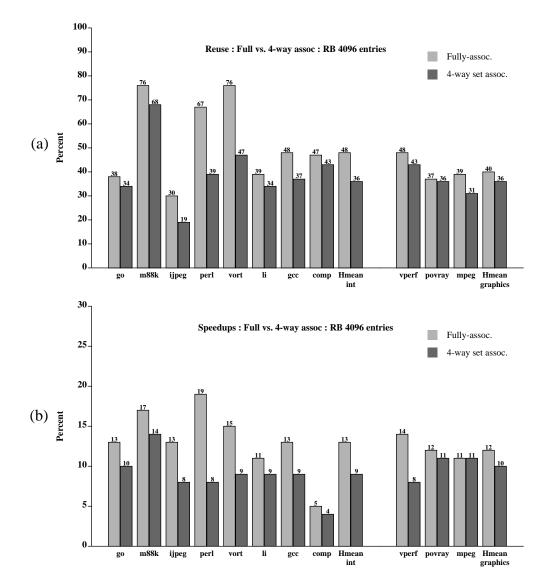

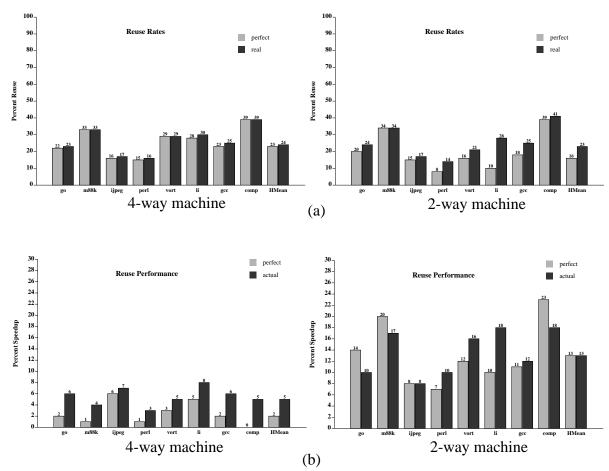

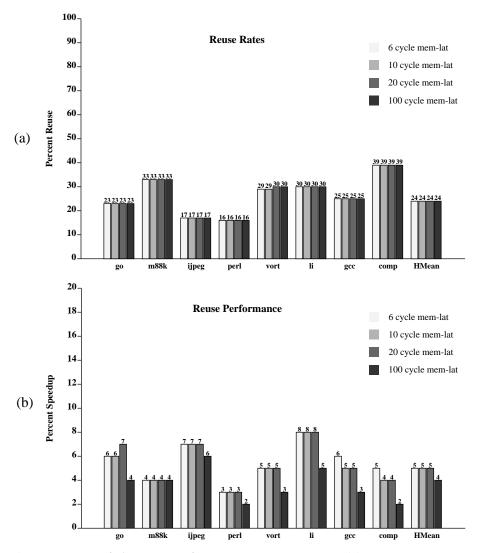

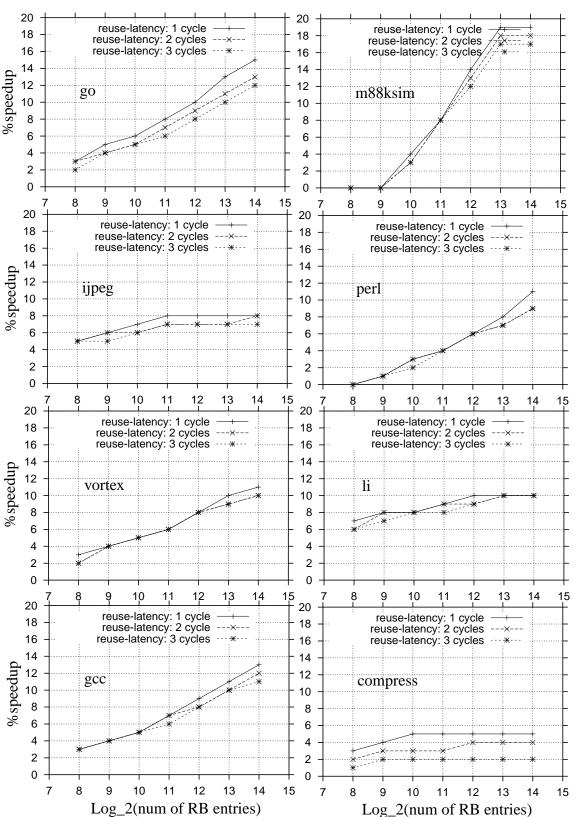

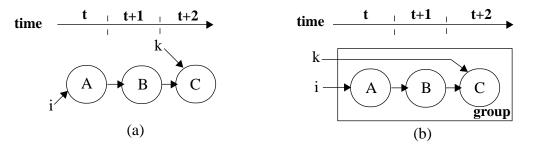

Categorizing instructions into different classes requires us to capture dynamic *slices of instructions*, that is, dynamic paths through programs traced by the flow of data (e.g., a slice of instructions executed in a function that depends upon its first argument). In capturing slices of computation, we are faced with the question of whether to consider data dependences, control dependences, or both. Control dependences determine *which* static instructions are entered into the dynamic instruction stream, and data dependences determine the outcome of those instructions. Since our purpose is to understand the repetitive behavior of instructions that are present in the dynamic instruction stream and not with how static instructions are entered into the dynamic instruction stream, we do not consider control dependences when dividing the dynamic instruction stream into dynamic slices. We base our decisions and analysis solely on data dependence relationships (in fact, the notion of a control dependence is somewhat meaningless in a *dynamic* instruction stream).