# THE MULTISCALAR ARCHITECTURE

by

# MANOJ FRANKLIN

A thesis submitted in partial fulfillment of the requirements for the degree of

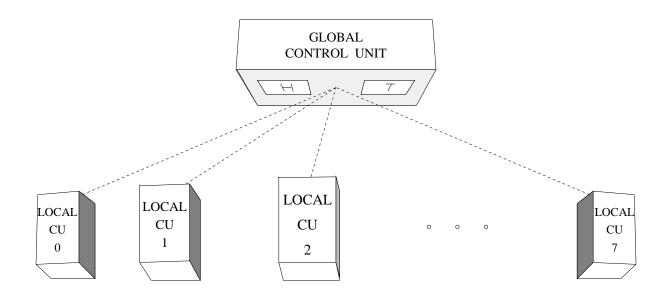

## DOCTOR OF PHILOSOPHY

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN — MADISON

1993

# THE MULTISCALAR ARCHITECTURE

#### Manoj Franklin

Under the supervision of Associate Professor Gurindar S. Sohi at the University of Wisconsin-Madison

#### **ABSTRACT**

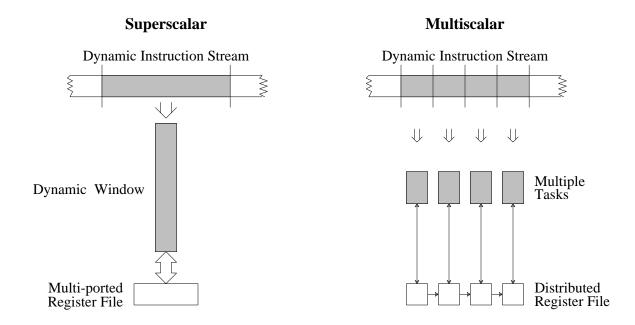

The centerpiece of this thesis is a new processing paradigm for exploiting instruction level parallelism. This paradigm, called the *multiscalar* paradigm, splits the program into many smaller tasks, and exploits fine-grain parallelism by executing multiple, *possibly (control and/or data) dependent* tasks in parallel using multiple processing elements. Splitting the instruction stream at statically determined boundaries allows the compiler to pass substantial information about the tasks to the hardware. The processing paradigm can be viewed as extensions of the superscalar and multiprocessing paradigms, and shares a number of properties of the sequential processing model and the dataflow processing model.

The multiscalar paradigm is easily realizable, and we describe an implementation of the multiscalar paradigm, called the multiscalar processor. The central idea here is to connect multiple sequential processors, in a decoupled and decentralized manner, to achieve overall multiple issue. The multiscalar processor supports speculative execution, allows arbitrary dynamic code motion (facilitated by an efficient hardware memory disambiguation mechanism), exploits communication localities, and does all of these with hardware that is fairly straightforward to build. Other desirable aspects of the implementation include decentralization of the critical resources, absence of wide associative searches, and absence of wide interconnection/data paths.

The multiscalar processor design has novel features such as the *Address Resolution Buffer* (*ARB*), which is a powerful hardware mechanism for enforcing memory dependencies. The ARB allows arbitrary dynamic motion of memory reference instructions by providing an efficient way of detecting memory hazards, and instructing the multiscalar hardware to restart portions of the dynamic instruction stream when hazards are violated.

We also present the results of a detailed simulation study showing the performance improvements offered by the multiscalar processor. These preliminary results are very encouraging. The multiscalar paradigm seems to be an ideal candidate to reach our goal of 10+ instructions per cycle, and has tremendous potential to be the paradigm of choice for a circa 2000 (and beyond) ILP processor.

# Acknowledgements

First of all, I offer praise and thanks with a grateful heart to my *Lord JESUS CHRIST*, to whom this thesis is dedicated, for *HIS* infinite love and divine guidance all through my life. Everything that I am and will ever be will be because of *HIM*. It was *HE* who bestowed me with the ability to do this piece of research. *HE* led and inspired me during the past six years over which I learned many spiritual matters, without which all these achievements are meaningless, and a mere chasing after the wind. So, to *God* be the praise, glory, and honor, for ever and ever.

I am deeply indebted to my PhD advisor, Professor Gurindar S. Sohi, for the constant guidance he provided in the course of this research. Guri shared with me many of his ideas, and gave extremely insightful advice aimed at making me aim higher and higher in doing research. His ability to identify significant ideas, and suppress insignificant ones was invaluable. I feel honored and privileged to have worked with him for this thesis.

I am very grateful to my MS advisor, Professor Kewal K. Saluja, for his encouragement and advice throughout my graduate studies, and for the opportunity to do research with him in many areas. I am deeply indebted to Professor James R. Goodman for his help and encouragement in steering me into Computer Sciences. I would like to thank Professor Mark Hill for his insightful comments on this thesis. I am very grateful to Professor Wilson Pearson for providing all facilities at Clemson University, where I can continue my career.

Members of my family, each in his/her own way, have taught me and loved me far beyond what I could ever repay. I would like to acknowledge my father Dr. G. Aruldhas and mother Mrs. Myrtle Grace Aruldhas, for their unfailing concern, care and support throughout my life. They have always encouraged me to strive for insight and excellence, while staying in the spiritual path. A heartfelt thanks to my sister, Dr. A. Ann Adeline, for her continuous love and support over the years. I am grateful to my uncle, Dr. G. Sundharadas, for his help and encouragement, especially in the beginning

stages of my graduate studies, a time when it was most needed.

I would like to acknowledge my friend Dr. B. Narendran, who kindled my interest in recreative mathematics and puzzles. Over the years, he has made many contributions to my papers on testing. I thank him for many helpful mathematical discussions and interesting puzzle solving sessions. On a different note, I thank my friend, Neena Dakua, for many stimulating philosophical discussions years back, which put me on a thinking path. I owe a special debt to her, D. Chidambara Krishnan, and my colleagues in Bangalore, for helping me to come to the USA for higher studies. I would like to acknowledge my friend Dr. Rajesh Mansharamani for taking care of all the logistics in connection with my thesis submission. Dionisios N. Pnevmatikatos took care of all my UNIX questions.

I would like to acknowledge my close friends in India, R. Rajendra Kumar and D. Sanil Kumar, who have demonstrated the reality of "friend in need", by the warmth and affection of their selfless love, which has accompanied me through the ups and downs of life. Rajendran's letters from far away have always been a constant source of encouragement.

I would very much like to thank my brothers and sisters in Christ, for their prayers and care over the years in Madison. In particular, I would like to thank Chellapandi Subramanian, Adharyan T. Dayan, Dr. Suseela Rajkumar, Mathews Abraham, Shelin Mathews, Paul Lanser, Karin Lanser, Professor Wayne M. Becker, and the members of the Faith Community Bible Church and Indonesian Christian Fellowship. They have made my time in Madison meaningful and enjoyable. The daily prayer meetings with Chella will always stay in my mind.

Finally, the arrival of my better half Dr. Bini Lizbeth George into my life inspired me to come out of the dissertator cocoon. If not for her, I would still be analyzing every nook and corner of the multiscalar architecture. She has shared every nuance of the last two years with me, and I express my deep gratitude to her for her love and affection.

My research as a graduate student was mostly supported by IBM through an IBM Graduate Fellowship, and also by Professor Gurindar Sohi through his NSF grant (contract CCR-8706722).

# **Table of Contents**

| Abstract                                             |  |  |  |

|------------------------------------------------------|--|--|--|

| Acknowledgements                                     |  |  |  |

| Table of Contents                                    |  |  |  |

| Chapter 1. Introduction                              |  |  |  |

| 1.1. Why ILP Processors?                             |  |  |  |

| 1.2. Challenges                                      |  |  |  |

| 1.3. Contributions of this Thesis                    |  |  |  |

| 1.4. Organization of the Thesis                      |  |  |  |

| Chapter 2. ILP Processing                            |  |  |  |

| 2.1. Program Execution Basics                        |  |  |  |

| 2.1.1. Constraints on ILP                            |  |  |  |

| 2.1.2. Program Representations                       |  |  |  |

| 2.2. Program Specification and Execution Models      |  |  |  |

| 2.2.1. Program Specification Order                   |  |  |  |

| 2.2.1.1. Control-Driven Specification                |  |  |  |

| 2.2.1.2. Data-Driven Specification                   |  |  |  |

| 2.2.2. Program Execution Order                       |  |  |  |

| 2.3. Fundamentals of ILP Processing                  |  |  |  |

| 2.3.1. Expressing ILP                                |  |  |  |

| 2.3.2. Extracting ILP by Software                    |  |  |  |

| 2.3.2.1. Establishing a Window of Operations         |  |  |  |

| 2.3.2.2. Determining and Minimizing Dependencies     |  |  |  |

| 2.3.2.3. Scheduling Operations                       |  |  |  |

| 2.3.3. Extracting ILP by Hardware                    |  |  |  |

| 2.3.3.1. Establishing a Window of Instructions       |  |  |  |

| 2.3.3.2. Determining and Minimizing Dependencies     |  |  |  |

| 2.3.3.3. Scheduling Instructions                     |  |  |  |

| 2.3.4. Exploiting Parallelism                        |  |  |  |

| 2.4. A Critique on Existing ILP Processing Paradigms |  |  |  |

| 2.4.1. The Dateflow Paradigm                         |  |  |  |

| 2.4.2. The Systolic Paradigm and Other Special Purpose Paradigms | 41 |

|------------------------------------------------------------------|----|

| 2.4.3. The Vector Paradigm                                       | 42 |

| 2.4.4. The VLIW Paradigm                                         | 43 |

| 2.4.5. The Superscalar Paradigm                                  | 44 |

| 2.4.6. The Multiprocessing Paradigm                              | 45 |

| 2.5. Observations and Conclusions                                | 46 |

| Chapter 3. The Multiscalar Paradigm                              | 48 |

| 3.1. Ideal Processing Paradigm—The Goal                          | 49 |

| 3.2. Multiscalar Paradigm—The Basic Idea                         | 50 |

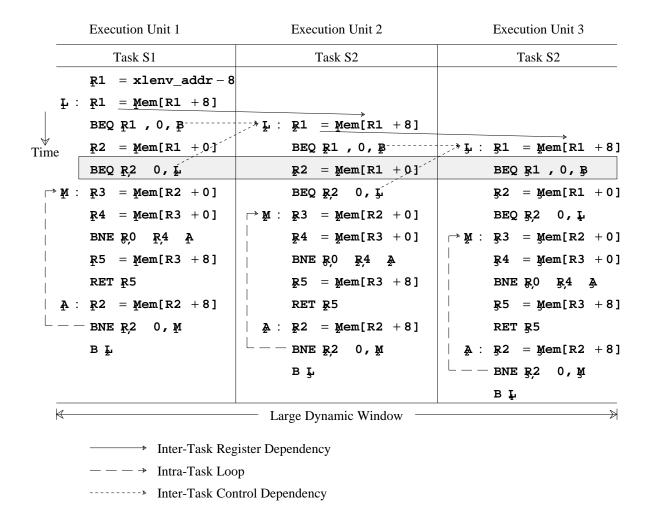

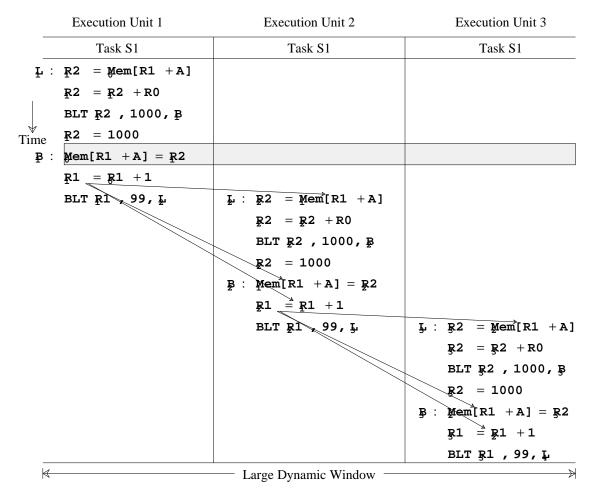

| 3.2.1. Multiscalar Execution Examples                            | 53 |

| 3.3. Interesting Aspects of the Multiscalar Paradigm             | 6. |

| 3.3.1. Decentralization of Critical Resources                    | 63 |

| 3.3.2. Execution of Multiple Flows of Control                    | 6. |

| 3.3.3. Speculative Execution                                     | 64 |

| 3.3.4. Parallel Execution of Data Dependent Tasks                | 64 |

| 3.3.5. Exploitation of Localities of Communication               | 64 |

| 3.3.6. Conveyance of Compile-Time Information to the Hardware    | 6. |

| 3.4. Comparison with Other Processing Paradigms                  | 6. |

| 3.4.1. Multiprocessing Paradigm                                  | 65 |

| 3.4.2. Superscalar Paradigm                                      | 6  |

| 3.4.3. VLIW Paradigm                                             | 68 |

| 3.4.3.1. Adaptability to Run-Time Uncertainities                 | 69 |

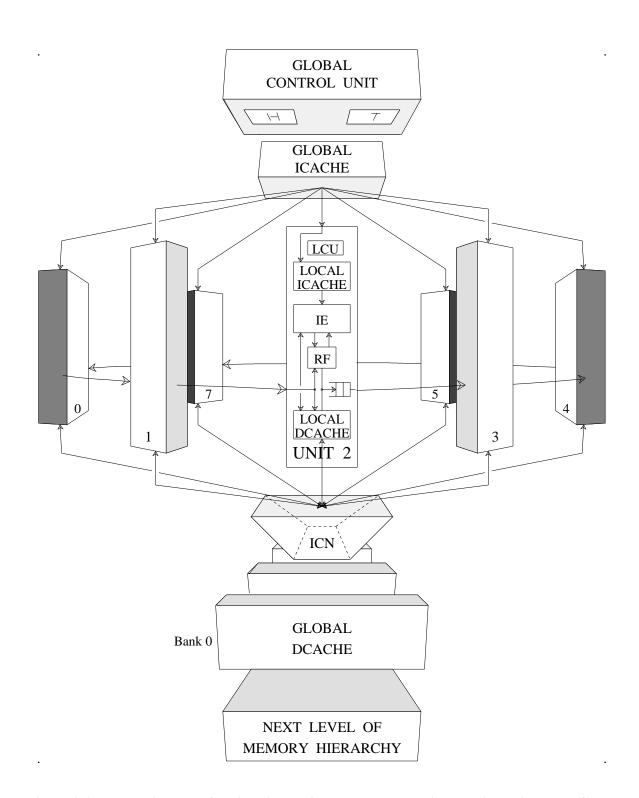

| 3.5. The Multiscalar Processor                                   | 7  |

| 3.6. Summary                                                     | 73 |

|                                                                  |    |

| Chapter 4. Control and Execution Units                           | 75 |

| 4.1. Execution Unit                                              | 75 |

| 4.2. Control Mechanism                                           | 7  |

| 4.2.1. Task Prediction                                           | 78 |

| 4.2.1.1. Static Task Prediction                                  | 79 |

| 4.2.1.2. Dynamic Task Prediction                                 | 79 |

| 4.2.2. Recovery Due to Incorrect Task Prediction                 | 8  |

| 4.2.3. Task Completion                                           | 8  |

| 4.2.4. Handling Interrupts                                       | 82 |

| 4.2.5. Handling Page Faults                                      | 82 |

| 4.3. Instruction Supply Mechanism                                | 8. |

| 4.4. Summary                                                     | 8. |

| Chapter 5 | Register File                                               | 86  |

|-----------|-------------------------------------------------------------|-----|

| 5         | Inter-Operation Communication in the Multiscalar Processor  | 86  |

|           | 5.1.1. High Bandwidth                                       | 87  |

|           | 5.1.2. Support for Speculative Execution                    | 88  |

| 5         | 2. Multi-Version Register File—Basic Idea                   | 88  |

|           | 5.2.1. Intra-Task Register Communication                    | 89  |

|           | 5.2.2. Inter-Task Register Communication                    | 90  |

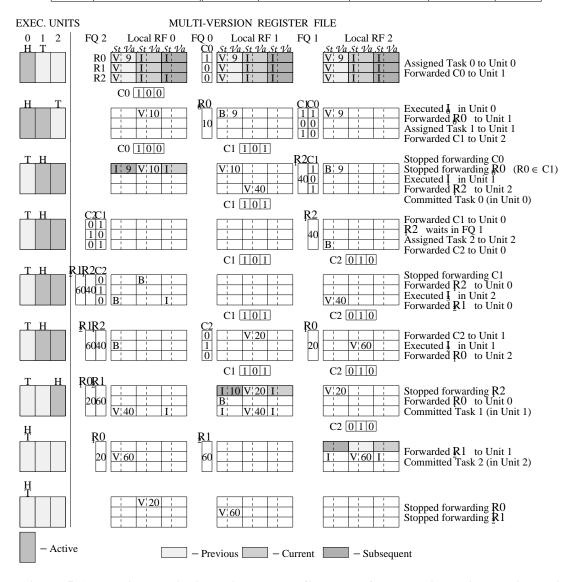

|           | 5.2.3. Example                                              | 92  |

| 5         | 3. Multi-Version Register File—Detailed Working             | 94  |

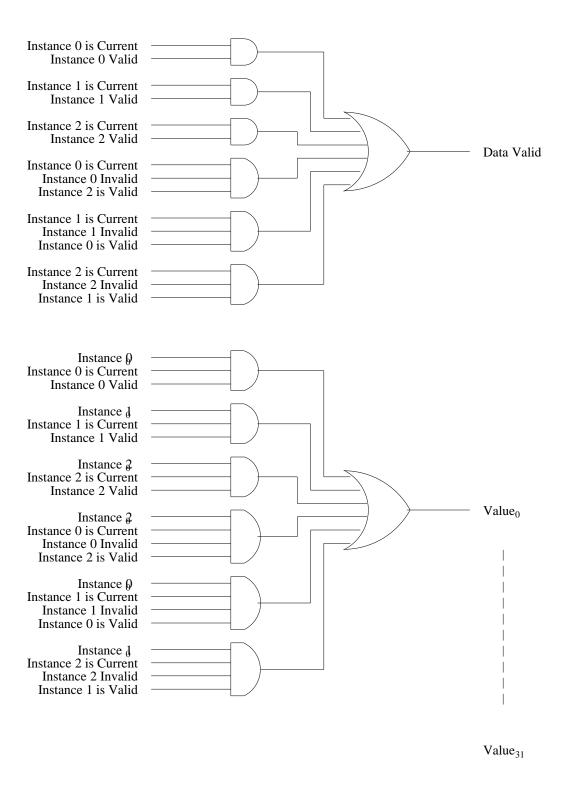

|           | 5.3.1. Enforcing Inter-Unit Register Data Dependencies      | 95  |

|           | 5.3.1.1. How are Busy Bits Set?                             | 96  |

|           | 5.3.1.2. How are Busy Bits Reset?                           | 98  |

|           | 5.3.2. Register Write                                       | 100 |

|           | 5.3.3. Register Read                                        | 100 |

|           | 5.3.4. Committing an Execution Unit                         | 101 |

|           | 5.3.5. Recovery Actions                                     | 103 |

|           | 5.3.6. Example                                              | 103 |

| 5         | 4. Novel Features of the Multi-Version Register File        | 106 |

|           | 5.4.1. Decentralized Inter-Operation Communication          | 106 |

|           | 5.4.2. Exploitation of Communication Localities             | 106 |

|           | 5.4.3. Register Renaming                                    | 107 |

|           | 5.4.4. Fast Recovery                                        | 107 |

| 5         | 5. Summary                                                  | 107 |

|           |                                                             |     |

| CI.       |                                                             | 100 |

|           | Data Memory System                                          | 109 |

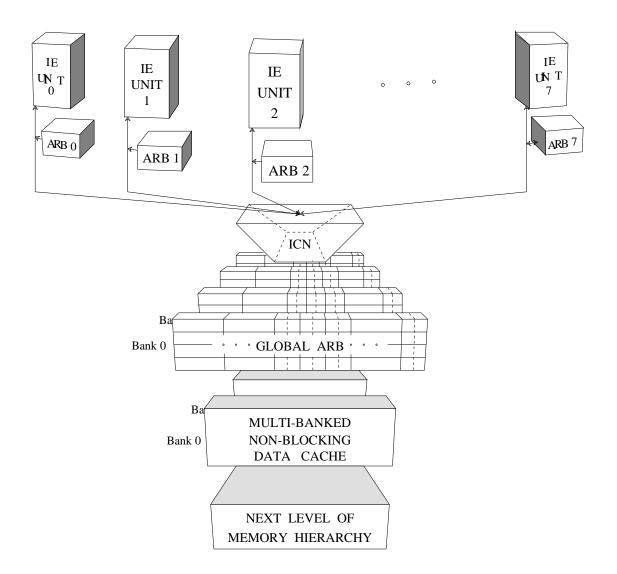

| 6         | 1. Requirements of the Multiscalar Data Memory System       | 110 |

|           | 6.1.1. High Bandwidth                                       | 110 |

|           | 6.1.2. Support for Speculative Execution                    | 110 |

|           | 6.1.3. Support for Dynamic Memory Disambiguation            | 111 |

|           | 6.1.4. Support for Dynamically Unresolved Memory References | 111 |

|           | 2. High-Bandwidth Data Memory System                        | 112 |

| 6         | 3. Existing Dynamic Disambiguation Techniques               | 113 |

|           | 6.3.1. Techniques for Control-Driven Execution              | 114 |

| _         | 6.3.2. Techniques for Data-Driven Execution                 | 116 |

| 6         | 4. Address Resolution Buffer (ARB)                          | 118 |

|           | 6.4.1. Basic Idea of ARB                                    | 119 |

|           | 6.4.2. ARB Hardware Structure                               | 119 |

|           | 6.4.3. Handling of Loads and Stores                         | 121 |

| 6.4.                 | 4. Reclaiming the ARB Entries                          | 125 |

|----------------------|--------------------------------------------------------|-----|

| 6.4.                 | 5. Example                                             | 126 |

| 6.4.                 | 6. Two-Level Hierarchical ARB                          | 127 |

| 6.5. Novel           | Features of the ARB                                    | 129 |

| 6.5.                 | 1. Speculative Loads and Stores                        | 129 |

| 6.5.                 | 2. Dynamically Unresolved Loads and Stores             | 131 |

| 6.5.                 | 3. Memory Renaming                                     | 131 |

| 6.6. ARB E           | Extensions                                             | 132 |

| 6.6.                 | 1. Handling Variable Data Sizes                        | 132 |

| 6.6.                 | 2. Set-Associative ARBs                                | 133 |

| 6.7. Summa           | ary                                                    | 134 |

|                      |                                                        |     |

| Chanter 7 Empirica   | ıl Results                                             | 136 |

|                      | mental Framework                                       | 136 |

| -                    | 1. Multiscalar Simulator                               | 137 |

|                      | Assumptions and Parameters Used for Simulation Studies | 137 |

|                      | 3. Benchmarks and Performance Metrics                  | 139 |

|                      | 4. Caveats                                             | 140 |

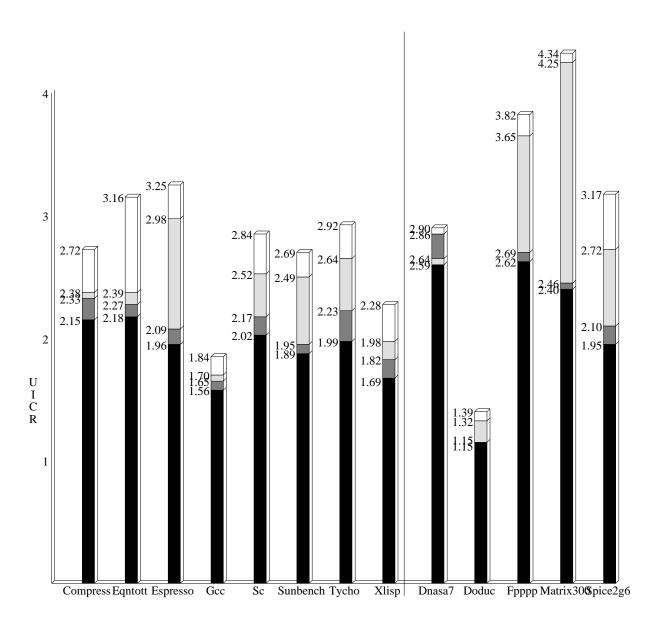

|                      | nance Results                                          | 141 |

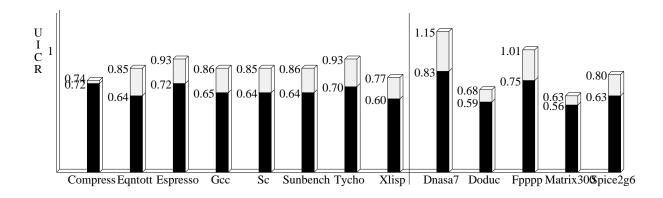

|                      | UICR with One Execution Unit                           | 141 |

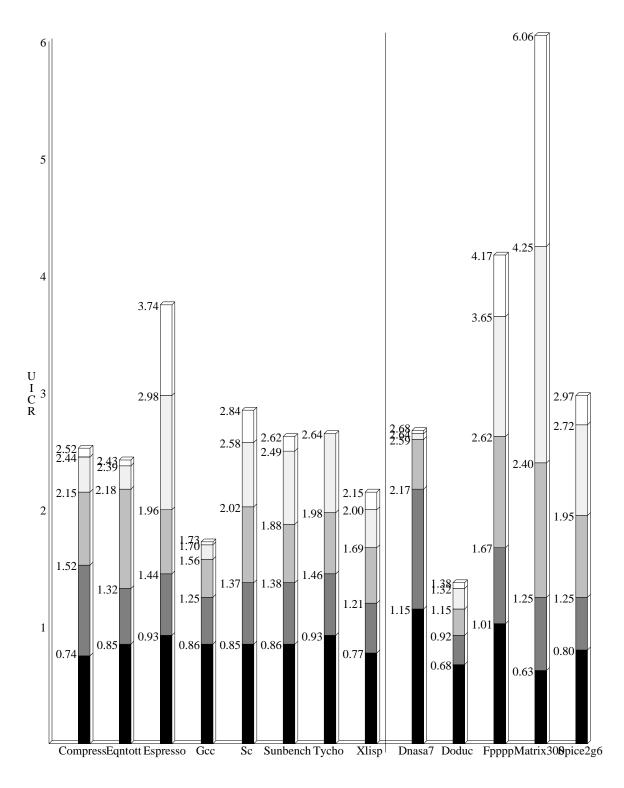

|                      | 2. UICR with Multiple Execution Units                  | 142 |

|                      | Task Prediction Accuracy                               | 144 |

|                      | 4. Incorrect Loads                                     | 146 |

|                      | Effect of Data Cache Miss Latency                      | 146 |

|                      | 6. Effect of Data Cache Access Time                    | 147 |

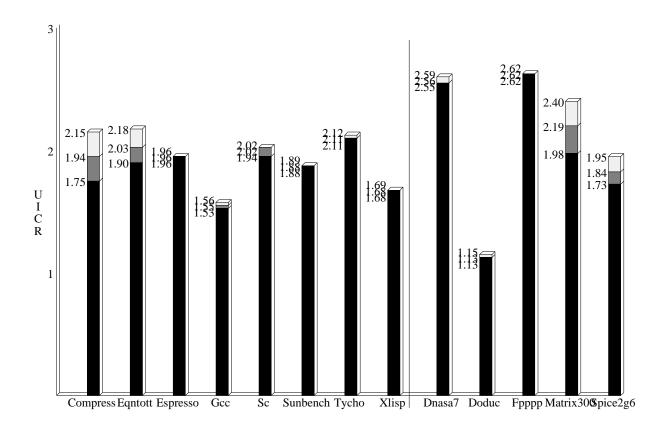

|                      | 7. Efficacy of Multi-Version Register File             | 148 |

|                      | ary                                                    | 151 |

| 7.4. Summe           |                                                        | 131 |

|                      |                                                        |     |

| Chapter 8. Role of C | Compiler                                               | 153 |

| 8.1. Task S          | election                                               | 153 |

| 8.1.                 | 1. Task Size                                           | 154 |

| 8.1.                 | 2. Inter-Task Data Dependencies                        | 154 |

| 8.1.                 | 3. Task Predictability                                 | 155 |

|                      | ask Static Scheduling                                  | 155 |

|                      | 1. Multiscalar-specific Optimizations                  | 158 |

| 8.2.                 | 2. Static Disambiguation                               | 158 |

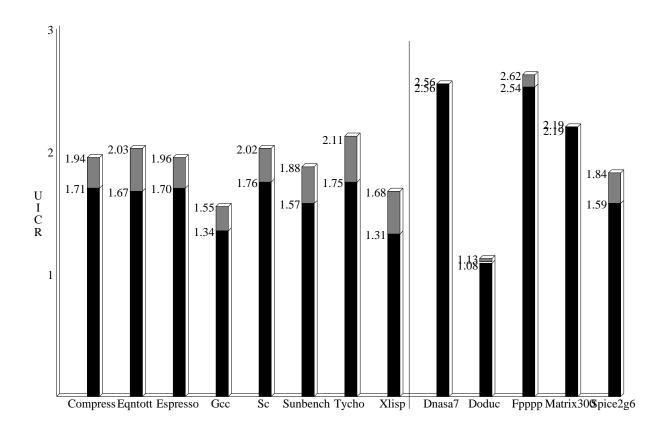

| 8.2.                 | 3. Performance Results with Hand-Scheduled Code        | 159 |

| 8.3. Other (         | Compiler Support                                       | 160 |

| 8.3.1. Static Task Prediction                             | 160        |

|-----------------------------------------------------------|------------|

| 8.3.2. Reducing Inter-Unit Register Traffic               | 160        |

| 8.3.3. Synchronization of Memory References               | 161        |

| 8.4. Summary                                              | 161        |

| Chapter 9. Conclusions                                    | 163        |

| 9.1. Summary                                              | 163        |

| 9.2. Future Work                                          | 164        |

| 9.2.1. Multiscalar Compiler                               | 165        |

| 9.2.2. Sensitivity Studies                                | 165        |

| 9.2.3. Evaluation of ARB                                  | 165        |

| 9.2.4. Multi-Version Data Cache                           | 165        |

| 9.2.5. Multiscalar-based Multiprocessing                  | 166        |

| 9.2.6. Testing                                            | 168        |

| Appendix                                                  | 169<br>169 |

| A.1.1 Increasing the Effective Number of ARB Stages       | 170        |

| A.2. Application of ARB to Statically Scheduled Machines  | 170        |

| A.2.1. Basic Idea                                         | 172        |

| A.2.2. Reclaiming the ARB Entries                         | 174        |

| A.2.3. Restrictions to Reordering of Ambiguous References | 176        |

| A.3. Application of ARB to Shared-memory Multiprocessors  | 178        |

| A.3.1. Detection of Data Races                            | 178        |

| A.3.2. Implicit Synchronization                           | 179        |

| A.4. Summary                                              | 182        |

|                                                           |            |

| References                                                | 183        |

# Chapter 1.

# Introduction

How to exploit parallelism from ordinary, non-numeric programs?

In spite of the tremendous increases in computing power over the years, nobody has ever felt a glut in computing power; the demand for computing power seems to increase with its supply. To satisfy this demand in the midst of fast approaching physical limits such as speed of light, scientists should find ever ingenious ways of increasing the computing power. The main technique computer architects use to achieve speedup is to do *parallel processing*. Today digital computing is at a point where clock speeds of less than 10ns are becoming the norm, and further improvements in the clock speed require tremendous engineering effort. An order of magnitude improvement in clock speed (to achieve clock cycles in the sub-nanosecond range) may be difficult, especially because of approaching physical limits. However, looking into the late 1990s and the early 2000s, there appears to be no end in sight to the growth in the number of transistors that can be put on a single chip. Technology projections even suggest the integration of 100 million transistors on a chip by the year 2000 [60], in place of the 2-4 million transistors that are integrated today. This has prompted computer architects to consider new ways of utilizing the additional resources for doing parallel processing.

The execution of a computer program involves *computation* operations and *communication* of values, constrained by *control* structures in the program. The basic idea behind parallel processing is to use multiple hardware resources to process multiple computations as well as multiple communication arcs in parallel so as to reduce the execution time, which is a function of the total number of computation operations and communication arcs, the cycle time, and the average number of computation nodes and communication arcs executed in a cycle. With the continued advance in technology, switching components have become progressively smaller and more efficient, with the effect that

computation has become reasonably fast. Communication speed, on the other hand, seems to be more restricted by the effects of physical factors such as the speed of light, and has become the major bottleneck.

The parallelism present in programs can be classified into different types — regular versus irregular parallelism, coarse-grain versus fine-grain (instruction level) parallelism, etc. Regular parallelism, also known as *data parallelism*, refers to the parallelism in performing the same set of operations on different elements of a data set, and is very easy to exploit. Irregular parallelism refers to parallelism that is not regular, and is harder to exploit. Coarse-grain parallelism refers to the parallelism between large sets of operations such as subprograms, and is best exploited by a multiprocessor. Fine-grain parallelism, or instruction level parallelism refers to the parallelism between individual operations. Over the years, several processing paradigms, including some special purpose paradigms, have been proposed to exploit different types of parallelism. While we would like to stay away from special purpose architectures and be as general as possible, we would still like to carve out our niche, which is *instruction level parallelism* or *ILP* for short. This thesis explores the issues involved in ILP processing, and proposes and investigates a new architectural paradigm for ILP processing.

## 1.1. Ny ILP Processors?

Why, in any case, must we investigate ever ingenious ways of exploiting ILP? The answer is that it is important to exploit parallelism, and many important applications exist (mostly non-numeric) in which ILP appears to be the only type of parallelism available. Exploitation of parallelism at the instruction level is very important to speed up such programs. Recent studies have confirmed that there exists a large amount of instruction-level parallelism in ordinary programs [18, 25, 36, 106, 159]. Even in other applications, no matter how much parallelism is exploited by coarse-grain parallel processors such as the multiprocessors, a substantial amount of parallelism will still remain to be exploited at the instruction level. Therefore, irrespective of the speedup given by a coarse-grain parallel processor, ILP processing can give additional speedups over that speedup. Thus,

coarse-grain parallel processing and ILP processing complement each other, and we can expect future multiprocessors to be a collection of ILP processors.

Although ILP processing has been used in the highest performance uniprocessors for the past 30 years, it was traditionally confined to special-purpose paradigms for exploiting regular parallelism from numeric programs. In this thesis we place a strong emphasis on exploiting ILP from non-numeric programs, which mostly contain irregular parallelism. This is not to belittle the importance of numeric programs, which are the backbone of many theoretical and simulation studies in scientific applications. We feel that numeric programs have received substantial attention in the past, whereas non-numerical programs have received only a passing attention. The ILP machines developed so far — vector machines, the primal VLIW machines [55], etc. — have all specifically targeted numeric applications. Our motivation for targeting the difficult irregular parallelism in non-numeric programs is that if we are able to develop techniques to extract and exploit even small amounts of ILP from such programs (which are anathema for ILP), then the same collection of techniques can be migrated to the realm of numeric programs to get perhaps an order of improvement in performance!

As of today, no single ILP processing paradigm has shown a spectacular performance improvement for non-numeric programs. This research is an attempt not only to bridge that gap, but also to lay the foundation for future ILP processors.

### 1.2. Challenges

There are several issues to be tackled in developing a good ILP processing paradigm. First, there are different schools of thought on when the extraction of parallelism is to be done — at compile time or at run time. Each method has its own strengths and shortcomings. We believe that any processing model that relies entirely on compile-time scheduling or on run-time scheduling is very likely to fail because of inherent limitations of both. So the challenge is to use the right mix of compile time and run time extraction of parallelism. The alternatives differ widely, based on the extent to which this question is answered by the compiler or the hardware, and on the manner in which the

compiler-extracted parallelism information is conveyed to the hardware.

Second, studies have found little ILP within a small sequential block of instructions, but significant amounts in large blocks [18, 25, 90, 159]. There are several inter-related factors that contribute to this. Because most programs are written in an imperative language for a sequential machine with a limited number of architectural registers for storing temporary values, instructions of close proximity are very likely to be data dependent, unless they are reodered by the compiler. This means that most of the parallelism can be found only amongst instructions that are further apart in the instruction stream. The obvious way to get to that parallelism is to establish a large window of instructions, and look for parallelism in this window.

The creation of the large window, whether done statically or dynamically, should be accurate. That is, the window should consist mostly of instructions that are *guaranteed* to execute, and not instructions that *might* be executed. Recent work has suggested that, given the basic block sizes and branch prediction accuracies for some common C programs, following a single thread of control while establishing a window may not be sufficient: the maximum ILP that can be extracted from such a window is limited to about 7 [90]. A more complex window, which contains instructions from multiple threads of control might be needed; analysis of the control dependence graph [38,51] of a program can aid in the selection of the threads of control.

Another major challenge in designing the ILP hardware is to decentralize the critical resources in the system. These include the hardware for feeding multiple operations to the execution unit, the hardware for carrying out the inter-operation communication of the many operations in flight, a memory system that can handle multiple accesses simultaneously, and in a dynamically scheduled processor, the hardware for detecting the parallelism at run time.

### 1.3. Contributions of this Thesis

In this thesis we describe a new processing model called the *multiscalar paradigm*; it executes programs by means of the parallel execution of multiple tasks that are derived from a sequential

instruction stream. This is achieved by considering a subgraph of the program's control flow graph to be a task, and executing many such tasks in parallel. The multiple tasks in execution can have both data dependencies and control dependencies between them. The execution model within each task can be a simple, sequential processor. As we will see later in this thesis, such an approach has the synergistic effect of combining the advantages of the sequential and the dataflow execution models, and the advantages of static and dynamic scheduling. Executing multiple subgraphs in parallel, although simple in concept, has powerful implications:

- (1) The hardware mostly involves only the replication of ordinary processors. This allows the critical hardware resources to be decentralized by divide-and-conquer strategy, as will be seen in chapters 3-6. A decentralized hardware realization facilitates clock speeds comparable to contemporary implementations of single-issue processors. Furthermore, it allows expandability.

- (2) The compiler can, as far as possible, attempt to divide the instruction stream into tasks at those points which facilitate the execution of control-independent code in parallel, thereby allowing multiple flows of control. Even if the compiler may not know the exact path that will be taken through a task at run time, it may be fairly sure of the next task that will be executed. Thus, the overall large window can be made very accurate.

- (3) It helps to overlap the execution of blocks of code that are not guaranteed to be (data) independent. The compiler can, of course, attempt to pack dependent instructions into a task, and as far as possible create tasks that are independent so as to improve the processor performance. However, the processing paradigm does not require the tasks to be independent, and this is a significant advantage.

- (4) Because the multiscalar paradigm considers a block of instructions as a single unit (task), the compiler can convey to the hardware more information such as inter-task register dependencies and control flow information. Thus, the hardware need not reconstruct some of the information that was already available at compile time.

- (5) It helps to process and execute multiple branches in the same cycle, which is needed to exploit significant levels of ILP.

- (6) It helps to exploit the localities of communication present in a program.

These statements may appear a bit "rough-and-ready", and may not make much sense before studying the new paradigm. It is precisely this paradigm and its implementation that we study in the ensuing chapters of this thesis.

## 1.4. Organization of the Thesis

We have outlined the important issues pertaining to the design of a high-performance ILP processor, and have now sketched in enough common ground for our study of ILP processing and the multiscalar paradigm to begin. The rest of this thesis is organized as follows. Chapter 2 presents a critique on ILP processing. It describes the fundamental concepts related to ILP processing, and explores how these concepts have been applied in existing ILP paradigms.

Chapter 3 introduces the multiscalar paradigm. It describes the basic philosophy of the paradigm, and compares and contrasts it with other processing paradigms such as the multiprocessor, VLIW, and superscalar paradigms. Chapter 3 also introduces the multiscalar processor, a possible implementation of the multiscalar paradigm.

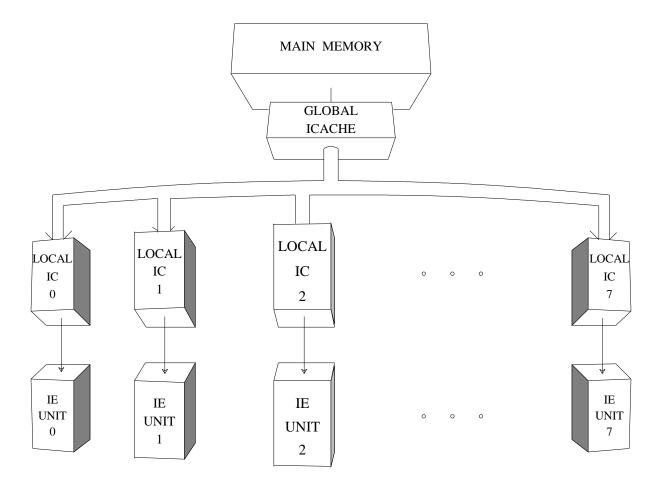

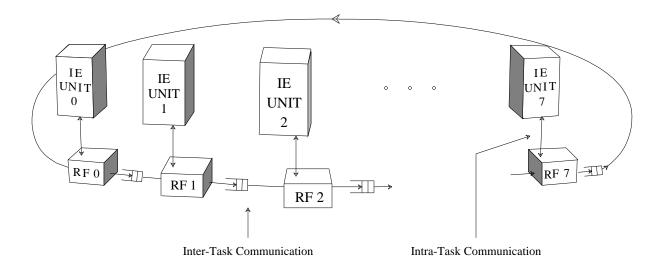

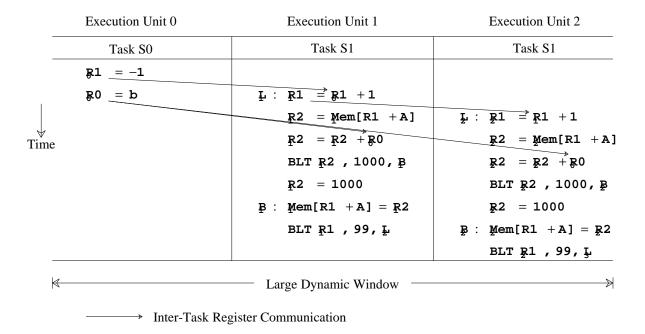

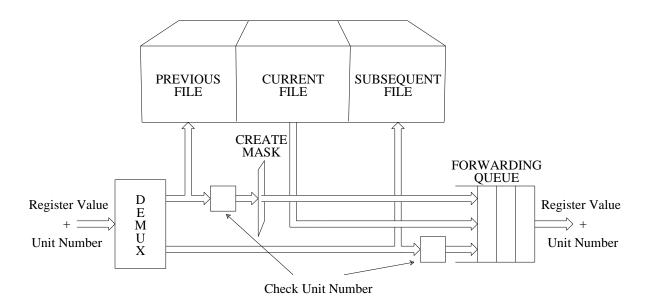

Chapters 4-6 describe the different building blocks of the multiscalar processor. The description includes details of the instruction issue mechanism (distributed instruction caches), the distributed register file, the memory disambiguation unit, and the distributed data memory system. Chapter 4 describes the control unit, the execution units, and the instruction supply mechanism. Chapter 5 describes the distributed inter-operation communication mechanism, namely the replicated register files. Chapter 6 describes the distributed data memory system. It also describes how the multiscalar processor allows out-of-order execution of memory references before disambiguating their addresses, and how it detects any dependency violations brought about by out-of-order execution of memory references. The descriptions in chapters 5-6 are made as generic as possible so that the

schemes developed in the context of the multiscalar processor can be used in other ILP processors too.

Chapter 7 presents the empirical results. It describes the methodology of experimentation, and the software tools developed specifically for studying the multiscalar processor. It presents the performance results of the multiscalar processor, and results showing that the distributed inter-operation communication mechanism in the multiscalar processor exploits localities of communication. Chapter 8 describes the role of the compiler, and the different ways in which the compiler can exploit the idiosyncrasies of the multiscalar paradigm to obtain more performance. Chapter 9 concludes the thesis by pointing out the broad implications of this dissertation.

The ARB mechanism proposed in chapter 6 is very general, and can be used in several execution models. The appendix demonstrates how the ARB can be used in superscalar processors, statically scheduled processors (such as VLIW processors), and small-scale multiprocessors.

# Chapter 2.

# **ILP Processing**

# What is the state of the art in ILP processing?

ILP processing involves a combination of software and hardware techniques to improve performance by executing multiple operations in parallel. This chapter describes the fundamental concepts related to ILP processing, and explores how these concepts have been applied in existing ILP paradigms. This chapter is organized in four sections. Section 2.1 describes the nature of parallelism in programs. Section 2.2 describes the different ways of specifying instruction level parallelism. Section 2.3 describes the fundamental steps involved in ILP processing, including the issues involved in extracting parallelism by software and by hardware. Section 2.4 reviews the state of the art in ILP processing, and provides a critique of the existing ILP paradigms. Section 2.5 recaps the main observations and concludes the chapter.

### 2.1. Program Execution Basics

From an abstract point of view, a program consists of computation operations and communication arcs, operating under control constraints. Computation operations operate on data values and produce new data values, which are communicated to other computation operations. The control constraints decide which parts of the program are executed, and how many times each part is executed. The basic idea behind ILP processing is to use multiple hardware resources to process multiple computation operations as well as multiple communication arcs in parallel so as to reduce the overall execution time. To better understand the nature of ILP in a program, we need to know the constraints on ILP and the ways in which they affect ILP processing.

#### 2.1.1. Constraints on ILP

Data dependencies and control dependencies are the two fundamental constraints on ILP processing. Data dependencies relate to the communication arcs in the program; a data dependency is present when the result of one computation operation is needed by another operation. Data dependencies are true dependencies, and set a theoretical limit on the ILP that can be extracted from a program. A control dependency exists between two operations if the execution of one operation can prevent the execution of the other. Control dependencies manifest by way of conditionals in the program.

Because a control dependency can prevent the execution of other operations, it can introduce or eliminate data dependencies when a program is executed. Data dependencies can in turn affect control decisions that depend on them. This might lead one to suspect that control dependencies and data dependencies are indeed two sides of the same coin.

Control dependencies can be converted to data dependencies and vice versa

A data dependency between two operations can be trivially converted to a control dependency by specifying an execution ordering for the two computation operations. Techniques for converting control dependencies to data dependencies (e.g. if-conversion) are described in section 2.3.2.1.

The effect of data dependencies on parallelism get modulated based on the manner in which communication is handled. Depending on the way computation operations are mapped onto a processing structure, the communication arcs (data dependencies) get "stretched" or "shrunk", causing changes in the communication costs, because it takes more time to send values over a distance.

### 2.1.2. Program Representations

Irrespective of the programming language in which a program is written, for purposes of parallelism extraction, the compiler uses different representations for denoting the computations, the communication, and the controls embedded in a program. We shall briefly discuss the important types of representations. One of them is the *data flow graph (DFG)*, which is a directed graph whose nodes denote computation operations and whose arcs denote the communication of values, which define the necessary sequencing constraints. Control constraints are represented by selective routing of data among the nodes, using *switch* and *merge* nodes.

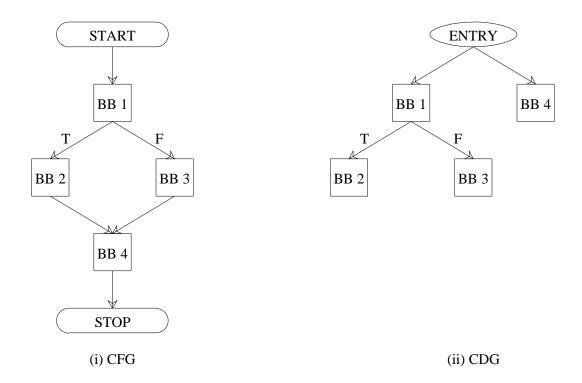

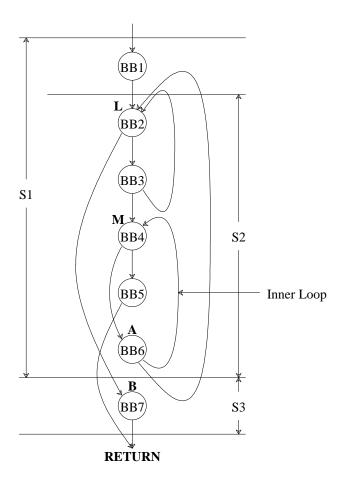

Another way of representing the attributes of a program is the *control flow graph (CFG)*, which is a directed graph whose nodes denote basic blocks (straight-line codes with no branches into or out of the middle of the block) and whose arcs denote the flow of control between them. Within a basic block, control is assumed to flow sequentially. Figure 2.1(i) shows an example CFG containing four basic blocks, marked BB1-BB4; the CFG contains a unique entry node called START and a unique exit node called STOP. In a control flow graph, a node *X* is said to be *post-dominated* by a node *Y* if every directed path from *X* to STOP (not including *X*) contains *Y* [51].

A third type of representation is the *program dependence graph (PDG)*, which explicitly represents the control dependencies and data dependencies for every operation in a program [51,76]. The control dependencies are represented by a subgraph called *control dependence graph (CDG)*, and the data dependencies are represented by another subgraph called *data dependence graph (DDG)*. Control dependencies are derived from the control flow graph by constructing its post-dominator tree [51]. Figure 2.1(ii) shows the CDG of the CFG shown in Figure 2.1(i). Notice that *control parallelism* exists between basic blocks 1 and 4, *i.e.*, these two blocks are control independent. Data dependencies are derived by performing a data flow analysis of the program [7].

# 2.2. Program Specification and Execution Models

ILP processing involves a sequence of steps, some of which need to be done by software/programmer and some of which need to be done by hardware. In between comes extraction of parallelism, which can be done either by the compiler or by the hardware or by both. The instruction set architecture (ISA) of an ILP processor is a function of where the boundary is drawn between

Figure 2.1: An Example Control Flow Graph (CFG) and its Control Dependence Graph (CDG)

what is done in software and what is done in hardware. The ISA is also a function of the manner in which information regarding parallelism is communicated by the compiler to the hardware through the program. In this regard, we consider two attributes to classify existing ILP architectures and their implementations. They are: (i) program specification order, and (ii) program execution order. These two attributes capture information about the extent to which static scheduling, dynamic scheduling, and combinations thereof are performed in different ILP processing paradigms.

### 2.2.1. Program Specification Order

### 2.2.1.1. Control-Driven Specification

The instructions in a program can imply either a static ordering or no ordering. When the instructions imply a static ordering, the corresponding ISA is said to be *control-driven*, and control is assumed to step through instructions one at a time. Communication is also control-driven; computation results do not directly proceed to the computation operations that need them, but are rather stored in a storage, for instance at the output of the functional units, in a set of registers, or in a set of memory locations. Control-driven architectures have the notion of a "present state" after each instruction is executed and the result(s) stored in the designated storage locations. The next instruction in the ordering is guaranteed to have its operands ready when control reaches it. Thus, all data dependencies are automatically specified by converting them to control dependencies! Generally, the implied program ordering is sequential ordering, with provisions to change the ordering by means of branch operations. Examples for control-driven specification are the VLIW, vector, and superscalar processors.

Control-driven specification allows communication to be specified by means of a shared storage structure. This has several implications. First, it gives rise to storage conflicts (*i.e.*, anti- and output dependencies). Second, execution of a conditional branch operation does not involve any routing of data, and involves only changing the value of the control sequencer. Third, it necessitates the construction of data access paths, computation operations to manipulate them, and algorithms to manage storage space, but therein lies the strength of static ordering. Static ordering can be used to introduce localities of communication, which can be exploited by hardware means to reduce the costs of communication, and to manage hardware resources properly. This has the effect of combining several adjacent computation operations of the program into one, because the communication arcs between them become very short when temporal locality is exploited by hardware means. Lastly, control-driven means "compiler-driven". The compiler can even analyze the entire program, and do some scheduling. The lesson learned from past experiences of the computer architecture community is to

make use of whatever support and scheduling the compiler can do.

Multiple Flows of Control: The discussion carried out so far might suggest that in control-driven specification, the execution of one operation triggers the execution of exactly one other operation — i.e., a single flow of control. However, this is not the case. In control-driven specification, control need not step through operations one at a time; each instruction could itself consist of many operations as in the VLIW paradigm. It is also possible to specify multiple flows of control in which the execution of an instruction triggers multiple instructions. An example for program specification involving multiple flows of control is the multiprocessing paradigm.

Parallelism Specification: In control-driven specification, the compiler can extract parallelism. The compiler-extracted parallelism can be specified in the program and conveyed to the execution hardware in many ways. One way is to use data parallel instructions (such as vector instructions) in which a single operation is specified on multiple data elements. Data parallel instructions are highly space-efficient; however, they are useful only for specifying the regular parallelism present in numeric programs, and are not of much use for specifying the irregular parallelism present in non-numeric programs. For specifying irregular parallelism, one can use horizontal instructions in which multiple operations are specified side by side in a single instruction. This is the specification used by the VLIW paradigm. Yet another type of parallelism specification is the one used by multiprocessors. In multiprocessors, the compiler specifies control-independent tasks, which can be executed by the hardware in parallel. Finally, in the case of the superscalar paradigm, the compiler can place independent instructions adjacent to each other in order that the superscalar hardware scheduler encounters them simultaneously.

### 2.2.1.2. Data-Driven Specification

When a program does not imply any particular static ordering, it is called *data-driven* specification. In this specification, communication is specified directly in the program. Computation results directly proceed to the computation operations that need them, and data are directly held

inside instructions, instead of being stored elsewhere. In data-driven specification, control dependencies are handled by switch nodes and merge nodes, which route data conditionally. Thus, all control dependencies are automatically specified by converting them to data dependencies!

The perceived advantage of data-driven specification is that it helps to express the maximum amount of parallelism present in an application. Ironically, therein lies its weakness! Data-driven specification, in an attempt to express the maximum amount of parallelism to the hardware, refrains from doing any static scheduling, and pushes the scheduling task entirely to the hardware. Lack of a static ordering has other ramifications as well. Data-driven specification suffers from the inability to express critical sections and imperative operations that are essential for the efficient execution of operating system functions, such as resource management [36, 114]. Furthermore, in data-driven specification, data tokens have to be routed through control-decision points such as switch nodes and merge nodes, and often get collected at these control-decision points, waiting for the appropriate control decisions to be taken.

Data-Driven Specification with Control-Driven Tasks: In an attempt to capture the benefits of control-driven specification, researchers have proposed using control-driven specification at the lower level with data-driven specification at the higher level [77,113]. In this specification, the dataflow graph is partitioned into different regions, each of which is scheduled independently at compile time. Within a region, control flows sequentially, whereas the execution of a region is triggered by interregion data availability.

#### 2.2.2. Program Execution Order

Program execution order is the ordering adopted by the execution hardware. If the hardware follows an execution order given by the program control flow, then it is called *control-driven execution*. If the hardware follows an execution order based on data availability, then it is called *data-driven execution*. In control-driven execution, a computation operation is triggered (*i.e.*, becomes ready for execution) when the control sequencer reaches that operation. Examples for control-driven

execution are the traditional von Neumann, VLIW, and vector processors. In data-driven execution, a computation operation is triggered when all of its input operands have arrived. Examples for data-driven execution are the dataflow machines. Although existing paradigms that use data-driven specification have also used data-driven execution, this need not be the case. It is theoretically possible to have a hardware that takes a data-driven specification, converts it into control-driven specification and executes it in a control-driven manner.

Data-driven execution offers a lot of opportunity to execute multiple operations in parallel, because it introduces no artificial control restraints on parallel processing. However, the costs of freedom take their toll, which manifest as a host of overheads, rendering data-driven execution performance-ineffective. In an attempt to extract parallelism at run time, then, the data-driven hardware gets bogged down in a truly global scheduling every cycle. A significant communication overhead also accrues, as data-driven execution does not attempt to exploit localities of communication. Furthermore, data-driven execution needs special mechanisms to detect operand availability, to match results with needy operations, and to enable the execution of ready operations in an asynchronous manner. Finally, data-driven execution performs random scheduling; if many operations are ready for execution, then based on resource availability, some operations are selected in random for execution, without any consideration for the critical path. This is because the hardware cannot see what happens beyond the next cycle when no static ordering has been presented to it.

Control-driven execution definitely restrains parallelism. The advantage of control-driven execution is that after an instruction is executed, there is no need to search for the next instruction to be executed, which helps to reduce the hardware complexity significantly. Further, it has the capability to exploit localities of communication. In an attempt to combine the good aspects of control-driven execution and data-driven execution, processing paradigms have been proposed to combine control-driven execution and data-driven execution. Prime examples are the superscalar processors, which do data-driven execution within a window of operations obtained by control-driven fetching of instructions. Multiprocessors also use a combination of control-driven execution and data-driven execution, but in a different manner. In a multiprocessor, each processor performs control-driven execution, but

inter-processor communication and synchronization are performed in a data-driven manner (with some hardware support).

## 2.3. Fundamentals of ILP Processing

Converting a high-level language program into one that a machine can execute involves taking several decisions at various levels. Parallelism exploitation involves additional decisions on top of this. The fundamental aspect in ILP processing is:

Given a program graph with control and data constraints, arrive at a good execution schedule in which multiple computation operations are executed in a cycle as allowed by the resource constraints in the machine.

Arriving at a good schedule involves manipulations on the program graph, taking into consideration several aspects such as the ISA and the resources in the machine. Since there can only be a finite amount of fast storage (such as registers) for temporarily storing the intermediate computation values, the values have to be either consumed immediately or stored away into some form of backup storage (such as main memory), creating additional communication arcs. Thus, the challenge in ILP processing is not only to identify a large number of independent operations to be executed every cycle from a large block of computation operations having intricate control dependencies and data dependencies, but also reduce the inter-operation communication costs and the costs of storing temporary results. A good paradigm should not only attempt to increase the number of operations executed in parallel, but also decrease the inter-operation communication costs by reducing the communication distances and the temporary storing away of values, thereby allowing the hardware to be expanded as allowed by technology improvements in hardware and software.

Optimal scheduling (under finite resource constraints) is an NP-complete problem [32], necessitating the use of heuristics to take decisions. Although programmers can ease scheduling by expressing some of the parallelism present in programs by using a non-standard high-level language (HLL),

the major scheduling decisions have to be taken by the compiler, by the hardware, or by both of them. There are different trade-offs in taking the decisions at programming time, at compile time, and at run time, as illustrated in Table 2.1.

A program's input (which can affect scheduling decisions) are available only at run-time when the program is executed, leaving compilers to work with conservative assumptions while taking scheduling decisions. Run-time deviations from the compile-time assumptions render the quality of

Table 2.1: Trade-offs in Taking Decisions at Programming Time, Compile Time, and Run Time

| Taking Decisions at                                                                                           |                                                                                        |                                                                                                                                           |  |  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Programming Time                                                                                              | Compile Time                                                                           | Run Time                                                                                                                                  |  |  |

| No compiler complexity.  No hardware complexity.                                                              | No hardware complexity.                                                                | Introduces hardware complexity, with potential cycle time increase.  The benefit should more than make up for this increase in cycle time |  |  |

| Only macro-level analysis.  Difficult to reason about parallelism, specific ISAs, & specific implementations. | Global analysis possible.                                                              | Only tunnel vision possible, with no increase in hardware complexity.                                                                     |  |  |

| Conservative due to lack of run-time information.                                                             | Conservative due to lack of run-time information. Difficult to guarantee independence. | Has complete run-time information within the "tunnel", and can make well-informed decisions within the "tunnel".                          |  |  |

| Tailored for a specific. HLL program                                                                          | HLL compatible. Tailored for specific ISA.                                             | HLL compatible. Object code compatible.                                                                                                   |  |  |

the compiler-generated schedule poor, and increase the program execution time significantly. On the other hand, any scheduling decisions taken by the hardware could increase the hardware complexity, and hence the machine cycle time, making it practical for the hardware to analyze only small portions of the program at a time. Different ILP processing paradigms differ in the extent to which scheduling decisions are taken by the compiler or by the hardware.

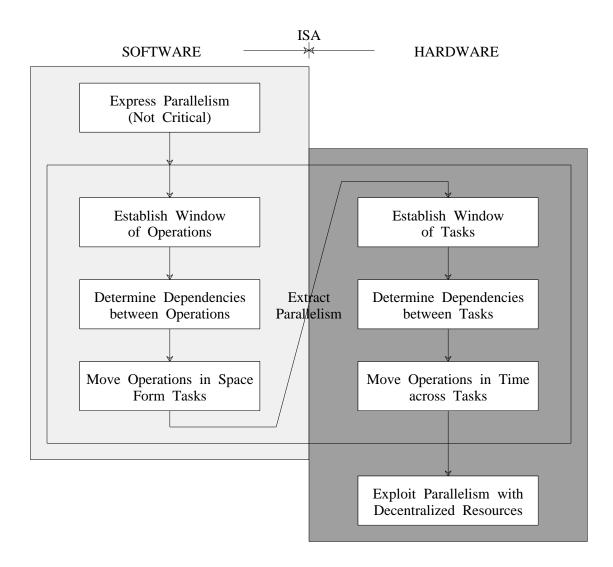

In this section, we explore the different steps involved in ILP processing. To explore the full possibilities of what can be done by the compiler and what can be done by the hardware, this discussion assumes a combination of control-driven specification and data-driven execution. The sequence of processes involved in ILP processing can be grouped under the four steps listed below:

- (i) Expressing ILP (done by the programmer),

- (ii) Extracting ILP by software,

- (iii) Extracting ILP by hardware, and

- (iv) Exploiting ILP (done by the hardware).

In our opinion, these four steps are generally orthogonal to each other, although hardware mechanisms for extracting ILP (step 3) and those for exploiting ILP (step 4) are often integrated in hardware implementations. We shall look into each of the four steps in more detail.

### 2.3.1. Expressing ILP

The programmer can choose to express the parallelism present in an application by using appropriate algorithms, programming languages, and data structures. This is particularly useful for expressing the control parallelism present in an application. For a given application, some algorithms have more inherent parallelism than others. Similarly, some of the control dependencies in a program are an artifact of the programming paradigm used; dataflow languages such as Id [17] are tailored to express the parallelism present in an application, and do not introduce artificial control dependencies. One example where data structures help in expressing parallelism is the use of arrays instead of linked lists. Information about data parallelism can also be expressed by the programmer, by means of assertions. In many situations, the programmer may not be able to reason about and express all the

parallelism in an application, in which case the compiler can attempt to expose some of the hidden parallelism, particularly the control parallelism in the program. These are described in detail in section 2.3.2.1.

### 2.3.2. Extracting ILP by Software

Extraction of ILP can be performed by software and by hardware. The motivation for using software to extract ILP is to keep the hardware simpler, and therefore faster. The motivation for using hardware to extract ILP (c.f. Section 2.3.3) is to extract that parallelism which can be detected only at run time. A central premise of this thesis is that these two methods are not mutually exclusive, and can both be used in conjunction to extract as much parallelism as possible.

There are three fundamental steps in extracting ILP from a program:

- (1) Establish a window of operations.

- (2) Determine and minimize dependencies between operations in this window.

- (3) Schedule operations.

Below, we explain each of these steps in more detail.

### 2.3.2.1. Establishing a Window of Operations

The first step in extracting ILP from a program at compile time is to establish a path or a subgraph in the program's CFG, called an *operation window*. The two important criteria in establishing the operation window are that the window should be both large and accurate. Small windows tend to have small amounts of parallelism as discussed in section 1.2. Control dependencies caused by statically unpredictable conditional branches are the major hurdle in establishing a large and accurate static window. To overcome this, compilers typically analyze both paths of a conditional branch or do a prediction as to which direction the branch is most likely to go. Because an important component of most window-establishment schemes is the accurate prediction of conditional branches, a considerable amount of research has gone into better branch prediction techniques. Initial static

prediction schemes were based on branch opcodes, and were not accurate. Now, static prediction schemes are much more sophisticated, and use profile information or heuristics to take decisions [28, 75, 98, 118, 160].

In addition to branch prediction, the compiler uses several other techniques to overcome the effects of control dependencies. Some of these techniques are if-conversion, loop unrolling, loop peeling, loop conditioning, loop exchange [12], function inlining [28, 85], replacing a set of IF-THEN statements by a jump table [129], and even changing data structures. All these techniques modify the CFG of the program, mostly by reducing the number of control decision points in the CFG. We shall review some of these schemes in terms of the type of modifications done to the CFG and how the modifications are incorporated.

**Loop Unrolling:** Loop unrolling is a technique used to enlarge the body of (typically) small loops. The key idea is to combine multiple iterations of the loop into a single iteration, and decrease the loop iterations proportionately, in order to permit better loop body pipelining and decrease the overhead of branch execution and induction variable update.

Loop Peeling: Loop peeling is a technique used to reduce dependencies when there is a control flow into the middle of a loop from outside the loop. If there is a control flow into the middle of a loop, then that control flow is effectively into the first iteration of the loop. Loop peeling involves peeling off this first iteration out of the loop by duplicating the loop body, and reducing the loop iteration count by one. Now, any dependencies that were carried into the loop through the previous control flow (into the loop) belong entirely to the peeled iteration, potentially allowing more static scheduling to be done.

Function Inlining: The essence of function inlining is to remove from the CFG of a program control flow alterations caused by function calls and returns. The procedure for doing inlining is to take a program's call graph and replace calls to the leaf functions (especially the ones that are called frequently) by the functions' body, and then repeating the process. Function inlining provides an enlarged window for code optimization, register allocation, and code scheduling. Most current

21

compilers do function inlining as an optimization.

If-Conversion: A control dependency from operation  $I_1$  to operation  $I_2$  can be converted to a

data dependency by changing  $I_2$  to a conditional execution operation whose execution is data

dependent on a guard. The guard for a conditional execution operation is a Boolean expression that

represents the conditions under which the operation is executed, and can be stored in a general pur-

pose register or a condition code register. Thus, instead of the two operations

$I_1$ : if (condition) branch to  $I_2$

I<sub>2</sub>: computation operation

we can have,

$I_1$ : guard  $\leftarrow$  condition is true

I2: if (guard) computation operation

This conversion process is called if-conversion [13, 14, 21, 35, 71, 129]. Because the guard is an input

operand to  $I_2$ , the relationship between  $I_1$  and  $I_2$  has now been converted from a control depen-

dency to a data dependency. One potential problem with if-conversion, which prevents its pervasive

application in a program, is that the if-converted instructions need to be executed irrespective of

whether their execution is required or not.

2.3.2.2. Determining and Minimizing Dependencies

Once a window of operations has been established, the next step is to determine the data depen-

dencies between the operations in the window, which exist through (pseudo)registers and memory

locations. If register allocation has already been performed, then this step involves determining the

register storage dependencies (anti- and output dependencies) as well.

Static Memory Address Disambiguation: Static memory address disambiguation is the process

of determining if two memory references (at least one of which is a store) could ever point to the

same memory location in any valid execution of the program. Static disambiguation is a hard task as memory addresses could correspond to pointer variables, whose values might change at run time. Two memory references may be dependent in one instance of program execution and not dependent in another instance, and static disambiguation has to consider all possible executions of the program. Various techniques have been proposed to do static disambiguation of memory references involving arrays [11, 19, 20, 49, 105, 163]. These techniques involve the use of conventional flow analyses of reaching definitions to derive symbolic expressions for array indexes. The symbolic expressions contain compile-time constants, loop-invariants, and induction variables, as well as variables whose values cannot be derived at compile time. To disambiguate two references, first their symbolic expressions are checked for equality. If the expressions are equal, then it means that the two references always conflict. If not, the two symbolic expressions are symbolically equated and the resulting diophantine equation is solved. If there are (integer) solutions to the equation, then it means that the two references might point to the same memory location during program execution, and a potential hazard has to be assumed. Otherwise, the two references are guaranteed not to conflict. For arbitrary multi-dimensional arrays and complex array subscripts, unfortunately, these tests can often be too conservative; several techniques have been proposed to produce exact dependence relations for certain subclasses of multi-dimensional arrays [62, 97]. Good static memory disambiguation is fundamental to the success of any parallelizing/vectorizing/optimizing compiler [14, 49, 54, 86, 94]. Existing static disambiguation techniques are limited to single procedures, and do not perform much of inter-procedural analysis. Moreover, existing static techniques are suitable only for memory references involving array subscripts, and not suitable for those references involving data types such as unions and pointers. Hence they are useful mainly for a class of scientific programs. Ordinary nonnumerical applications, however, abound with unions and pointers [30, 67, 70, 92]. Although recent work has suggested that some compile-time analysis could be done with suitable annotations from the programmer [49, 68, 72], it appears that accurate static disambiguation for arbitrary programs written in arbitrary languages with pointers is unlikely without considerable advances in compiler technology.

23

Once the dependencies in the window are determined, the dependencies can be minimized by techniques such as software register renaming (if register allocation has been performed), induction variable expansion, and accumulator variable expansion. A description of some of these techniques is given below.

Software Register Renaming: Reuse of storage names (variables by the programmer and registers by the compiler) introduces artificial anti- and output dependencies, and restricts the static scheduler's opportunities for reordering operations. For instance, consider the code sequence given below.

$$I_1: R1 = R1 + R2$$

$$I_2: R3 = R1 + R4$$

$$I_3$$

: R1 = R4

In this code sequence, there is an anti-dependency between  $\mathbf{I}_1$  and  $\mathbf{I}_3$  and between  $\mathbf{I}_2$  and  $\mathbf{I}_3$  because of the reuse of register  $\mathbf{R}\mathbf{1}$ . Similarly, there is an output dependency between  $\mathbf{I}_1$  and  $\mathbf{I}_3$  through register  $\mathbf{R}\mathbf{1}$ . Because of these dependencies,  $\mathbf{I}_3$  cannot be executed concurrently or before  $\mathbf{I}_2$  or  $\mathbf{I}_1$ . Many of these artificial dependencies can be eliminated with software register renaming. The idea behind software register renaming is to use a unique architectural register for each assignment in the window, in similar spirit to static single assignment [38]. In the above code, by replacing the assignment to register  $\mathbf{R}\mathbf{1}$  by an assignment to register  $\mathbf{R}\mathbf{5}$ , both the anti- and output dependencies are eliminated, allowing  $\mathbf{I}_3$  to be scheduled before  $\mathbf{I}_2$  and  $\mathbf{I}_1$  as shown below.

$$I_3$$

: R5 = R4

$$I_1: R1 = R1 + R2$$

$$I_2$$

: R3 = R1 + R4

*Induction Variable Expansion:* Induction variables, used within loops to index through loop iterations and arrays, can cause anti-, output, and flow dependencies between different iterations of a loop. Induction variable expansion is a technique to reduce the effects of such dependencies caused by induction variables. The main idea is to eliminate re-assignments of the induction variable within the

window, by giving each re-assignment of the induction variable a new induction variable name, thereby eliminating all dependencies due to multiple assignments. Of course, the newly introduced induction variables have to be properly initialized. Consider the loop shown in Figure 2.2(i). Figure 2.2(ii) shows this loop unrolled twice. The statements in the unrolled loop cannot be reordered because of the dependencies through the induction variable i. However, we can use two different induction variables, i0 and i1, to redress the effects of multiple assignments to the induction variable, and reassign the induction variables as shown in Figure 2.2(iii).

```

i = 0

i = 0

i0 = 0;

i1 = 1

while (i < 100)

while (i < 100)

while (i0 < 100)

{

{

{

A[i] += 10

A[i] += 10

A[i0] += 10; A[i1] += 10

i0 += 2; i1 += 2

i++

}

}

A[i] += 10

i++

}

(i)

(ii)

(iii)

```

Figure 2.2. Example Showing the Benefit of Induction Variable Expansion

(i) An Example Loop; (ii) The Loop Unrolled Twice;

(iii) Induction Variable Expansion

#### 2.3.2.3. Scheduling Operations

Once an operation window is established, and the register dependencies and memory dependencies in the window are determined and minimized, the next step is to move independent operations up in the CFG, and schedule them in parallel with other operations so that they can be initiated and executed earlier than they would be in a sequential execution. If a static scheduler uses a basic block as the operation window, then the scheduling is called basic block scheduling. If the scheduler uses multiple basic blocks as the operation window, then the scheduling is called global scheduling. Basic block schedulers are simpler than global schedulers, as they do not deal with control dependencies; however, their use for extracting parallelism is limited. Global scheduling is more useful, as they consider large operation windows. Several global scheduling techniques have been developed over the years to establish large static windows and to carry out static code motions in the windows. These include: trace scheduling [53], percolation scheduling [57, 107], superblock scheduling [28], software pipelining [45, 89, 102, 103, 161], perfect pipelining [8, 9], boosting [141-143], and sentinel scheduling [95].

Trace Scheduling: The key idea of trace scheduling is to reduce the execution time along the more frequently executed paths, possibly by increasing the execution time in the less frequently executed paths. Originally developed for microcode compaction [53], trace scheduling later found application in ILP processing [34, 49]. Its methodology in the context of ILP processing is as follows: The compiler forms the operation window by selecting from an acyclic part of the CFG the most likely path, called trace, that will be taken at run time. The compiler typically uses profile-based estimates of conditional branch outcomes to make judicious decisions in selecting the traces. There may be conditional branches out of the middle of the trace and branches into the middle of the trace from outside. However, the trace is treated and scheduled as if there were no control dependencies within the trace; special compensation codes are inserted on the off-trace branch edges to offset any changes that could affect program correctness. Then the next likely path is selected and scheduled, and the process is continued until the entire program is scheduled. Nested loops are scheduled by first applying trace scheduling on the inner loop body, and then treating the inner loop as a single node within the

enclosing outer loop. Trace scheduling is a powerful technique, which is very useful for numeric programs in which there are a few most likely executed paths. In non-numeric programs, however, many conditional branches are statically difficult to predict, let alone have a high probability of branching in any one direction.

Percolation Scheduling: Percolation scheduling considers a subgraph of the CFG (such as an entire function) as a window, using a system of semantics-preserving transformations for moving operations between adjacent blocks [107]. Repeated application of the transformations allows operations to "percolate" towards the top of the program, irrespective of their starting point. A complete set of semantics-preserving transformations for moving operations between adjacent blocks is described in [107]. Ebcioglu and Nakatani describe an enhanced implementation of percolation scheduling for VLIW machines having conditional evaluation capabilities [47]. In their implementation of percolation scheduling, a code motion across a large number of basic blocks is allowed only if each of the pair-wise transformations is beneficial.

Superblock Scheduling: Superblock scheduling [27,28] is a variant of trace scheduling. A superblock is a trace with a unique entry point and one or more exit points, and is the operation window used by the compiler to extract parallelism. Superblocks are formed by identifying traces using profile information, and then using tail duplication to eliminate any control entries into the middle of the trace. (Tail duplication means making a copy of the trace from the side entrance to the end of the trace, and redirecting the incoming control flow path to that copy.) In order to generate large traces (preferably along the most frequently executed paths of the program), techniques such as branch target expansion, loop peeling, and loop unrolling are used. Once a superblock is formed, the anti-, output, and flow dependencies within the superblock are reduced by techniques such as software register renaming, induction variable expansion, and accumulator variable expansion. Finally, scheduling is performed within the superblock by constructing the dependence graph and then doing list scheduling. In order to reduce the effect of control dependencies, operations are speculatively moved above conditional branches.

Hyperblock Scheduling: In hyperblock scheduling, the operation window is a hyperblock. A hyperblock is an enhancement on superblock [96]. A hyperblock is a set of predicated basic blocks in which control may enter only from the top, but may exit from one or more points. The difference between a hyperblock and a superblock is that a superblock contains instructions from only instructions from one path of control, whereas a hyperblock contains instructions from multiple paths of control. If-conversion is used to convert control dependencies within the hyperblock to data dependencies. The predicated instructions are reordered without consideration to the availability of their predicates. The compiler assumes architectural support to guarantee correct execution.

Software Pipelining: The static scheduling techniques described so far deal mostly with operation windows involving acyclic codes. Software pipelining is a static technique for scheduling windows involving loops. The principle behind software pipelining is to overlap or pipeline different iterations of the loop body. The methodology is to do loop unrolling and scheduling of successive iterations until a repeating pattern is detected in the schedule. The repeating pattern can be re-rolled to yield a loop whose body is the repeating schedule. The resulting software pipeline schedule consists of a prologue, a kernel, and an epilogue, and its execution is similar to that of a sequence of chained vector instructions. Figure 2.3 illustrates how software pipelining is applied to a loop. Figure 2.3(i) shows an example loop; Figure 2.3(ii) shows the loop unrolled three times. Scheduling is done on the unrolled loop, and the re-rolled loop is shown in Figure 2.3(iii). Different techniques have been proposed to do software pipelining: perfect pipelining [10], enhanced pipeline scheduling [47], GURPR\* [149], modulo scheduling [48, 124], and polycyclic scheduling [125].

**Boosting:** Boosting is a technique for statically specifying speculative execution [141-143]. Conceptually, boosting converts control dependencies into data dependencies using a technique similar to if-conversion, and then executes the if-converted operations in a speculative manner before their guards are available. (The guard of a boosted operation includes information about the branches on which the boosted operation is control dependent and the statically predicted direction of each of these branches.) Extra buffering is provided in the processor to hold the effect of speculative

```

R0 = 0

R0 = 0

L: Load R1

L: Load R1

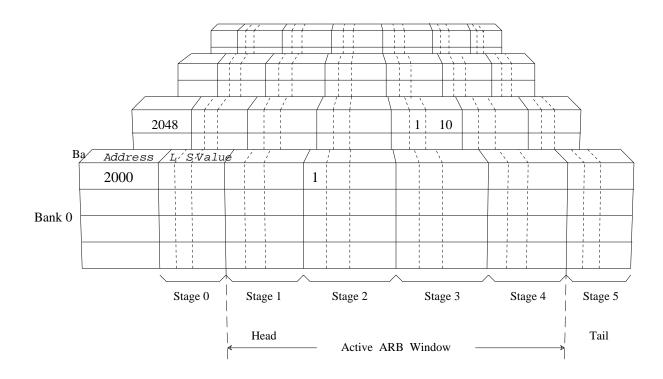

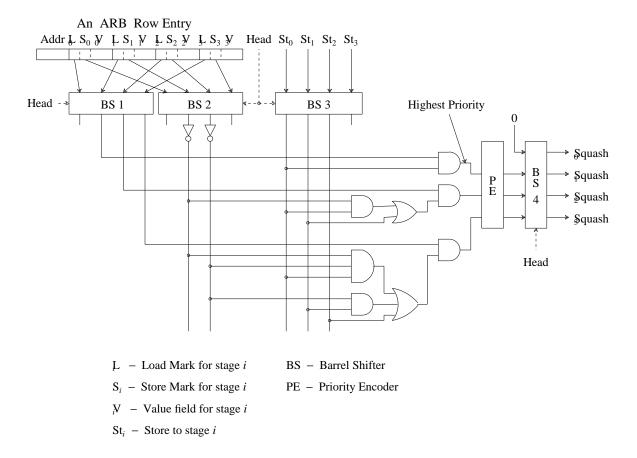

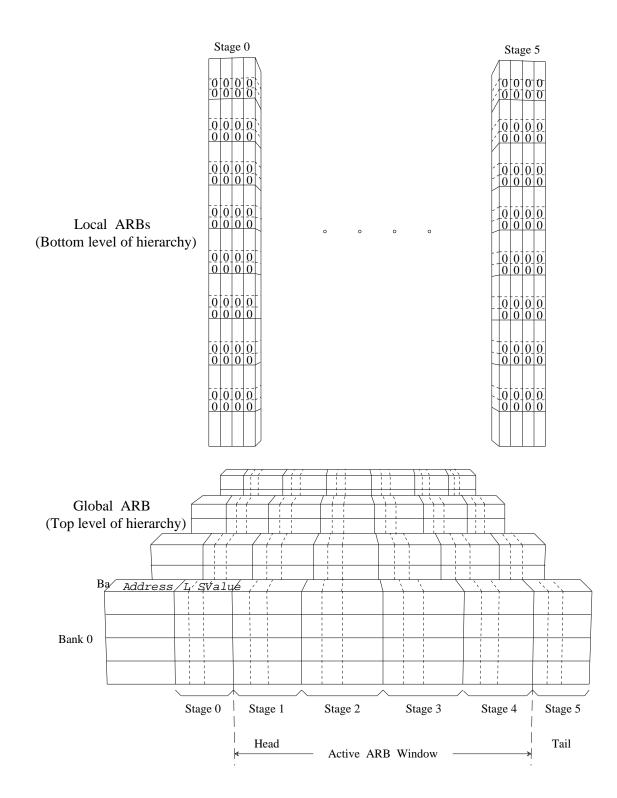

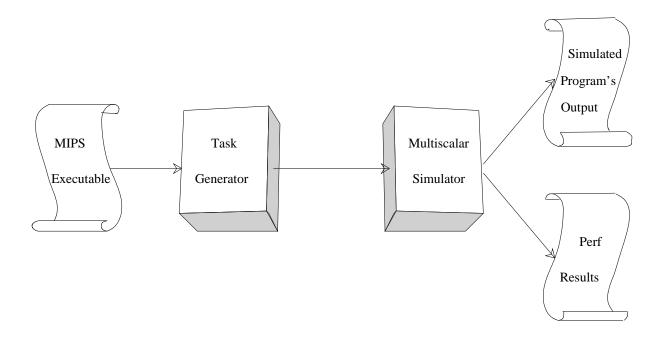

R2 = R1 + R3