## PRE-EXECUTION VIA SPECULATIVE DATA-DRIVEN MULTITHREADING

BY

AMIR ROTH

A dissertation submitted in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the University of Wisconsin-Madison

2001

© Copyright by Amir Roth 2001 All Rights Reserved

#### Abstract

This dissertation introduces *pre-execution*, a novel technique for accelerating sequential programs. Pre-execution directly attacks the instructions that cause performance problems—mis-predicted branches and cache missing loads. In pre-execution, future branch outcomes and load addresses are computed on the side and the results are fed to the main program. In doing so, the main program is spared from having to incur the full computation latencies of these instructions. Pre-execution exploits *out-of-order fetch* and *decoupling*. Fetching and executing only critical load and branch computations while skipping over all unrelated instructions allows pre-execution to compute values faster than the main program. Decoupling, doing so in a separate thread, isolates stalls that occur in these computations so that they do not directly impact the main program thread.

This dissertation describes *speculative data-driven multithreading (DDMT)*, an implementation of pre-execution. DDMT implements the runtime component of pre-execution—responsible for pre-executing computations and communicating the results to the main program—as an extension to a superscalar processor. In addition to using the single cache hierarchy to allow pre-executing computations to prefetch for the main program, DDMT stores individual pre-executed instruction results in the shared physical register and then passes them one-by-one to the main program via a novel modification to register renaming called *register integration*.

For DDMT's setup component—responsible for finding load and branch computations and conveying them to the runtime component—this dissertation introduces an algorithm for automatically extracting performance-enhancing computations from program traces. The algorithm evaluates a benefit-cost function over all candidate computations in a trace and chooses those that maximize benefit (latency tolerance) while minimizing cost (execution overhead). The algorithm is formulated to permit software, hardware, and hybrid implementations.

The dissertation includes a simulation-driven performance evaluation of DDMT. Our results show that DDMT achieves 10% to 15% performance improvements for general-purpose integer programs running on an aggressive baseline processor with large caches, with the potential for greater improvements on likely future processor designs. We conclude that pre-execution and DDMT are promising technologies that merit consideration for inclusion in future machines.

## Acknowledgements

Many people deserve thanks for helping me through the often frustrating, sometimes wonderful world of graduate school. First among these is my wife, Marci. Marci and I came to Wisconsin together in 1995. In the six years since, she has continuously supported me, repeatedly comforted me, occasionally dissuaded me from dropping out, and once even agreed to marry me. She is my rock. She is my best friend. She is my far better half and certainly far better than I deserve. I can imagine neither the last six years nor the next sixty without her.

My parents, Itzhak and Zipora, also deserve thanks, not only for the love and support they have given me—over the phone, through the mail, and occasionally in person—for the last six years, but for everything they have done for me during the previous twenty-three. I can only hope that I will be as good a parent to my future children as they have been to me. My sister Nurit and my brother Eatai have always been there when I needed them, and I will always be there for them.

I may not like to admit it, but I owe much of my academic and professional development to my advisor, Guri Sohi. Guri took me on in 1996 after, in his own words, "no one else would work with me." His handling of me in the five years since is best summed by the Rolling Stones: I may not have always gotten what I wanted, but I always got exactly what I needed. Guri has given me continuous support and provided me with countless opportunities. His technical insights have been inspiring and his confidence in my abilities and my work has been uplifting. He has taught me how to write, how to ask insightful questions and how to stand up for my ideas. Oh yes, it was his 552 class that turned me on to computer architecture in the first place. I respect any person who can put up with me for one week, much less five years, but my respect for him goes far beyond that. I hope he knows how much I appreciate everything he has done for me and everything he has made me do for myself.

I want to thank the other members of my thesis committee. Charlie Fischer, Jim Goodman, Mark Hill and Jim Smith not only agreed to read (or at least skim) this monstrosity, but also to sign my defense warrant. More importantly, they have provided me with valuable feedback and advice, whenever I asked for it, about any topic whatsoever. I also want to thank Charlie for assisting Milo Martin and myself with our first research venture and for letting me drive his BMW, Jim Smith for his friendly barbs and for embarrassing me cardiovascularly despite being 20 years my senior, and Mark for being the perfect counterpoint to Guri. In his two years in the department, Ras Bodik has also been a good friend while showing me by example how an assistant professor is supposed to act.

Most of my technical growth has come from interactions with other students rather than with faculty. Andreas Moshovos helped me organize my writing and my thinking and generally showed me the ropes during my early rounds of research. Stephanos Kaxiras, Subbarao Palacharla and Avinash Sodani were also helpful in those early years. More recently, I have needed less hand-holding and more sound-boarding. Fortunately, the University of Wisconsin has some of the best architecture sound-boards in the world. I want to thank Adam Butts, Brian Fields, Milo Martin, Ravi Rajwar, Dan Sorin and Craig Zilles for reading my paper drafts, attending my practice talks, helping me think through my ideas, listening to my complaints, sharing in my academic successes and failures, and allowing me to share in theirs. They have been as good an intellectual support system as one can ask for, and they have contributed much more than technical input to my graduate school experience. I want to thank Milo, in particular, for essentially handing me my first conference publication, yet still speaking to me after that experience.

I have made many friends in the past six years. Glenn Ammons, Paul Bradley, Bill Donaldson, Elton Glaser, Ben Teitelbaum, Todd Turnidge and Victor Zandy are a few, but there are more than I can name. Two in particular, Chris Lukas and David Melski, have been with me since my first days in graduate school. Our Friday lunches at Mickey's will undoubtedly be my most fond and lasting memories of Madison. I want to thank Chris and his wife, Erika, for providing Marci and me with countless nights of old-married-couple entertainment. Of the aforementioned, Craig and his wife Julie, Milo and his wife Denise, and Adam Butts and his fiancee Sue, have also been good friends to Marci and me. I will miss our cabin getaway weekends and our trips to the APT. Craig and Adam have also accompanied me on multiple snowboarding trips and have never laughed at me in my presence. Finally, I want to thank Dan Sorin, my fellow departmental sports fanatic, for allowing me to make merciless fun of the Cavs in exchange for his doing the same to the Phillies.

Finally, want to thank all those people with whom I have had less than regular interaction, but who supported me and contributed greatly to my academic experience nonetheless: the computer science faculty, the administrative staff which has dealt so pleasantly so many times with my disregard for deadlines and my propensity for losing materials, and the incredibly competent lab staff which has dealt with my ignorance of system administration even more frequently. I also want to thank the Condor team for their tool, without which the experimental portion of this work would have taken at least ten times as long.

My graduate work has been financially supported by a Wisconsin Alumni Research Foundation (WARF) fellowship, an IBM graduate fellowship and an Intel graduate fellowship, National Science Foundation grants MIP-9505853 and CCR-9900584, U.S. Army Intelligence Center and Fort Huachuca contract DABT63-95-C-0127, and by equipment donations from Intel and Sun Microsystems.

## **Table of Contents**

| Abstract i                                                             |

|------------------------------------------------------------------------|

| Acknowledgements                                                       |

| Table of Contents                                                      |

| List of Figures xiv                                                    |

| List of Tables                                                         |

| Chapter 1 Introduction                                                 |

| 1.1 The Need for Implicit Instruction Level Parallelism (ILP)          |

| 1.2 Obstacles to Instruction Level Parallelism                         |

| 1.2.1 The Incumbent: The Dynamically-Scheduled Superscalar Model5      |

| 1.2.2 Limitations of the Superscalar Model                             |

| 1.2.3 Value Analytical Predictors and Problem Instructions             |

| 1.3 Pre-Execution                                                      |

| 1.3.1 Example                                                          |

| 1.3.2 Aspects of Pre-Execution                                         |

| 1.3.3 A Definition of Pre-Execution                                    |

| 1.3.4 Implementation: Speculative Data-Driven Multithreading (DDMT) 20 |

| 1.4 Dissertation Contributions and Outline                             |

| viii                                                               |

|--------------------------------------------------------------------|

| Chapter 2 Pre-Execution via Speculative Data Driven Multithreading |

| 2.1 DDMT Primer                                                    |

| 2.1.1 Terminology                                                  |

| 2.1.2 DDMT Microarchitecture Overview                              |

| 2.1.3 The Life of a DDT                                            |

| 2.1.4 Pre-Execution Reuse via Register Integration                 |

| 2.2 Control Flow in DDMT                                           |

| 2.2.1 Implicit Data-Driven Sequencing                              |

| 2.2.2 Simulating Conditional Control in DDMT                       |

| 2.2.2.1 Implicit Conditional Control                               |

| 2.2.2.2 Greedy Conditional Control                                 |

| 2.2.3 Simulating Loop Control in DDTs                              |

| 2.2.3.1 Overlapped Full Unrolling                                  |

| 2.2.3.2 Unoverlapped Full Unrolling                                |

| 2.2.3.3 Induction Unrolling                                        |

| 2.2.3.4 Alternative: Trigger Chaining                              |

| 2.3 DDT Dataflow Structure                                         |

| 2.3.1 Stores and Memory Communication in DDTs                      |

| 2.4 Chapter Summary                                                |

| Chapter 3 DDT Selection                                            |

| 3.1 Algorithm Overview                                             |

| 3.2 Phase I: Selecting Problem Instructions                        |

| 3.2.1 Metric: Problem Ratio                                        |

| 3.2.2 Metric: Problem Contribution                                 |

| 3.2.3 Metric: Problem Penalty (Desired Latency Tolerance)          |

| 3.3 Phase II: Selecting Single-Problem-Instance DDTs               |

|           | ix                                                             |

|-----------|----------------------------------------------------------------|

| 3.3.1     | Building the Raw Statistical Database: the Time-Consuming Part |

| 3.3.2     | Algorithm Structure and Hard Termination Conditions            |

| 3.3.3     | Metric: Estimating Execution Times using SCDH                  |

| 3.3.4     | Metric: Aggregate Latency Tolerance                            |

| 3.3.5     | Metric: Aggregate Overhead                                     |

| 3.3.6     | Ultimate Metric: Aggregate Advantage                           |

| 3.3.7     | Working Example                                                |

| 3.3.8     | Another Metric: Integrability                                  |

| 3.3.9     | Unrolling and Single-PDI DDTs                                  |

| 3.4 Pha   | se III: Multiple-PDI DDTs                                      |

| 3.4.1     | Alternatives to Merging and Their Limitations                  |

| 3.4.2     | Merging Algorithm                                              |

| 3.4.3     | Working Example                                                |

| 3.4.4     | Multiple-PDI DDTs and Unrolling 101                            |

| 3.5 Imp   | plementing the Algorithm in the Real World                     |

| 3.5.1     | Static, Off-line Implementation                                |

| 3.5.2     | Dedicated Hardware Implementation                              |

| 3.5.3     | Co-Designed Virtual Machine Implementation                     |

| 3.6 Cha   | apter Summary                                                  |

| Chapter 4 | <b>DDMT Microarchitecture</b>                                  |

| 4.1 Uno   | derlying Processor and DDMT112                                 |

| 4.1.1     | The Role of a Centralized Underlying Organization              |

| 4.1.2     | DDMT Modifications                                             |

| 4.2 Fro   | nt End Aspects                                                 |

| 4.2.1     | Pipeline Organization                                          |

| 4.2.2     | DDTC                                                           |

|                          | Х                                               |

|--------------------------|-------------------------------------------------|

| 4.2.3 Trigger Table      |                                                 |

| 4.2.4 Context-Man        | ager and Injection Scheduler 122                |

| 4.2.5 Injection Poli     | cy 123                                          |

| 4.3 Execution Core As    | pects                                           |

| 4.3.1 Stores and Me      | emory Communication                             |

| 4.3.1.1 DDT-E            | xternal Communication                           |

| 4.3.1.2 DDT-In           | ternal Communication                            |

| 4.3.2 Allocation an      | d Freeing of Execution Resources                |

| 4.3.3 Exceptions ar      | d Other Disastrous Events                       |

| 4.4 Register Integration | n                                               |

| 4.4.1 Squash Reuse       | via Register Integration                        |

| 4.4.2 Uses of Regis      | ter Integration in DDMT 140                     |

| 4.4.3 A Physical Re      | egister Discipline for Integration              |

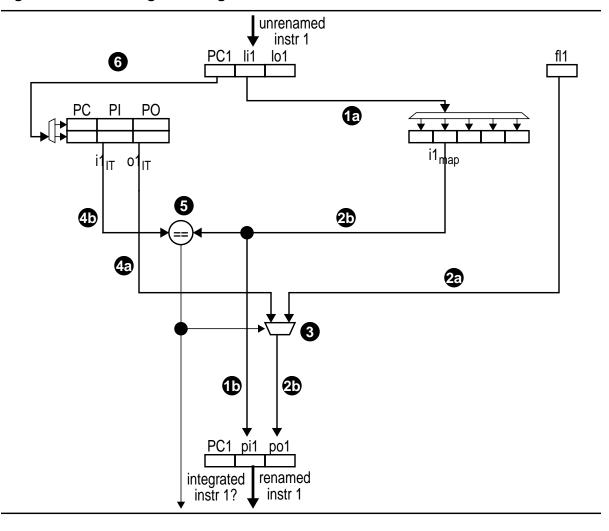

| 4.4.4 Integration C      | rcuit                                           |

| 4.4.4.1 Scalar C         | Sircuit                                         |

| 4.4.4.2 Supersc          | alar Circuit                                    |

| 4.4.5 A Shortcomir       | g of the Current Formulation and an Alternative |

| 4.4.6 Register Integ     | gration and Correctness                         |

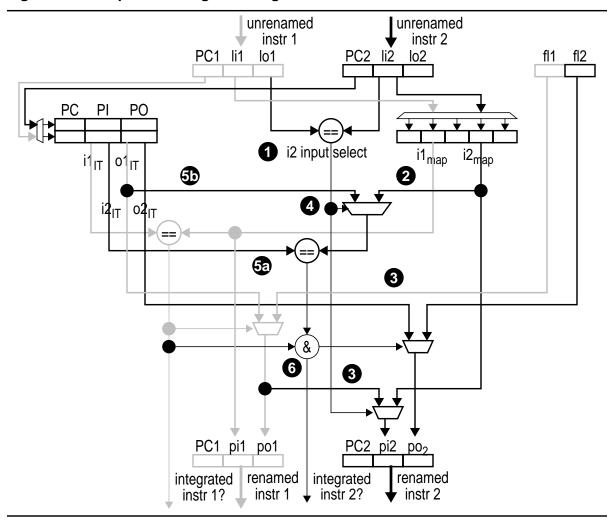

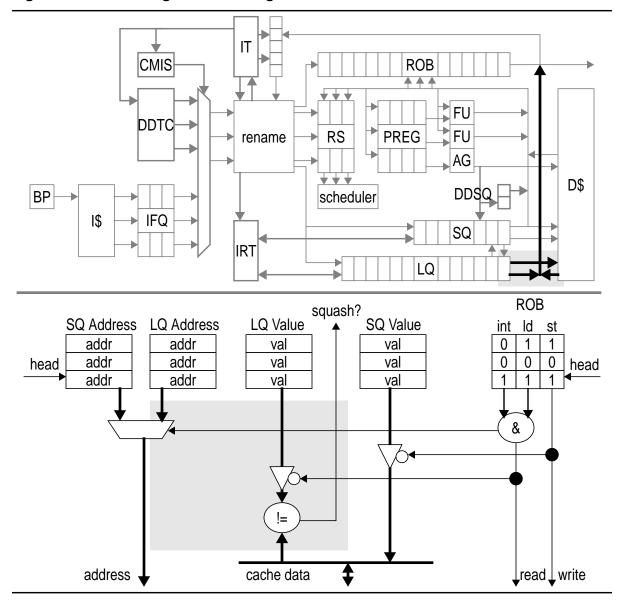

| 4.4.6.1 Detectir         | g Mis-Integrations 158                          |

| 4.4.6.2 Avoidin          | g Mis-Integrations 161                          |

| 4.4.6.3 Memory           | Model Issues                                    |

| 4.5 Chapter Summary .    |                                                 |

| Chapter 5 Experimental   | Evaluation                                      |

| 5.1 Experimental Fram    | ework and Methodology 166                       |

| 5.1.1 DDMT Performance   | mance Simulator                                 |

| 5.1.2 DDT Constru        | ction Tool-Chain 172                            |

| 5.1.3 Benchmark P        | rograms                                         |

| xi                                                                   |

|----------------------------------------------------------------------|

| 5.1.4 Sampling                                                       |

| 5.2 Analysis of a Single DDMT Design Point                           |

| 5.2.1 Establishing a Baseline                                        |

| 5.2.2 Absolute Upper Bound on DDMT Performance                       |

| 5.2.3 Performance Potential of Perfecting Problem Instructions       |

| 5.2.4 DDT Characterization                                           |

| 5.2.5 DDMT Performance                                               |

| 5.2.5.1 Measuring Pre-Execution Activity and Pre-Execution Reuse 214 |

| 5.2.5.2 PDI Coverage                                                 |

| 5.2.5.3 Impact of Pre-Execution Reuse                                |

| 5.2.5.4 Attempting to Account for Overhead                           |

| 5.2.6 Evaluating the Implementation "Stack"                          |

| 5.3 Sensitivity Analysis                                             |

| 5.3.1 Sensitivity to DDMT Specific Microarchitecture Configuration   |

| 5.3.1.1 Integration Associativity                                    |

| 5.3.1.2 Load Integration Suppression                                 |

| 5.3.1.3 Trigger Chaining                                             |

| 5.3.1.4 A Summary of Other Results                                   |

| 5.3.2 Sensitivity to DDT Selection Parameters                        |

| 5.3.2.1 Problem Instruction Definition                               |

| 5.3.2.2 DDT Size, Slicing Scope and Unrolling Degree                 |

| 5.3.2.3 Latency Tolerance Acceptability Factor (LCAF)                |

| 5.3.2.4 Summary of Other Results                                     |

| 5.3.3 Sensitivity to Setup/Runtime Relationship                      |

| 5.3.4 Sensitivity to Underlying Processor Configuration              |

| 5.3.4.1 Processor Width                                              |

| 5.3.4.2 Cache and Branch Predictor Table Size                        |

| 5.3.4.3 L2 Cache, Memory and Branch Resolution Latencies             |

|                | xii                                                       |

|----------------|-----------------------------------------------------------|

| 5.4 Chapter    | Summary                                                   |

| Chapter 6 Rela | ted Work                                                  |

| 6.1 Pre-Exe    | cution: My Retrospective                                  |

| 6.1.1 De       | pendence-Based Prefetching for Linked Data Structures     |

| 6.1.2 De       | pendence-Based Pre-Computation for Virtual Function Calls |

| 6.1.3 A        | Speculative Dataflow Processor                            |

| 6.1.4 DI       | DMT                                                       |

| 6.2 Earlier V  | Work                                                      |

| 6.2.1 Da       | taflow Architectures                                      |

| 6.2.2 De       | coupled Access/Execute Architecture                       |

| 6.2.3 Ru       | nahead Execution                                          |

| 6.2.4 Sp       | eculative (Control-Driven) Multithreading                 |

| 6.2.5 Mu       | ulti-Path Execution                                       |

| 6.2.6 Pre      | e-Execution                                               |

| 6.2.7 Ins      | struction Reuse and Unified Renaming                      |

| 6.3 Contemp    | poraneous Work                                            |

| 6.3.1 Da       | ta-Threaded Microarchitecture                             |

| 6.3.2 Sli      | pstream Processors                                        |

| 6.4 Subsequ    | ent Work                                                  |

| 6.4.1 De       | pendence Graph Pre-Computation and ILP Balancing          |

| 6.4.2 Pre      | e-execution of Speculative Slices                         |

| 6.4.3 Sp       | eculative Pre-Computation                                 |

| 6.4.4 So       | ftware-Controlled Pre-Execution                           |

| 6.4.5 Sli      | ce Processors                                             |

| 6.5 Chapter    | Summary                                                   |

|              | xiii                                                  |

|--------------|-------------------------------------------------------|

| Chapter 7 (  | Conclusion                                            |

| 7.1 Sum      | mary of Concepts, Mechanisms and Frameworks           |

| 7.1.1        | Pre-Execution                                         |

| 7.1.2        | Speculative Data Driven Multithreading                |

| 7.1.3        | Automated DDT Selection                               |

| 7.2 Sum      | mary of Results                                       |

| 7.2.1        | Performance Potential of DDMT                         |

| 7.2.2        | Sensitivity of DDMT                                   |

| 7.2.3        | Limitations of DDMT                                   |

| 7.3 Futu     | re Work                                               |

| 7.3.1        | System-Friendly Implementation and Interface for DDMT |

| 7.3.2        | Practical Register Integration                        |

| 7.3.3        | Branch Predictor Interface for Pre-Executed Branches  |

| 7.3.4        | Unoverlapped Full Unrolling for DDTs                  |

| 7.3.5        | Optimizations for DDTs                                |

| References . |                                                       |

# List of Figures

| Figure 1.1:  | Abstract dynamically-scheduled superscalar processor                   | 6   |

|--------------|------------------------------------------------------------------------|-----|

| Figure 1.2:  | Abstract example of pre-execution                                      | 14  |

| Figure 2.1:  | DDMT terminology                                                       | 27  |

| Figure 2.2:  | DDMT microarchitecture                                                 | 30  |

| Figure 2.3:  | Events in the life of a DDT                                            | 32  |

| Figure 2.4:  | Pre-execution reuse using register integration                         | 37  |

| Figure 2.5:  | Problem with use of opcode matching in register integration            | 39  |

| Figure 2.6:  | Implicit conditional control in a DDT                                  | 44  |

| Figure 2.7:  | Greedy conditional control in a DDT                                    | 46  |

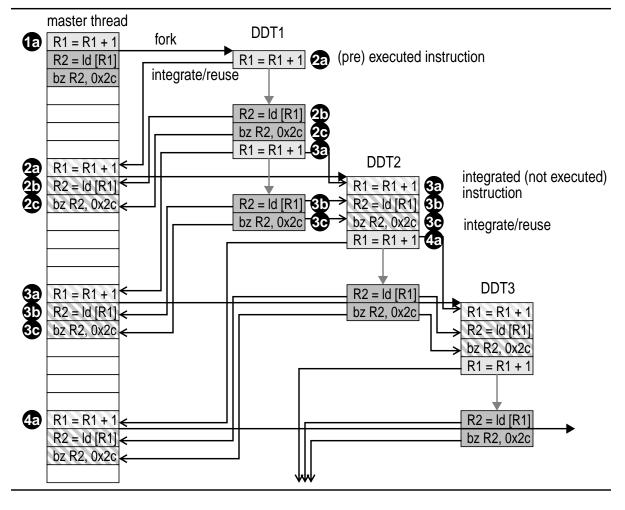

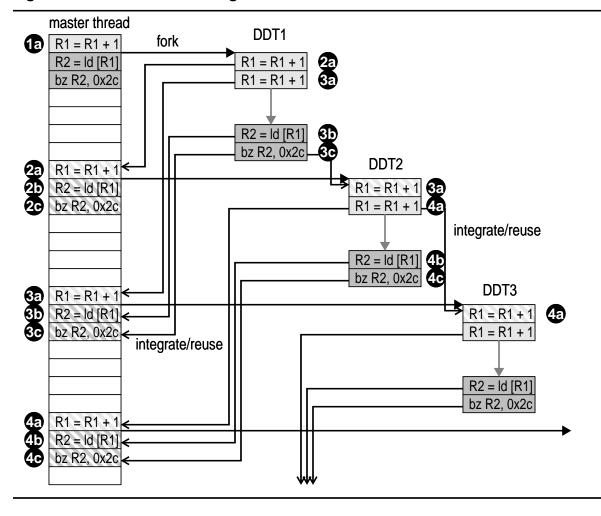

| Figure 2.8:  | Overlapped full unrolling                                              | 49  |

| Figure 2.9:  | Two examples of unoverlapped full unrolling                            | 51  |

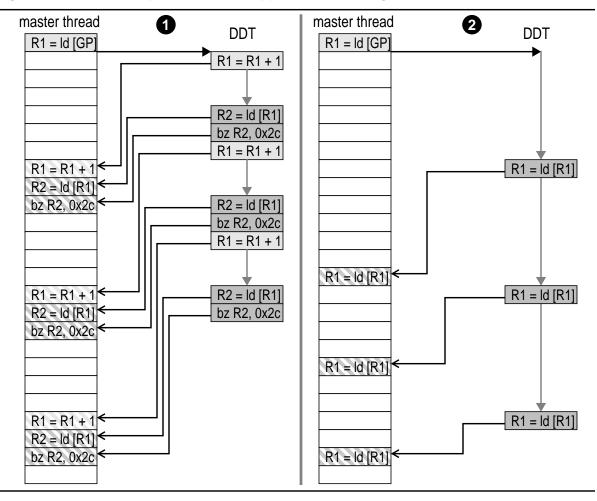

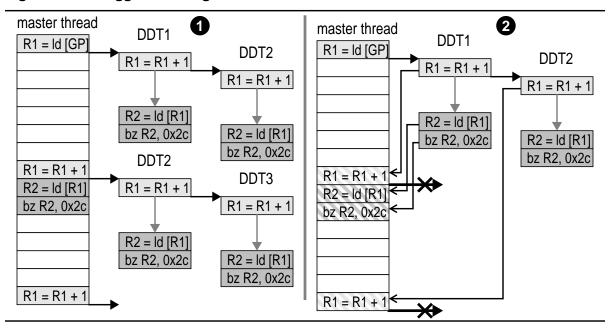

| Figure 2.10: | Induction unrolling                                                    | 53  |

| Figure 2.10: | Induction unrolling                                                    | 53  |

| Figure 2.11: | Trigger chaining                                                       | 55  |

| Figure 2.12: | DDT-internal and DDT-external memory communication                     | 58  |

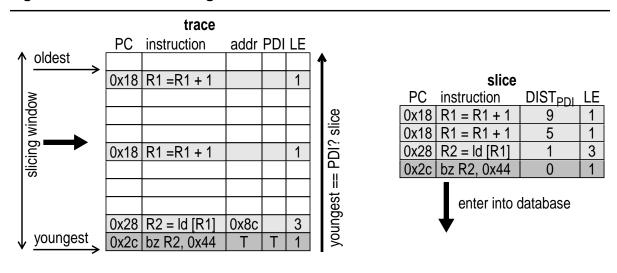

| Figure 3.1:  | Slicer and slicing window                                              | 73  |

| Figure 3.2:  | Statistical backward slice database                                    | 74  |

| Figure 3.3:  | Sample SCDHdiff calculation.                                           | 81  |

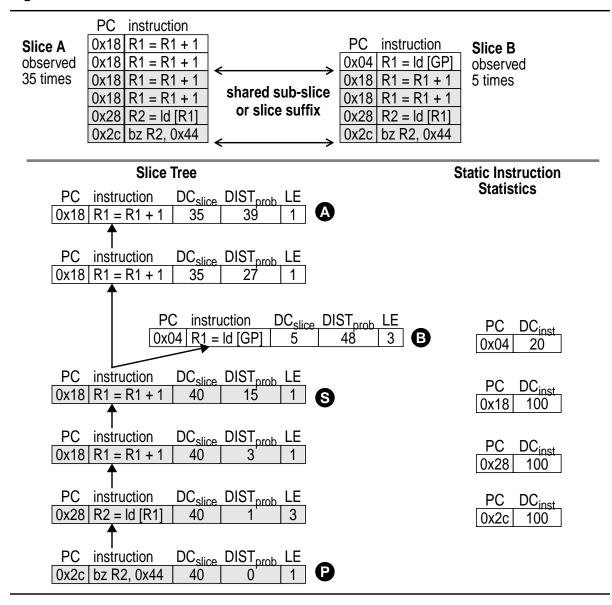

| Figure 3.4:  | Working example of single-PDI DDT selection algorithm                  | 87  |

| Figure 3.5:  | A DDT that is difficult to integrate                                   | 91  |

| Figure 3.6:  | Integration disambiguation mechanism for difficult-to-integrate DDTs . | 92  |

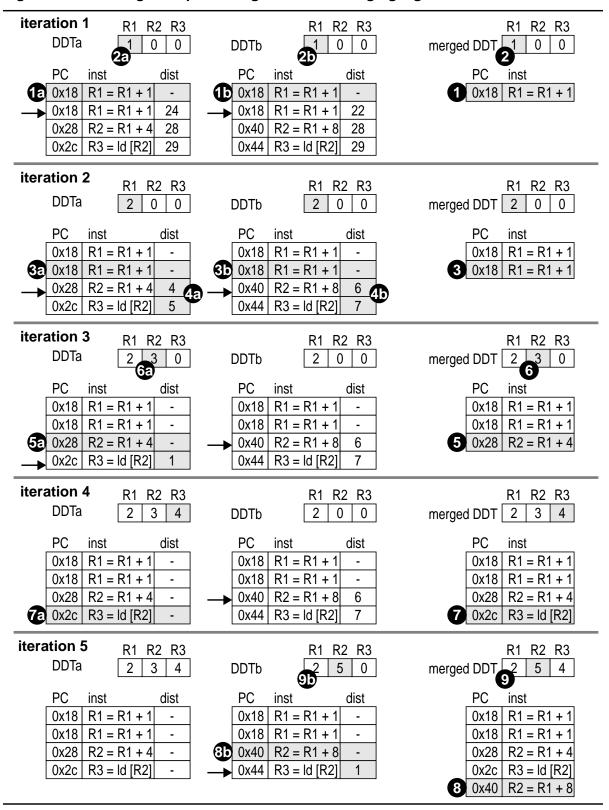

| Figure 3.7:  | Working example of single-PDI DDT merging algorithm                    | 99  |

| Figure 3.8:  | Merging unrolled DDTs                                                  | 102 |

| Figure 4.1:  | DDMT microarchitecture                                                 | 115 |

|              |                                                                        |     |

|              | XV                                                                        |

|--------------|---------------------------------------------------------------------------|

| Figure 4.2:  | DDMT front end                                                            |

| Figure 4.3:  | DDSQ implementation                                                       |

| Figure 4.4:  | Register integration                                                      |

| Figure 4.5:  | Register integration squash reuse scenario                                |

| Figure 4.6:  | Physical register disciplines: conventional and with squash reuse143      |

| Figure 4.7:  | Physical register discipline for pre-execution reuse                      |

| Figure 4.8:  | Physical register discipline with cascaded invalidation                   |

| Figure 4.9:  | Scalar register integration circuit                                       |

| Figure 4.10: | Superscalar register integration circuit                                  |

| Figure 4.11: | Mis-integration scenarios                                                 |

| Figure 4.12: | Detecting load mis-integrations via re-execution                          |

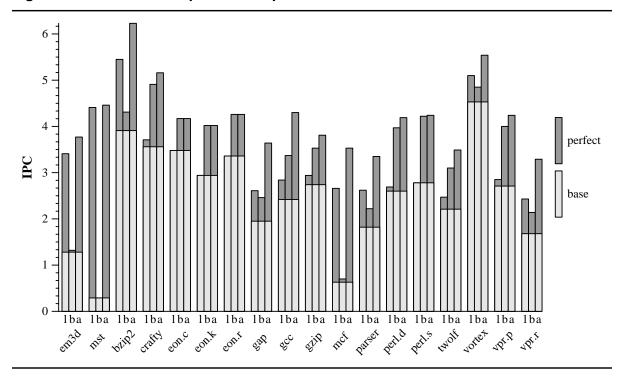

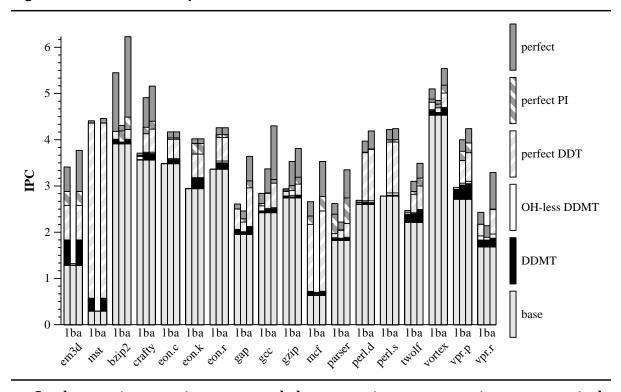

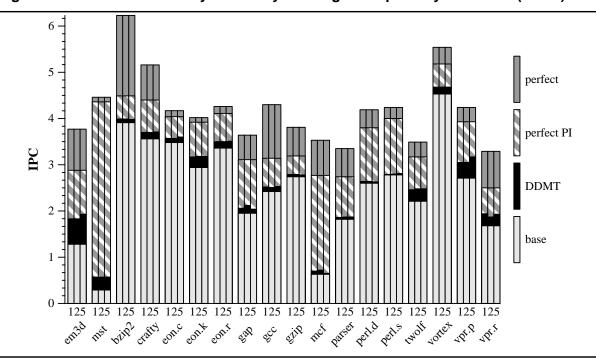

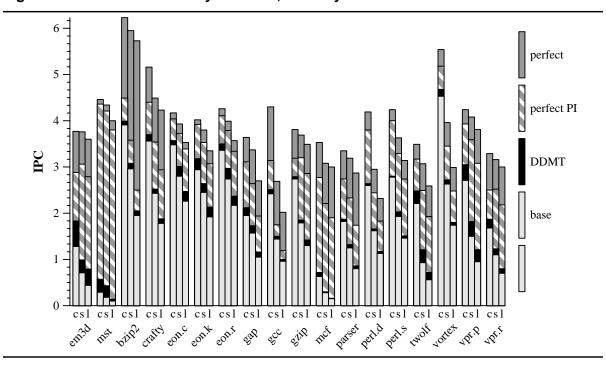

| Figure 5.1:  | Performance potential of perfect load and branch resolution latencies 190 |

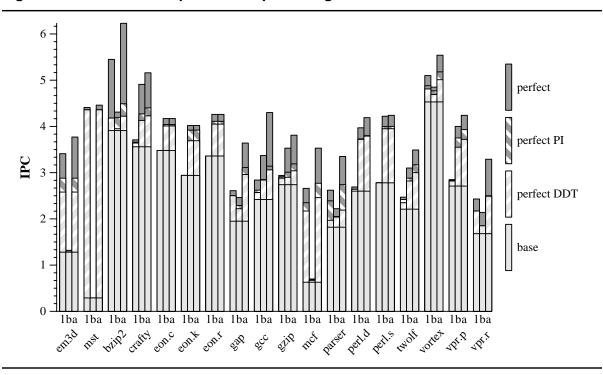

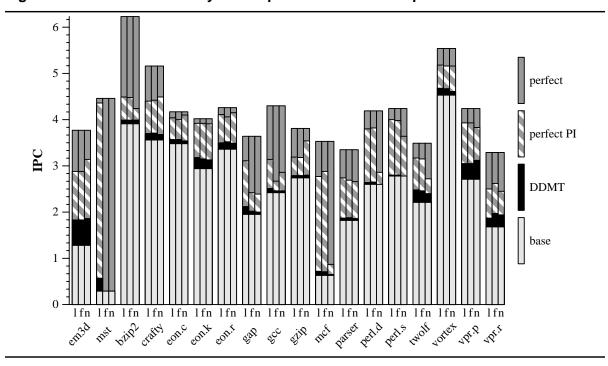

| Figure 5.2:  | Performance potential of perfecting PIs                                   |

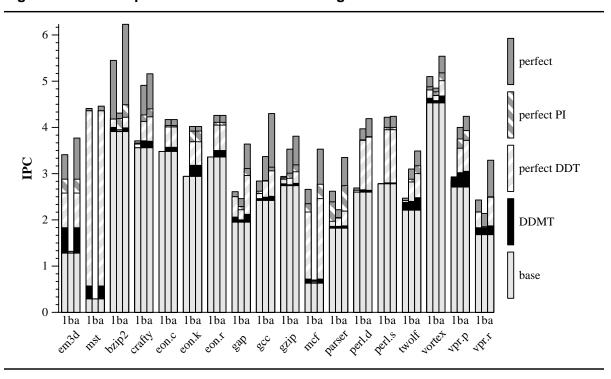

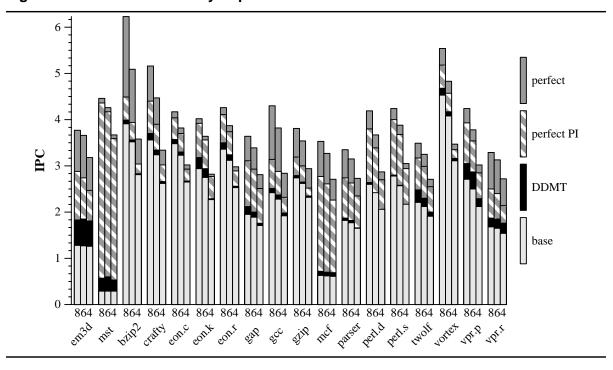

| Figure 5.3:  | Performance potential of perfecting PIs for which DDTs were found 200     |

| Figure 5.4:  | DDMT performance on central configuration                                 |

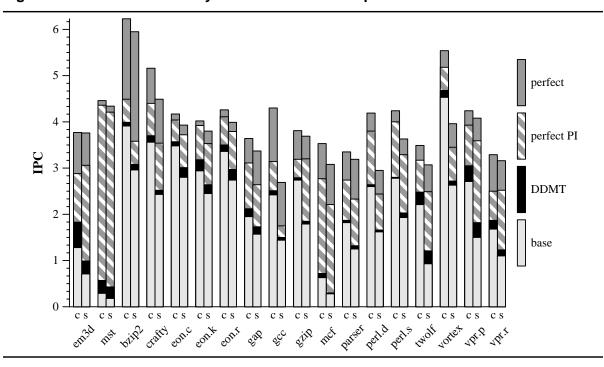

| Figure 5.5:  | Performance impact of pre-execution reuse                                 |

| Figure 5.6:  | Performance potential of DDMT without overhead                            |

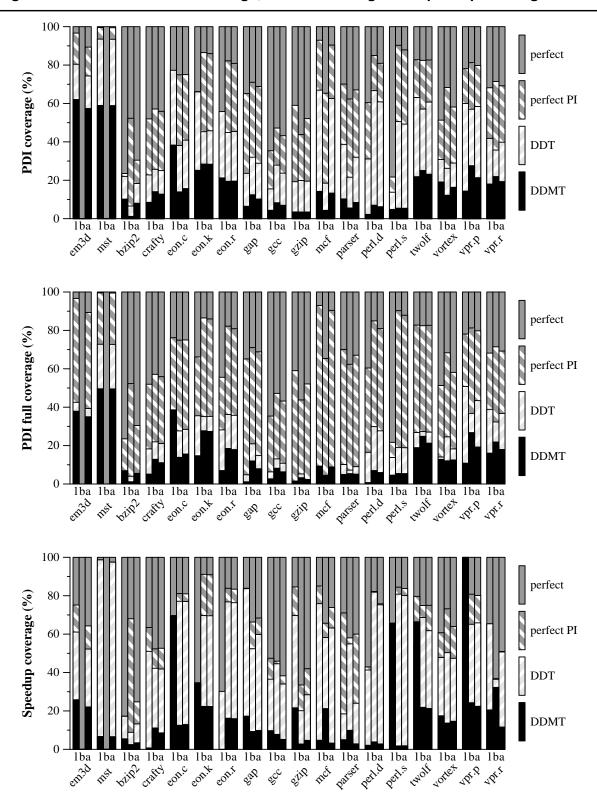

| Figure 5.7:  | Cumulative PDI coverage, PDI full coverage and speedup coverage 234       |

| Figure 5.8:  | DDMT sensitivity to PI definition                                         |

| Figure 5.9:  | DDMT sensitivity to DDT size, selection scope and unrolling degree 258    |

| Figure 5.10: | DDMT sensitivity to latency coverage acceptability threshold (LCAF) 263   |

| Figure 5.11: | DDMT sensitivity to setup/runtime relationship                            |

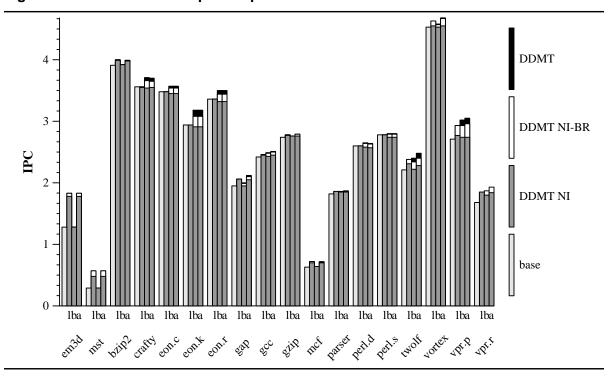

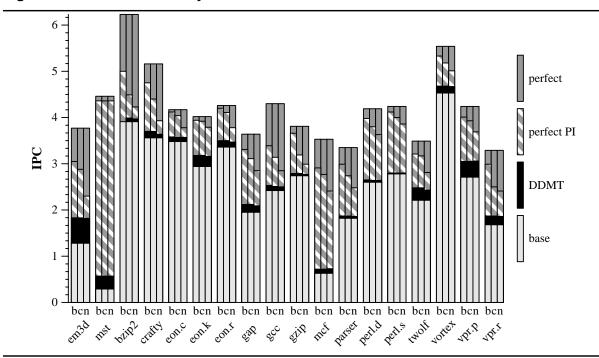

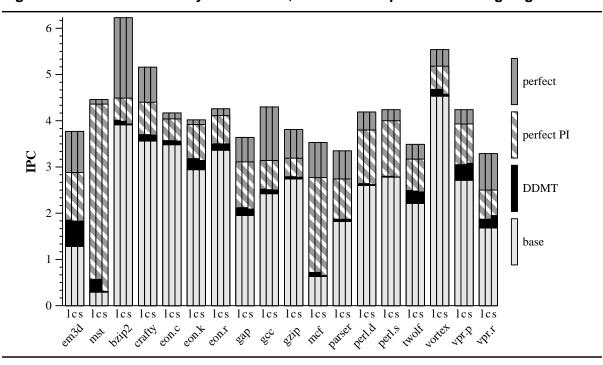

| Figure 5.12: | DDMT sensitivity to processor width                                       |

| Figure 5.13: | DDMT sensitivity to cache and branch predictor size                       |

| Figure 5.14: | DDMT sensitivity to cache, memory and branch resolution latencies 291     |

## **List of Tables**

| Table 5.1:  | Performance simulator configuration: branch predictor and caches 10      | 58 |

|-------------|--------------------------------------------------------------------------|----|

| Table 5.2:  | Performance simulator configuration: pipeline and scheduler 10           | 69 |

| Table 5.3:  | Performance simulator configuration: DDMT and register integration1      | 70 |

| Table 5.4:  | Ddt-select parameters                                                    | 73 |

| Table 5.5:  | Functional benchmark characterization1                                   | 76 |

| Table 5.6:  | Performance of register integration-based squash reuse                   | 84 |

| Table 5.7:  | Performance potential of perfect load and branch resolution latencies 19 | 91 |

| Table 5.8:  | Performance potential of perfecting load PIs                             | 95 |

| Table 5.9:  | Performance potential of perfecting branch PIs                           | 96 |

| Table 5.10: | Performance potential of perfecting load and branch PIs                  | 97 |

| Table 5.11: | Characterizing load DDTs                                                 | 01 |

| Table 5.12: | Characterizing branch DDTs                                               | 02 |

| Table 5.13: | Characterizing "combination" load and branch DDTs                        | 03 |

| Table 5.14: | Additional characterization of "combination" load and branch DDTs 20     | 06 |

| Table 5.15: | DDMT performance for "combination" load and branch DDTs 20               | 09 |

| Table 5.16: | DDMT performance load DDTs and branch DDTs separately                    | 10 |

| Table 5.17: | Pre-execution and pre-execution reuse diagnostics                        | 16 |

| Table 5.18: | Load pre-execution and pre-execution reuse diagnostics                   | 19 |

| Table 5.19: | Branch pre-execution and pre-execution reuse diagnostics                 | 22 |

| Table 5.20: | Load and branch pre-execution and pre-execution reuse diagnostics22      | 23 |

| Table 5.21: | Performance impact of pre-execution reuse                                | 27 |

| Table 5.22: | Performance potential of DDMT without overhead                           | 32 |

| Table 5.23: | Performance impact of IT associativity                                   | 39 |

| Table 5.24: | Performance impact of load integration suppression predictor24           | 43 |

|             | xvii                                                                         |

|-------------|------------------------------------------------------------------------------|

| Table 5.25: | Performance impact of trigger chaining                                       |

| Table 5.26: | Comparative evaluation of PI definitions                                     |

| Table 5.27: | Characterizing DDTs selected using different PI definitions                  |

| Table 5.28: | DDMT performance sensitivity to different PI definitions                     |

| Table 5.29: | Evaluating DDTs of different sizes, slicing scopes and unrolling degrees 260 |

| Table 5.30: | DDMT performance sensitivity to DDTs of different sizes                      |

| Table 5.31: | Evaluating DDTs chosen using different LCAF values                           |

| Table 5.32: | DDMT sensitivity to different LCAF values                                    |

| Table 5.33: | PI definition stability under different setup/runtime scenarios              |

| Table 5.34: | DDMT sensitivity to setup/runtime scenarios                                  |

| Table 5.35: | DDMT on an 8-wide processor                                                  |

| Table 5.36: | DDMT on a 6-wide processor                                                   |

| Table 5.37: | DDMT on a 4-wide processor                                                   |

| Table 5.38: | DDMT on a processor with smaller caches and branch predictor tables 286      |

| Table 5.39: | DDMT on a processor with smaller caches and longer memory latencies 292      |

|             |                                                                              |

## **Chapter 1**

### Introduction

This dissertation introduces *pre-execution*, a new paradigm for improving the performance of sequential programs. It also introduces *speculative data-driven multithreading (DDMT)*, an implementation of pre-execution.

Performance degradation in sequential programs is primarily due to *value latency*, the late availability of a value that directly or indirectly causes program execution to stall. In the natural course of execution, all needed values are ultimately computed. However, certain important values like branch outcomes and the addresses of soon-to-be referenced but uncached data blocks are often needed earlier than execution can supply them. Techniques for providing these values quickly by predicting them from previous values are extremely useful [7, 11, 13, 17, 16, 27, 28, 33, 47, 51, 57, 61, 62, 64, 77]. However, their accuracies and coverages are only about 95% and are unlikely to get much closer to 100% [34, 47]. The approximately 5% of dynamic branches and loads whose outcomes and addresses defy prediction are called *performance degrading instances (PDIs)*. PDIs account

for up to 50% of execution times of many sequential programs [104, 106]. The few static instructions that are responsible for the majority of PDIs [1] are called *problem instructions (PIs)* [106].

Pre-execution is a way of using actual program execution to obtain PDI values in a timely manner. Pre-execution is motivated by the observation that only a fraction of the program is required to generate any particular value. If this fraction is small enough and if enough execution bandwidth is available, then the latency of computing this value can be effectively hidden from the complete program by executing—actually pre-executing—a parallel copy of this computation. Because it executes fewer instructions, the copy initiates the high latency component of the computation earlier than the complete program is able to. Because the parallel copy and the main program are decoupled from one another, long latencies in one do not induce stalls in the other. A pre-executing copy acts as a "performance troubleshooter," absorbing latencies so that they do not stall the complete program whose performance is externally visible.

In addition to introducing and defining pre-execution, this dissertation also describes an implementation of pre-execution called *speculative data-driven multithreading (DDMT)*. DDMT implements pre-execution as a set of small extensions to a dynamically scheduled superscalar processor.

This dissertation is organized into seven chapters. The goal of this chapter is to motivate, introduce, and define both pre-execution and DDMT. We begin with a brief argument for the need for the kind of parallelism pre-execution enhances: instruction-level parallelism (ILP). We continue with a description of the incumbent model for extracting ILP, the superscalar model, and its limitations. We then introduce pre-execution as a technique for overcoming the limitations of the superscalar model and its satellite technologies in fundamental ways. Finally, we provide a high level overview of DDMT, our proposed implementation of pre-execution, pointing out its novel aspects. The last section of this chapter summarizes the contributions of the dissertation and outlines the remaining chapters.

## 1.1 The Need for Implicit Instruction Level Parallelism (ILP)

The central role played by computers in every aspect of society has been driven by the rapidly increasing performance of general purpose microprocessors. Successive order-of-magnitude increases in processor performance—which recently have occurred every six years or so—have enabled leaps in software functionality and made the microprocessor into a ubiquitous commodity. The charter of computer engineers is to ensure that performance continues to grow at an adequate pace.

Microprocessor performance is a product of two factors: clock frequency and parallelism—the execution of multiple useful operations per clock cycle. Semiconductor technology—the continued miniaturization of CMOS devices—has driven both. Device scaling produces faster individual transistors and more of them, enabling higher clock frequencies and providing computer architects with more raw materials with which to extract parallelism. Continued growth necessitates an increased contribution from parallelism. Even at today's frequencies, processors spend a significant fraction of their time waiting for data from memory. Increasing processor frequency will increase performance, but at a sublinear and shrinking rate of return as the memory waiting time is not reduced. Parallelism is needed both to make up for this decreased efficiency, by providing useful work that may be overlapped with memory latency, and to further boost the performance in its own right.

Parallelism can take many forms. An important form is the *instruction level parallelism (ILP)* available in varying degrees in every sequential—not explicitly parallel—piece of code. Enhanced ILP complements other granularities of parallelism and is the primary way to improve the parallelism of sequential code. It is the function of the microprocessor—potentially with help from software—to discover and exploit ILP, while giving the external appearance of sequential execution.

Parallelism and performance are not the only goals. Tightening constraints on power consumption, area, design and verification complexity, and reliability have shifted the research emphasis from ILP techniques that provide diminishing returns or use special purpose hardware, to innovative solutions that enhance ILP in fundamentally new ways while leveraging existing components. It is my belief that pre-execution is such a technique.

#### **1.2 Obstacles to Instruction Level Parallelism**

Limit studies of sequential programs have shown that, theoretically, most have sufficient inherent concurrency to sustain the parallel execution of over 20 instructions per cycle, even accounting for 100 cycle execution latencies that result from the use of realistic memory systems [90, 99]. However, for almost all of these programs, most modern microprocessors cannot sustain useful levels of parallelism that approach even one tenth of that amount.

This discrepancy is ultimately due to the von Neumann sequential programming model. The structure of computations in a program imposes a partial order on its instructions called the *data-flow order*. It is this partial order that defines maximum concurrency. The sequential programming model imposes a total order, called the *control-flow order*; on top of this partial order. The total-order of control-flow defines program state unambiguously at every instruction boundary, giving the programmer an interface that supports repeatable executions and allows him/her to reason about program behavior. Moreover, total-order (controlflow) is often the only way to specify the partial order, which for non-functional languages (most languages) is statically ambiguous. While the total order makes for a convenient programming interface, its implementation restricts concurrency.

#### 1.2.1 The Incumbent: The Dynamically-Scheduled Superscalar Model

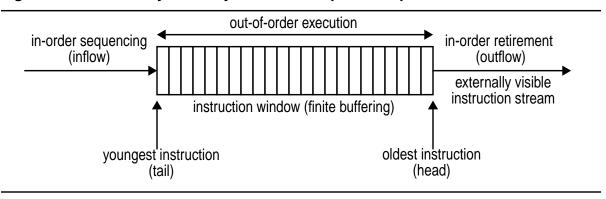

Dynamic scheduling or out-of-order execution is the standard technique for maximizing concurrency while implementing a sequential interface. An abstract dynamically scheduled superscalar processor is shown in Figure 1.1. The processor slides a fixed-size window over a program's dynamic instruction stream. Instructions are sequenced (flow into the window) and retired (flow out of the window) in program order. In-order retirement provides the external appearance

Figure 1.1 Abstract dynamically-scheduled superscalar processor.

of sequential execution. In-order sequencing establishes the correct data dependences between instructions required to implement the meaning of the program. Result buffering within the window allows instructions to execute out of program order. Precise knowledge of data-dependence information facilitates the exploitation of concurrency. Instructions that are known to be data-independent may execute in parallel. The earliest possible execution time of any instruction may be determined precisely by simply monitoring the availability status of its input dependence values. This same buffering even allows for *renaming*, a form of versioning that removes false dependences that are artifacts of the architectural name spaces, exposing even more parallelism.

#### **1.2.2 Limitations of the Superscalar Model**

Processor performance is measured by retirement (outflow) throughput. A processor can achieve peak performance if it can execute *useful instructions*—i.e., instructions that will ultimately be retired—at peak bandwidth every cycle. Performance degrades when not enough ready-to-execute useful instructions are

available in a given cycle. The number of ready-to-execute useful instructions can drop to sub-peak levels due to interruptions in the inflow of useful instructions.

There are two kinds of inflow interruptions and both are due to the sequential programming model. *Direct interruptions* are caused by events that occur at the sequencing end of the processor. The primary causes of direct interruptions are *instruction cache misses* and *branch mis-predictions*. Instruction cache misses stall inflow completely, while branch mis-predictions stall the inflow of useful instructions. Branch mis-predictions are an artifact of the sequential pipeline which implies that instructions be sequenced *speculatively* (i.e., before all prior branches have executed and determined the actual dynamic path). The sequential data-dependence model means that any instruction sequenced after a mispredicted branch is useless.

Indirect interruptions are caused by events that occur at the retirement end of the processor. Indirect interruptions directly stall outflow. The finite size of the window propagates the outflow stall backwards via back-pressure to create an inflow stall. The primary cause of indirect interruptions are instructions with long execution latencies, most commonly *loads that miss in the data cache*. In this dissertation, we deal only with branch mis-predictions and data cache misses. We ignore instruction cache misses as they are both infrequent in the programs we study and not easily handled by our technique.

In-order sequencing poses another difficult problem. Ideally, execution should take place in global data-driven order. However, execution order is constrained by sequencing order, and sequencing order and global data-driven order rarely match. Since both sequencing and execution can only be performed with certain bandwidth, the result is a window-restricted execution schedule which under-utilizes execution bandwidth. In other words, in-order sequencing is not conducive to high processor utilization. It delays some instructions that—for data-independence reasons—could have been executed right away, while inserting others into the window that—for data-dependence reasons—will not be executed for a long time.

There are two apparent solutions. One is to create a machine with a very large window. Such a machine would smooth temporary inflow stalls and dampen outflow stalls by removing back-pressure. There are several problems with this approach. First, superscalar execution requires the implementation of several highly-parallel search algorithms whose purpose is to find independent instructions to execute every cycle. The complexity and performance of these algorithms degrades when they must examine many instructions in parallel. Second, and more fundamentally, there is no point in filling a large window with useless instructions. Larger windows necessitate speculating across more unexecuted branches in order for sequencing to proceed. The sequential nature of control flow speculation creates a geometrically decreasing probability that the instructions sequenced using accumulated guesses are useful.

With the physical size of a superscalar processor apparently limited, a second approach is to statically schedule instructions in a program to take full advantage of whatever buffering and latency tolerance the window does provide. This approach is useful and extremely important, but static instruction scheduling is limited by dependence analysis and no amount of scheduling can prevent stalls if latencies are sufficiently long.

To summarize, processor performance degrades whenever the number of unexecuted, ready-to-execute useful instructions drops below peak execution bandwidth. Instances of this scenario are due to a combination of five factors. We take the first three as given: (1) the von Neumann in-order retirement constraint, (2) engineering constraints and diminishing control-speculation utility that restrict the size of a practical window, and (3) fundamental limitations on compiler scheduling. We turn our attention to the last two: (4) inflow interruptions due either directly to control mis-speculations or indirectly to long latencies of realistic memory systems, and (5) low execution utilization due to the ordering mismatch between data-driven execution and control-driven (in-order) sequencing.

#### **1.2.3 Value Analytical Predictors and Problem Instructions**

Inflow interruptions are due to value latency. Execution is the primary, golden method for generating values. However, execution cannot generate certain values—branch outcomes and the addresses of needed data blocks that are not in the cache—quickly enough to prevent the need for those values from causing stalls.

Control-speculation and proactive management of the memory hierarchy (prefetching) are popular techniques for hiding the two most common sources of value latency—the pipeline and the memory system. The workhorses of controlspeculation and prefetching are *branch* and *address predictors*, whose fundamental functions are to reduce the latency of branch outcomes and data addresses, providing them faster than conventional execution is able to. Branch and address prediction have been active subjects of research for a long time [7,11, 13, 16, 17, 27, 28, 33, 47, 51, 57, 61, 62, 64, 77]. Both have advanced to the point where values can be correctly predicted (and no performance penalty is incurred) for upwards of 95% of dynamic instances [33, 47]. However, the possibility for taking either technique to a 100% coverage and accuracy limit appears slim [34].

Before we proceed, we should mention that another possibility for tolerating load latency is to use *load value prediction* [39, 52, 53, 76] to generate load values that can be speculatively used in downstream computation. The predicted value—and the speculative computation—is then verified when the actual load completes. We do not consider load value prediction in this dissertation for two reasons. First, load value prediction accuracies are low—60% to 80%—relative to address prediction accuracies. Second, even if perfectly accurate, load value speculation may not improve performance significantly due to long verification latencies.

Providing accurate branch outcomes and prefetch addresses in a timely manner requires a mechanism that is faster than execution, but that can mimic execution results with high accuracy. The basis for such a mechanism lies in the regularity of addresses and branch outcomes produced by programs. Branch and address predictors study streams of addresses and branch outcomes and learn patterns that repeat in those streams. Patterns are associated with the program

contexts in which they occur. When a context repeats, the associated pattern is used to generate a guessed value for a branch or address—usually with high accuracy. We call this approach *value analytical*. The value analytical approach works because programs are repetitive and because common programming idioms—i.e., program structures—produce common and repetitive branch outcome and address patterns. The problem is that some program idioms produce patterns which externally do not appear regular or repetitive (e.g., a branch that tests a data element obtained from external input). Other idioms produce repetitive patterns, but do so over such a large and incompressible context that simply storing this context becomes impractical (e.g., a traversal of a very large pointer-based data structure [11]). Still other idioms produce value streams with small and finite contexts that simply do not repeat, so that learning the requisite patterns on the first pass over the stream does not accelerate the handling of future passes over the stream, as no future passes will be made [11]. These are fundamental problems with value analytical approaches that do not appear surmountable from within.

The instructions that, for program-structural reasons, expose the limitations of value-analytical mechanisms have been called *problem instructions (PIs)* [104, 106]. Informally, a PI is any static instruction whose dynamic instances account for a disproportionate amount of a program's execution time, both on a per-static and a per-dynamic instruction basis. In other words, a problem instruction has many long latency instances. In practice, instructions that have a large fraction of long latency instances are pathologic in some way and, in particular, they are loads and branches whose behavior cannot be reproduced by value-analytical predictors. Problem instructions cause problems for value-analytical predictors and, as a result, for performance.

#### **1.3 Pre-Execution**

The limitations of conventional branch and address prediction lead to the following hypothesis: the values associated with problem instructions can only be obtained reliably via execution. However, this leaves us with a dilemma. On the one hand, we must obtain these values in a way that is faster than execution. On the other, the only reliable tool we have is execution. In essence, we must use execution in a way that is somehow faster and more streamlined than normal execution. The observation that motivates pre-execution is that, while the program is the source of all values, only a small subset of the program is needed to compute any particular value. Provided its computation is a small enough subset of the program and provided resources exist to execute this computation, any value can be made available in a timely fashion to the main program simply by expediting its computation. We call this kind of execution *pre-execution* because it executes pieces of the original program before a control-driven processor would be able to execute them via the conventional route.

This dissertation explores the use of pre-execution in the role of providing timely values for problem branches and loads. We propose to create copies of problem computations—computations of problem loads and branches—and to pre-execute these computations in parallel with, and decoupled from, the main program. The pre-executing copies compute problem instruction values faster than the complete program by virtue of their smaller sizes. Pre-executed computations act as "branch oracles" for the complete program, supplying it with precomputed branch outcomes. In addition, the demand-driven cache management performed by pre-executing computations looks like proactive oracle cache management to the complete program. In essence, pre-executed computations "absorb" value latencies and their associated stalls on behalf of the complete program.

#### 1.3.1 Example

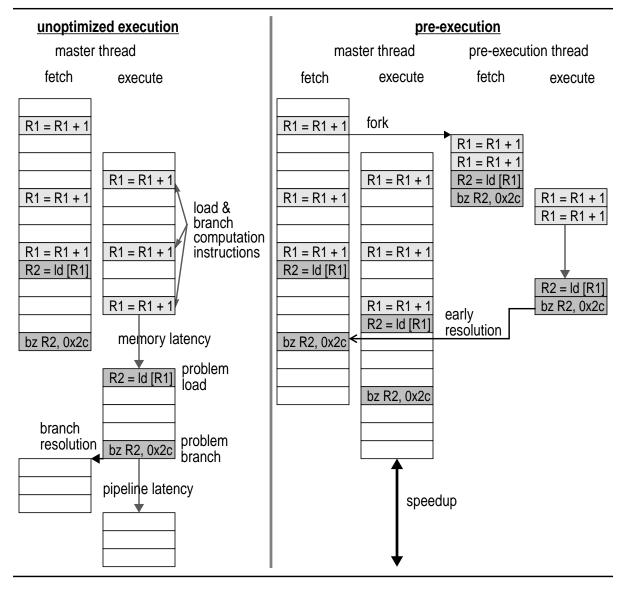

Figure 1.2 shows an abstract example of pre-execution. An unoptimized execution is on the left, showing both fetch and execution schedules. Each box represents a dynamic instruction. Boxes in dark gray are instances of problem instructions (PIs). Boxes in lighter gray are instructions that participate in a PI computation. Empty white boxes are instructions that do not contribute to a PI computation. We will follow this convention in the rest of the dissertation. The abstract pipeline depth is three cycles from fetch to execute. Two sources of delay are shown. Memory latency delays the execution of a problem load that misses in the cache. Branch resolution latency exposes the depth of the pipeline on a mispredicted problem branch. Our convention is to use arrows to represent delays. A branch delay arrow appears after the corresponding branch signifying that delay "starts" once the branch completes. A load delay arrows is shown before the corresponding load, signifying that load latency "ends" when the load

Figure 1.2 Abstract example of pre-execution.

completes.

The right side of the figure shows how pre-execution hides these two latencies. The original (master) thread is again on the left. On the right is a pre-execution thread that fetches and executes the problem load and branch (in dark gray) and their computation (in lighter gray). The pre-execution thread is forked by the main thread after the first instruction in the problem computation is encountered. Because it executes fewer instruction, the pre-executing computation initiates the memory request for the problem load earlier than the master thread is able to on its own. By the time the master thread arrives at the problem load, the response from memory has already arrived and its latency has been effectively absorbed by the pre-execution thread. The pre-execution thread also hides the branch resolution latency from the master thread by sending the branch result to the fetch stage of the master thread. Pre-execution can hide pipeline latencies by sending pre-computed results to pipeline stages that occur before execution.

#### **1.3.2 Aspects of Pre-Execution**

Pre-execution is a simple idea. However, it has several aspects that may not be initially obvious. We make those explicit here.

The process of reducing master thread value latency is composed of two tasks. First, the desired value must be *computed* before the master thread needs it. Second, the value must be *communicated* to the master thread. The communication mechanism is specific to the implementation of pre-execution. It may be something as simple as the data cache which communicates pre-executed load values to the master thread implicitly via the prefetching effect, a branch predictor interface for communicating pre-executed branch outcomes, or something else entirely. The conceptual center of pre-execution lies in the much harder task of computing a given value faster than the master thread is able to.

Producing a value faster than the master thread requires that the value's

entire computation is executed ahead of its master thread schedule. However, because the execution schedule is constrained by the sequencing schedule, simply "compressing" a computation's execution schedule will not significantly hoist (move up) its execution latency, unless its sequencing schedule is similarly compressed. We call the compressed sequencing of a computation—i.e., a sequencing that skips over unrelated master thread instructions—*data-driven sequencing*. Data-driven sequencing is a key component of pre-execution.

While data-driven sequencing allows long latencies to be initiated earlier during the execution of a program, decoupling is needed to allow these latencies to be tolerated. Latencies are "exposed" when the processor runs out of useful instructions to execute in parallel with them. A long latency instruction stalls the thread in which it executes, limiting the number of useful instructions whose execution can be overlapped with its own to the size of the window. By pre-executing instructions in a separate, decoupled context, we effectively move their latencies to a different thread. Now, when the latency is incurred, only the pre-execution thread stalls. The main thread can keep fetching, executing, and retiring arbitrary numbers of instructions. Performance does not visibly degrade until the main thread itself experiences a stall.

Data-driven sequencing powers pre-execution, but it also casts it in a *complementary* role. In-order sequencing of the complete program unambiguously establishes the data dependences that produce the program's intended outcome. There is only one currently known way of determining whether a data-driven sequencing of a computation produces data dependences that precisely correspond to those established by in-order sequencing of the complete program: executing the two sequences and comparing the results. This fact has two implications. First, any data-driven sequencing activity—and consequently pre-execution—must be performed *redundantly* with the in-order sequencing of the complete master thread. Second, a pre-executed result can only be used *speculatively* by the master thread—i.e., it must verified via re-execution. Now, redundant execution can be avoided if a pre-executed result can be proven to be correct via some sequencing-based invariant. In fact, we later introduce a mechanism for doing just that. However, redundant sequencing is unavoidable. Since a processor does not contain nearly enough bandwidth to redundantly sequence the computation of every branch and every load (even if this bandwidth did exist, it would very likely be better used to sequence other programs), pre-execution must be staged as a rarely-used complement to a second, lower cost technique that can perform the bulk of the heavy lifting with satisfactory results. Fortunately, value-analytical prediction is such a technique.

Despite its relatively high cost, complementary-technique status and "merely speculative" nature, pre-execution is a powerful general mechanism. Pre-execution fundamentally overcomes the basic limitations of superscalar processors to provide timely values for problem instructions when these cannot be supplied early enough and accurately enough by any other means. When used judiciously, pre-execution can provide a significant performance benefit.

# **1.3.3 A Definition of Pre-Execution**

To help understand the important aspects of pre-execution as well as its context in the realm of high-performance sequential processing, we provide a formal definition. Pre-execution is characterized by three properties:

- *Proactive, out-of-order sequencing of problem computations.* If master thread stalls are to be *avoided*, then problem instruction (PI) value latency must be overlapped with instructions that are older than the PI instance itself. Doing so requires both foreknowledge of the downstream existence of the PI instance (proactive) and the ability to get to it faster than the master thread (out-of-order sequencing). Proactive, out-of-order sequencing removes the in-order sequencing constraint from PI computations, allowing them to be hoisted arbitrary distances with respect to the master thread.

- Decoupling of problem computations from the master thread. Decoupling enables arbitrary degrees of overlapping and latency hiding. Decoupling a problem computation from the master thread—e.g.., executing it in a different thread—effectively "moves" the latencies and stalls associated with that computation to that thread. Since stalls incurred within one thread do not effect the other thread, long latencies moved to a pre-execution thread may be overlapped with an arbitrary number of useful master thread instructions. In parallel with a stall in a pre-execution thread, the master thread can keep retiring instructions out of the window, sequencing new instructions into the window, and generally doing useful work for an arbitrary number of cycles.

• Applicability to ordinary, unmodified, sequential programs. There are systems that naturally support proactive out-of-order sequencing and decoupling. However, these do not also support arbitrary sequential programs. To be applied to sequential programs, pre-execution is cast in a way that relieves it from architectural correctness obligations, leaving it only with statistical correctness obligations—i.e., pre-execution must do the right thing often enough so that overall performance improves.

There have been several proposed pre-execution implementations [14, 20, 36, 68, 69, 72, 71, 73, 85, 106]. Speculative data-driven multithreading (DDMT) [73] is the subject of this dissertation, all the rest will be discussed in Chapter 6. All of these implementations share the above three properties which do *not* specify (a) whether pre-executed computations are copied from the program or created from scratch to mimic computations within the program, (b) whether the computation selection process is manual or automatic, or (c) how pre-executed results are communicated to the master thread. It is the implementation details of these aspects that differentiate pre-execution systems from one another.

These properties also serve to distinguish pre-execution implementations from systems that use performance enhancing execution modes other than preexecution. Systems that redundantly sequence pieces of the program in a controldriven manner (i.e., sequence more instructions than are necessary to execute specific computations) [4, 8, 54] are not pre-execution systems. Neither are systems that divide a sequential program along dynamic control boundaries [2, 29, 38, 83]. Systems that redundantly sequence computations but do not decouple them from the main program—i.e., duplicate computations in line with the main program—are not considered to perform pre-execution. Finally, systems that require changes to the basic representation and externally visible execution model of the program [5, 24, 42, 46, 63, 74, 75, 78, 89, 91, 98] are also excluded by this definition. Chapter 6 will discuss several of these systems as well.

### **1.3.4 Implementation: Speculative Data-Driven Multithreading (DDMT)**

A pre-execution implementation has two groups of components. The first group contains *pre-execution setup tasks*—tasks that are not fundamentally coupled to the runtime mechanics of pre-execution. These tasks are certainly crucial, but their completion sets up pre-execution rather than actively participating in every pre-execution instance. These tasks may be performed once, potentially statically, and their cost may be amortized over many dynamic executions. These tasks include identification of static problem instructions, selection of computations for problem instructions, and communication of problem computations to the processor.

The second group of components implement *pre-execution runtime tasks* tasks that are performed every time a pre-execution instance takes place. Runtime tasks are *initiation and initialization* of problem computations, *pre-execution* of problem computations, and *communication* of pre-executed results to the master thread. The cost of these tasks is dynamic and any inefficiency in their implementation directly detracts from the performance impact of pre-execution.

Speculative data-driven multithreading (DDMT) is an implementation of pre-

execution as it is defined above. DDMT's runtime component is built as a microarchitectural extension to a dynamically-scheduled superscalar processor that uses a physical-register-style out-of-order execution core. The proposed implementation can also leverage some of the microarchitectural components that would be present in a processor that supports simultaneous multithreading (SMT) [22, 26, 94, 95, 102]. The choice of processor substrate is motivated by the advantages that a centralized pipeline organization and a shared memory system provide for pre-execution.

Like most other pre-execution proposals, DDMT uses the shared memory hierarchy to allows a pre-executing computation to perform de facto cache-prefetching for a master thread. However, unlike all other proposals, DDMT implements a second, very aggressive channel for communicating pre-executed results to the master thread. Specifically, it stores individual pre-executed instruction results in the shared physical register file and then passes them one-by-one to the master thread via a modification to register renaming called *register integration*.

To complement the proposed implementation of the runtime component, this dissertation presents a framework for automated selection of pre-execution computations which may be used as the basis for a future implementation. The actual implementation of the setup component of DDMT is left open, although several implementations are considered and discussed at the end of Chapter 3.

This dissertation includes a simulation-driven performance evaluation of DDMT. The baseline for this evaluation is an aggressive 8-wide superscalar processor with large caches and a large branch predictor. Despite high baseline per-

formance, we find that DDMT achieves speedups of 10% to 15% on general purpose integer programs. Performance improves as DDMT successfully reduces both the average load latency and the average branch mis-prediction resolution latency in these programs.

# **1.4 Dissertation Contributions and Outline**

This dissertation's thesis comprises the following two assertions:

- Pre-execution is a good method of extracting additional ILP from sequential programs.

- Speculative data-driven multithreading (DDMT) is a good instantiantion of pre-execution, supporting an evolutionary implementation of its runtime component and automation of its setup component.

In this dissertation, I make the following contributions:

- I introduce and define pre-execution.

- I characterize data-driven threads (DDTs) and describe an algorithm for automatically extracting and selecting useful DDTs from program traces.

- I introduce and describe speculative data-driven multithreading (DDMT), an implementation of pre-execution, as a set of extensions to a dynamically scheduled superscalar processor.

- I present an empirical evaluation of DDMT in support of my thesis.

The remainder of the dissertation is organized into six chapters. Chapter 2 presents the DDMT pre-execution model—i.e., the way in which DDMT implements pre-execution. The use of register integration has many implications which

make DDMT's interpretation of pre-execution rather distinctive. Chapter 3 describes the metrics and algorithms used in the process of automatic extraction and selection of candidate pre-execution computations. Chapter 4 presents the DDMT microarchitecture, focusing on the extensions and modifications required to implement DDMT on top of a conventional superscalar design. A large fraction of the chapter deals with the implementation of register integration, a new technique with several interesting aspects. Chapter 5 presents an empirical, simulation-driven evaluation of DDMT. The chapter contains both limit studies and characterizations that are of general interest to pre-execution, as well as a focused design-space exploration of the effects and interactions of the various DDMT components, including the DDT selection algorithm. Chapter 6 provides context for pre-execution and DDMT by discussing prior and contemporaneous related work by both myself and others. Chapter 7 summarizes the dissertation and concludes.

# **Chapter 2**

# **Pre-Execution via Speculative Data Driven Multithreading**

*Speculative data-driven multithreading (DDMT)* is our proposed implementations of the runtime component of pre-execution. DDMT consists of a small set of modifications to a dynamically scheduled superscalar processor.

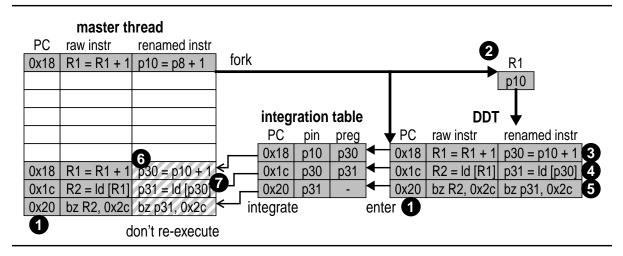

What separates DDMT from other proposed implementations is its mechanism for communicating pre-executed results to the master thread. A description of this new mechanism, which we call *register integration*, occupies a large fraction of this dissertation. Register integration implements direct, instantaneous communication via a modification to register renaming that effectively allows a master thread and pre-executing threads to share physical registers. In DDMT, pre-executed operations are often *not re-executed by the master thread*. Register integration enables DDMT to implement pre-execution in the truest sense. Preexecuted instructions are actually instructions from the original complete program whose execution has been time-shifted ahead of (i.e., pre) its "natural" place in the program. DDMT's unit of pre-execution is the *data-driven thread (DDT)*. A DDT is a sequence of instructions that encodes the computations of one or more problem load or branch instances. Each static DDT is associated with a static *trigger instruction*. Whenever the master thread encounters an instance of a trigger instruction, the processor forks a copy of the corresponding DDT. At this point, the two threads—the master thread and the DDT—begin executing in parallel. A DDT implements pre-execution—rather than post-execution or redundant parallel execution—because it is even with the master thread at the point of the fork and from that point forward, sequences and executes a small subset of the instructions processed by the master thread.

To sequence a DDT, the processor steals some sequencing bandwidth away from the master thread. Once in the execution core, DDT instructions are dynamically and transparently interleaved with instructions from the master thread. When a DDT completes execution, its hardware context is reclaimed but the results it computed are still "alive" in physical registers. The master thread uses register integration to locate these pre-computed values, associate them with the proper corresponding instructions in its own sequential stream and claim them as its own.

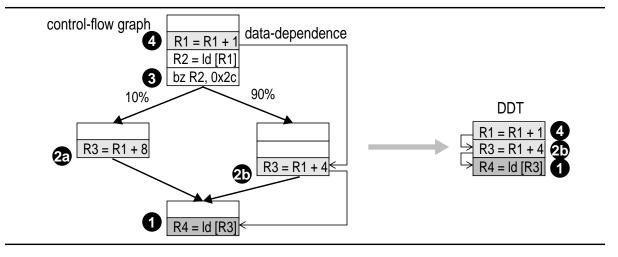

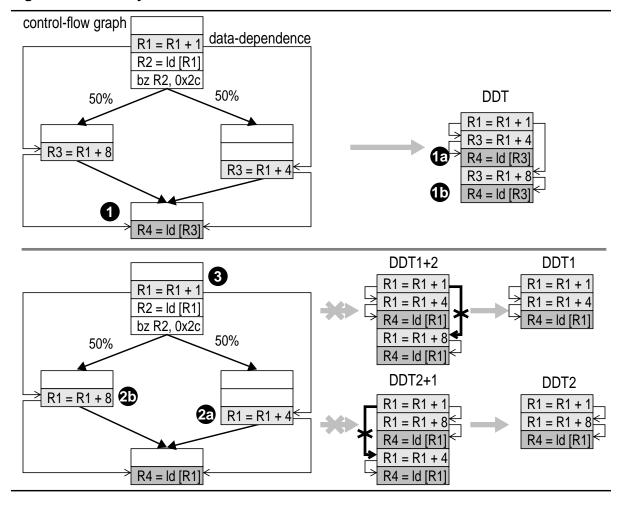

The use of register integration conveys many benefits—both performance and otherwise—but also imposes many constraints on DDMT. The most stringent constraint prevents DDTs from interpreting control-transfers of any kind—both implicit and explicit—and hence from using control-flow for sequencing. The inability to use control-flow restricts the kinds of DDTs that can be pre-executed. However, this restriction is not fatal as DDMT can use various techniques to "simulate" control-flow. A second constraint imposed by register integration is that DDTs must match dynamic program dataflow graphs precisely, instruction for instruction, and may not be optimized beyond those graphs. The inability to optimize DDTs hurts performance. Ironically enough, however, it also restricts DDT structure sufficiently to allow the DDT selection process to be automated.

Automatic DDT selection and the details of the DDMT microarchitecture are the subjects of chapters 3 and 4, respectively. In this chapter we describe DDMT's implementation of pre-execution. We briefly introduce the microarchitecture and walk through a "day in the life of a DDT." We also introduce some key concepts of register integration. These are needed to motivate the control-flow and optimization restrictions. The bulk of the chapter describes the DDMT pre-execution model the collection of unique constructs employed by DDMT to circumvent, but sometimes to actively exploit, the constraints imposed on it by register integration.

# 2.1 DDMT Primer

A description of the DDT execution model requires a basic understanding of the mechanics of DDMT. This section presents a brief introduction to the DDMT microarchitecture, describes its basic operation, and introduces the function of register integration.

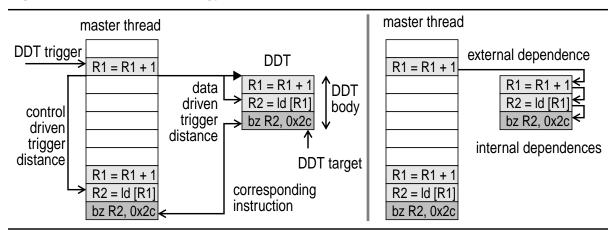

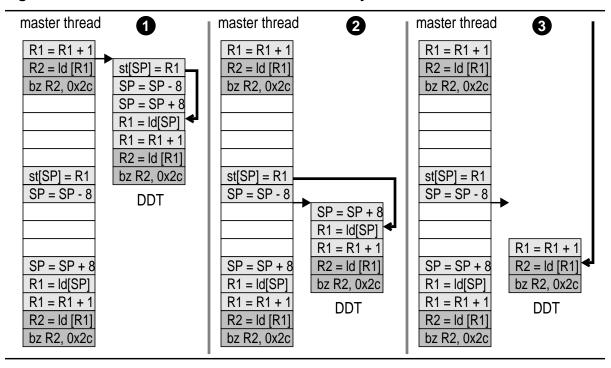

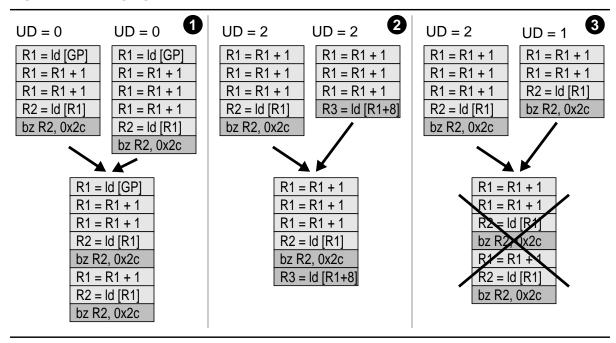

Figure 2.1 DDMT terminology.

# 2.1.1 Terminology

To help with the rest of the chapter, we begin by establishing some terminology. We may have used some of this terminology loosely already. At this point we would like to formalize it using Figure 2.1 as an aid.

The sequential, control-driven program thread is referred to as the *master thread*. A pre-executing computation is called a *data-driven thread* or a *DDT*. We use the term DDT in both a static and a dynamic sense. A DDT is both the static description of a problem computation and a pre-executing dynamic instance of that computation. We most commonly use the term in its dynamic sense. When speaking of the static representation of a DDT, we will use the term *static DDT*.

A DDT has several components. The *body* of a DDT is the sequence of instructions that DDT pre-executes. The *DDT target(s)* are the problem instruction instances the DDT is ultimately attacking. An important component of a DDT and a term we will use frequently is the *DDT trigger*. The DDT trigger is an instruction in the master thread that "triggers" the forking of the DDT. The DDT trigger is not a part of the DDT body as it is not pre-executed. Like a DDT, the DDT trigger is also both a static and a dynamic term. A static DDT trigger is associated with a static DDT. A dynamic instance of a static DDT trigger triggers the forking of a dynamic instance of the corresponding static DDT.

Each dynamic DDT instruction has (hopefully) a *corresponding instruction* within the master thread. Collectively, a dynamic DDT has (again, hopefully) a *corresponding computation* within the master thread.

When speaking of a DDT instruction—especially in the context of calculating how much faster a DDT can sequence to a given instruction than the master thread can sequence to its corresponding instruction—we will refer to the instruction's *trigger distance*. An instruction's trigger distance is the number of dynamic instructions between itself and its DDT's trigger instruction. A DDT instruction actually has two trigger distances. The *data-driven trigger distance* is its trigger distance from within the DDT. Its *control-driven trigger distance* is the trigger distance of its corresponding instruction within the master thread. The data-driven trigger distances of the instructions in a DDT are consecutive and start from zero. The control-driven trigger distances of the same instructions are not consecutive reflecting the fact that the corresponding master thread instructions are separated by other unrelated instructions. An instruction's data-driven trigger distance is always smaller than or equal to its control-driven trigger distance.

When discussing DDT pre-execution, we will speak of values and data-depen-

dences. In doing so, we distinguish between two kinds. A value or a data-dependence is *DDT-internal* if both producer and consumer of the value are DDT instructions. A value or a data-dependence is *DDT-external* if the consumer is a DDT instruction and the producer is a master thread instruction outside the DDT. The producer of a DDT-external value may be the trigger instruction or any instruction older than the trigger. However, it cannot be any instruction younger than the trigger. Note, there is *no* explicit flow of values from a DDT to the master thread. In other words, master thread instructions do not read values written by DDT instructions. The only way for DDT values to flow back to the master thread is via register integration and once integrated a DDT value effectively "becomes" a master thread value.

Finally, we also need some terminology in order to effectively discuss problem instructions. A *problem instruction (PI)* is a static instruction that meets some performance criteria. The precise criteria are unimportant right now, only the term is important. The dynamic instances of a problem instruction are collectively called *problem instruction instances (PIIs)*. We distinguish between two kinds of PIIs. The PIIs that dynamically exhibit problems—i.e., the particular dynamic instances of a load which miss in the cache and the particular dynamic instances of a branch which are mispredicted—are called *performance-degrading instances (PDIs)*. The PIIs that do not exhibit problems are called *non-performance-degrading instances (NPDIs)*.

# 2.1.2 DDMT Microarchitecture Overview

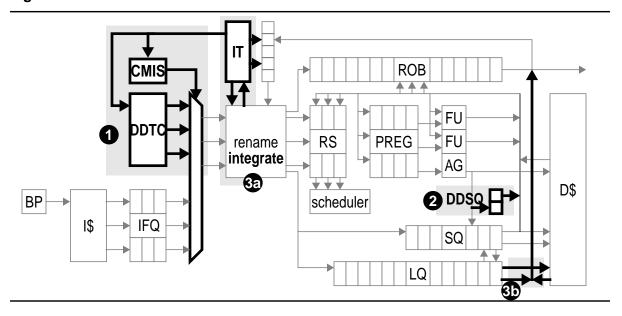

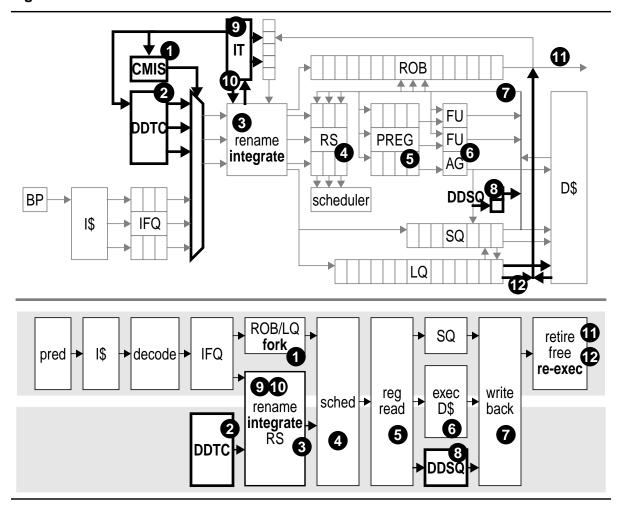

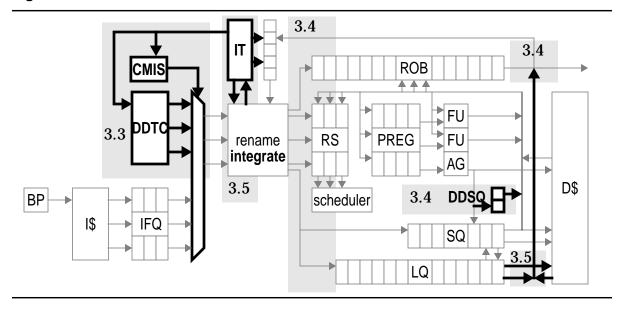

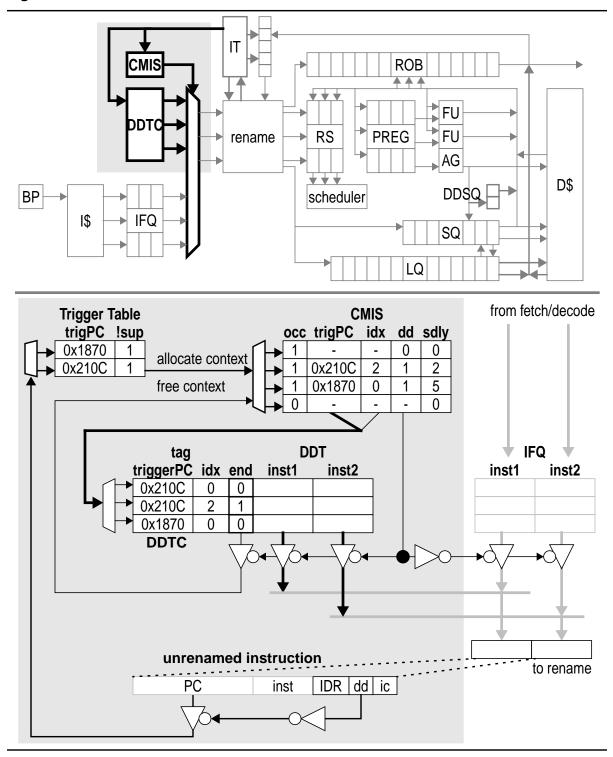

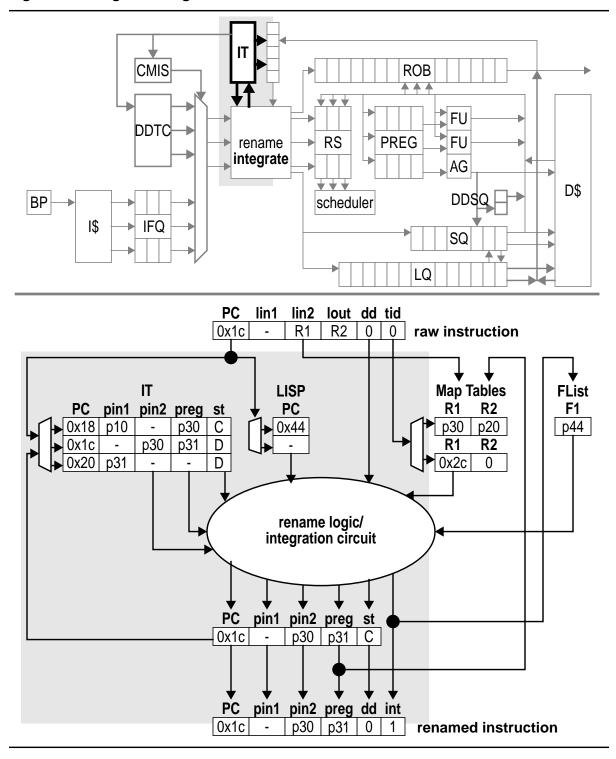

DDMT is implemented as a set of localized extensions and modifications to a dynamically scheduled superscalar processor with a physical register file style execution core microarchitecture. Figure 2.3 shows a block diagram of the DDMT microarchitecture. The DDMT-specific components are emphasized.

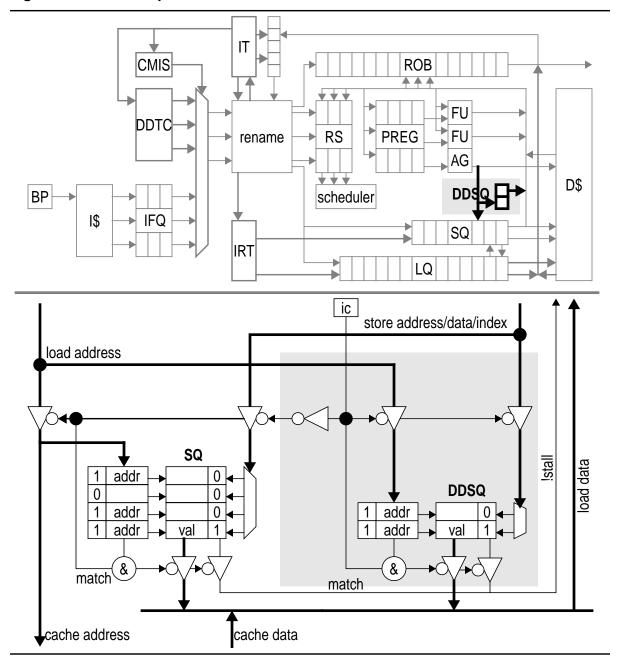

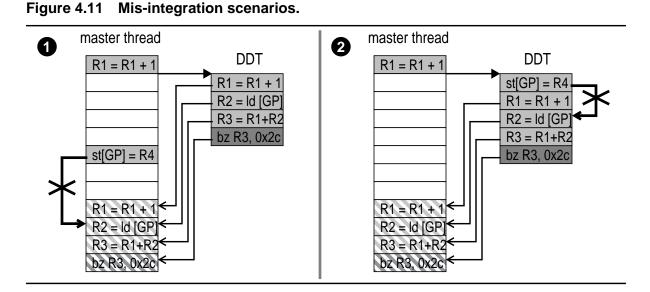

DDMT extensions come in three groups. The first group (marker #1) is the DDT-specific front end. The major components in this group are the *data-driven thread cache (DDTC)* and the combined *context manager/injection scheduler (CMIS)*. The DDTC stores static DDTs. The CMIS is responsible for forking DDTs, allocating and deallocating hardware register contexts, and scheduling active DDTs for "injection" into the execution core. The second group (marker #2) comprises a single extension to the out-of-order execution core, the *data-driven*

*store queue (DDSQ).* The DDSQ is the DDT analog of the conventional store queue (SQ). It is required because DDT stores must be handled differently than conventional stores. The final group of extensions is the implementation of register integration. The major components in this group are the *integration table (IT)* and integration logic which act during the register renaming stage (marker #3a) and a load re-execution mechanism (marker #3b) which acts at the retirement stage.

## 2.1.3 The Life of a DDT

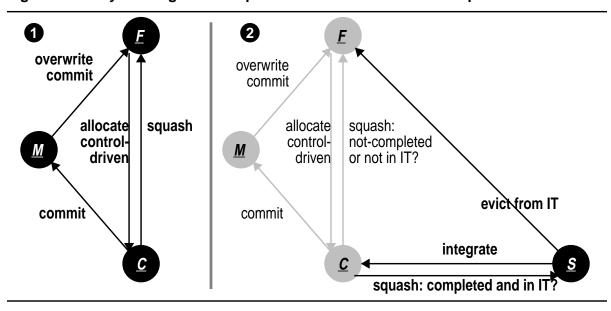

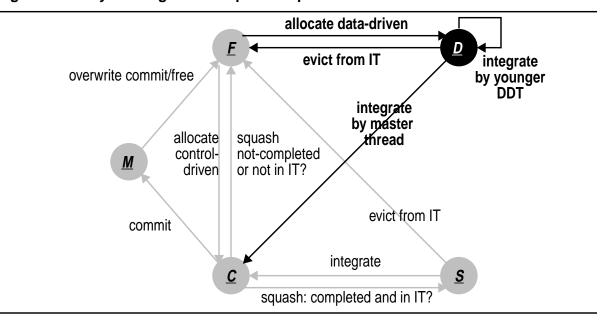

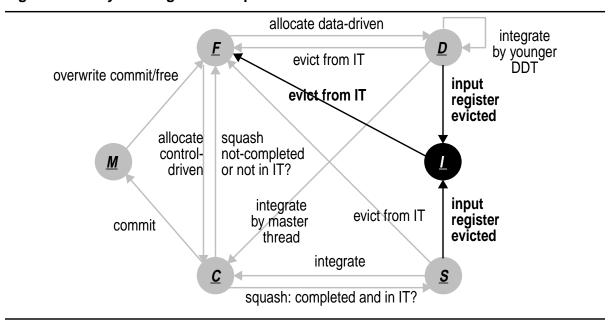

With a basic understanding of the DDMT microarchitecture, we turn to its mechanics. Figure 2.3 reprises the microarchitecture and augments it with a dual pipeline diagram. The top pipeline shows the processing stages of controldriven—i.e., master thread—instructions. The bottom pipeline shows the processing stages of data-driven DDT instructions. Stages that straddle both pipelines are common to both types of instructions. The matching numbered markers on the figure represent the important events in the life of a DDT.

A DDT is born when the master thread renames its trigger instruction. The CMIS observes the master thread's renaming stream and forks the corresponding DDT if any instruction matches a trigger (marker #1). Forking a DDT consists of allocating a free hardware register context (map table) for it, initializing this context with a copy of the master thread's context and scheduling the DDT for injection into the renaming stage. Since DDTs are purely speculative, the CMIS may ignore a trigger sighting if, for instance, no free register context is available.