# **Specifying System Requirements for Memory Consistency Models**

Kourosh Gharachorloo Sarita V. Adve Anoop Gupta John L. Hennessy Mark D. Hill

Technical Report #1199

December 1993

# Specifying System Requirements for Memory Consistency Models \*

Kourosh Gharachorloo<sup>†</sup>, Sarita V. Adve<sup>‡</sup>, Anoop Gupta<sup>†</sup>, John L. Hennessy<sup>†</sup>, and Mark D. Hill<sup>‡</sup>

<sup>†</sup>Computer System Laboratory Stanford University Stanford, CA 94305

<sup>‡</sup>Computer Sciences Department University of Wisconsin Madison, Wisconsin 53706

Stanford University Technical Report CSL-TR-93-594 University of Wisconsin-Madison Computer Sciences Technical Report #1199

#### Abstract

The memory consistency model of a shared-memory system determines the order in which memory accesses can be executed by the system, and greatly affects the implementation and performance of the system. To aid system designers, memory models either directly specify, or are accompanied by, a set of low-level system conditions that can be easily translated into a correct implementation. These sufficient conditions play a key role in helping the designer determine the architecture and compiler optimizations that may be safely exploited under a specific model. Therefore, these conditions should obey three important properties. First, they should be unambiguous. Second, they should be feasibly aggressive; i.e., they should not prohibit practical optimizations that do not violate the semantics of the model. Third, it should be relatively straightforward to convert the conditions into efficient implementations, and conversely, to verify if an implementation obeys the conditions. Most previous approaches in specifying system requirements for a model are lacking in at least one of the above aspects.

This paper presents a methodology for specifying the system conditions for a memory model that satisfies the above goals. A key attribute of our methodology is the exclusion of ordering constraints among memory operations to different locations by observing that such constraints are unnecessary for maintaining the semantics of a model. To demonstrate the flexibility of our approach, we specify the conditions for several proposed memory models within this framework. Compared to the original specification for each model, the new specification allows more optimizations without violating the original semantics and, in many cases, is more precise.

# 1 Introduction

A memory consistency model or memory model for a shared-memory multiprocessor specifies how memory operations of a program will appear to execute to the programmer. The most commonly assumed model is sequential

<sup>\*</sup>The Stanford University authors are supported by DARPA contract N00039-91-C-0138. Anoop Gupta is partly supported by a NSF Presidential Young Investigator Award. The University of Wisconsin authors are supported in part by a National Science Foundation Presidential Young Investigator Award (MIPS-8957278) with matching funds from A.T. & T. Bell Laboratories, Cray Research Foundation and Digital Equipment Corporation. Sarita Adve is also supported by an IBM graduate fellowship.

consistency (SC) [Lam79]. While SC provides an intuitive model for the programmer, it restricts many architecture and compiler optimizations that exploit the reordering and overlap of memory accesses [DSB86, MPC89]. This has led researchers to propose alternate models that allow more optimizations: e.g., processor consistency (PC) [GLL+90], total store ordering (TSO) [SUN91], partial store ordering (PSO) [SUN91], weak ordering (WO) [DSB86], and release consistency (RCsc/RCpc) [GLL+90]. These models are referred to as hardware-centric because they are defined in terms of relatively low-level hardware constraints on the ordering of memory accesses.

While the above relaxed models provide substantial performance improvements over SC [GGH91, GGH92, ZB92], they are difficult for programmers to reason with. To remedy this, another category of models, referred to as *programmer-centric*, have been proposed. Programmer-centric models provide a higher level system abstraction to the programmer, thus relieving the programmer from directly reasoning with memory access optimizations. Instead, the programmer can reason with SC and is only required to provide certain information about memory accesses (e.g., which accesses may be involved in a race [AH90b, GLL<sup>+</sup>90]). This information is in turn used to allow optimizations without violating SC. *DRF0* [AH90b], *DRF1* [AH93], *PL* [GLL<sup>+</sup>90], and *PLpc* [GAG<sup>+</sup>92] are example programmer-centric models that allow optimizations similar to the hardware-centric models.

To correctly and efficiently implement a memory model, the system designer must identify the hardware and software optimizations that are allowed by that model. Hardware-centric models, by the nature of their specification, directly specify such optimizations. In contrast, it is difficult to deduce such optimizations from the specification of programmer-centric models. Consequently, to aid designers, these models are also typically accompanied by a set of low-level system conditions that are proven sufficient for correctness.

For both classes of models, the low-level system specification plays a key role by directly influencing the hardware and system software implementation. Therefore, it is important for the specification to satisfy the following criteria. First, the specification should be precise and complete. Any ambiguity arising from the specification is undesirable and can lead to incorrect implementations. Second, the specification should be general, allowing a wide range of system designs and optimizations. To achieve this goal, the specification should impose as few constraints as necessary to maintain the semantics of the model. Finally, it should be easy to identify the allowed optimizations from the specification and conversely to determine if a particular implementation obeys the specification. For many of the models described above, the specifications of system constraints as they appear in the literature fall short of meeting these goals by being overly restrictive or ambiguous.

This paper presents a framework for specifying sufficient system constraints for a memory model that meets the above criteria. Our framework extends previous work by Collier [Col92], Sindhu et al. [SFC91], and Adve and Hill [AH92]. The framework consists of two parts: an abstraction of a shared-memory system, and a specification methodology for system requirements based on that abstraction. Our abstraction extends previous work by adequately modeling essential characteristics of a shared-memory system, such as replication of data, non-atomicity of memory operations, and allowing a processor to read the value of its own write before the write takes place in any memory copies. Previous abstractions either do not directly model some of these characteristics or are more complex. A key attribute of our specification methodology is the exclusion of ordering constraints among operations to different locations. This allows us to expose more optimizations while still maintaining the original semantics of a model. To demonstrate the flexibility of our approach, we specify the system requirements for several of the models discussed above. In all cases, the new specifications expose more potential optimizations than the original specifications. In some cases, the new specifications are also more precise than the original specifications. Furthermore, expressing the specifications within a uniform framework allows for an accurate comparison of the system constraints imposed by the different models.

The rest of the paper is organized as follows. Section 2 presents our abstraction for the system and our framework, and describes how system requirements may be specified through several examples. Section 3 describes how the specifications can be translated into implementation constraints for the architecture and the compiler. Section 4 compares our abstraction with previously proposed abstractions and discusses some implications of our approach. Finally, we conclude in Section 5. The detailed specification for several models with the corresponding correctness proofs are provided in Appendices B and C; Appendices A and D provide some of the other conditions that are required for correctness.

<sup>&</sup>lt;sup>1</sup>The processor consistency model considered in this paper is different from that proposed by Goodman [Goo91]. The definitions for PC and RCsc/RCpc given in [GLL+90] are modified in a minor way as explained in [GGH93].

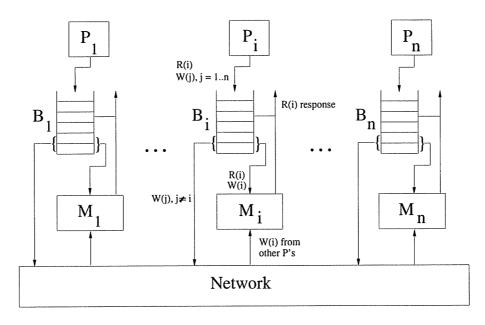

Figure 1: Abstraction for a shared-memory system.

## 2 Our Framework

This section describes our framework for specifying system requirements that are imposed by a memory model. The first part presents an abstraction of a shared-memory system that serves as the basis for the framework. We then formally define the notion of an execution and describe how conditions may be imposed on an execution in order to satisfy the semantics of various memory models. Our abstraction is influenced by the abstractions of Collier [Col92] and that of Sindhu et al. [SFC91, SUN91]. Some of the formalism and terminology are derived from work by Adve and Hill [AH92].

## 2.1 Abstraction of the System

Figure 1 shows the various components in our abstraction. The system consists of n processors,  $P_1, \ldots, P_n$ . Each processor has a complete copy of the shared (writable) memory, denoted as  $M_i$  for  $P_i$ . A read operation reads a specific memory location and a write operation modifies a location. A read operation R by  $P_i$  is comprised of a single atomic sub-operation, R(i). A write operation W by  $P_i$  is comprised of (n+1) atomic sub-operations: an initial write sub-operation  $W_{init}(i)$  and n sub-operations  $W(1), \ldots, W(n)$ . Each processing node also has a (conceptually infinite) memory buffer, denoted as  $B_i$  for  $P_i$ . A read operation on  $P_i$  results in the read sub-operations R(i) being placed into the corresponding buffer,  $B_i$ . Similarly, a write operation on  $P_i$  results in write sub-operations  $W(1), \ldots, W(n)$  being placed in  $B_i$ . The sub-operation  $W_{init}(i)$  of W corresponds to the initial event of placing  $W(1), \ldots, W(n)$  into  $B_i$ . Sub-operations are removed from  $B_i$  (not necessarily in first-in-first-out order) and then issued to the memory system. A write sub-operation W(j) by  $P_i$  executes when it is issued from  $B_i$  to the memory system and atomically updates its destination location in the memory copy  $M_j$  of  $P_j$  to the specified value. A read sub-operation R(i) by  $P_i$  executes when its corresponding read operation is issued to the memory system and returns a value. If there are any write sub-operations W(i) in  $B_i$  that are to the same location as R(i), then R(i) returns the value of the last such W(i) that was placed in the buffer (and is still in  $B_i$ ). Otherwise, R(i) returns the value of the last write sub-operation W(i) that executed in the memory copy  $M_i$  of  $P_i$ .

The above abstraction is a conceptual model meant to only capture the important properties of shared-memory systems relevant to specifying system requirements for memory models. For example, we do not model details of the processor architecture because we assume that each processor by itself behaves like a correct uniprocessor (this

<sup>&</sup>lt;sup>2</sup>These can be thought of as virtual processors. In this way, the notion of process or processor become interchangeable if there is one process per virtual processor.

<sup>&</sup>lt;sup>3</sup>All n sub-operations may not be present in an execution; see Condition 5.

notion is discussed further in the next section). Similarly, we only model memory operations to shared writable data. Below, we explain how the different features of the above abstraction (i.e., a complete copy of memory for each processor, several atomic sub-operations for a write, and buffering operations before issue to memory) adequately model shared-memory systems.

The first two features of a complete memory copy per processor and several atomic sub-operations for writes are based directly on the abstraction by Collier [Col92] and have been previously used as the basis for specifying system requirements for memory models (e.g., DRF1 [AH92]). Dubois et al.'s "perform with respect to" abstraction [DSB86, SD87], though different in flavor, also effectively captures these concepts. Providing each processor with a copy of memory serves to model the multiple copies of a datum that are present in real systems due to the replication and caching of shared data. For example, in reality the copy of memory modeled for a processor may represent a union of the state of the processor's cache, and blocks belonging to memory or other caches that are not present in this processor's cache.

The multiple sub-operations attributed to each write operation model the fact that updating multiple copies of a location may be non-atomic. Adve and Hill [AH92] explain the correspondence to real systems as follows (slightly paraphrased). "While there may be no distinct physical entity in a real system that corresponds to a certain sub-operation, a logically distinct sub-operation may be associated with every operation and a memory copy. For example, updating the main memory on a write corresponds to the sub-operations of the write in memory copies of processors that do not have the block in their cache. Also, while sub-operations may not actually execute atomically in real systems, one can identify a single instant in time at which the sub-operation takes effect such that other sub-operations appear to take effect either before or after this time." Note that in reality, write operations may actually invalidate a processor's copy instead of updating it with new data. Nevertheless, the event can be modeled as an update of the logical copy of memory for that processor.

The third feature, i.e., the memory buffer, represents a significant addition to most previous abstractions, and seems necessary to capture the behavior of many multiprocessor system designs, such as Silicon Graphics and SUN multiprocessors. Again, there may be no physical entity corresponding to this buffer in a real system. The intent of the buffer is to model the scenario where a processor reads the value of its own write before any of the write's sub-operations take effect in memory. This scenario can occur in a cache-coherent multiprocessor if a processor does a write to a location that requires exclusive ownership to be requested and allows a subsequent read (issued by itself) to that location to return the new value while the ownership request is pending. <sup>4</sup> Sindhu et al.'s abstraction [SFC91] models this effect through a conceptual write buffer and allowing the read to return the value of a write before it is retired from this buffer. However, their abstraction is limited in two aspects: they assume the processor stalls on a read operation until a value is returned and they model writes with a single sub-operation. Thus, they do not model out-of-order reads and non-atomic writes.

The abstraction used by Gibbons et al. [GMG91, GM92] to formalize the system requirements for properly-labeled (PL) programs and release consistency meets the criteria we have discussed above; i.e., it models the existence of multiple copies, the non-atomicity of writes, the out-of-order execution of memory operations, and allowing the processor to read its own write before the write is issued to the memory system. (The  $M_{base}$  abstraction in [GMG91] is limited because it does not model out-of-order read operations from the same processor; however, the non-blocking  $M_{base}$  abstraction in [GM92] removes this restriction.) While their abstraction meets our goals, the methodology used in [GMG91, GM92] to specify system requirements is overconstraining and does not fully expose the range of possible optimizations. We will further discuss their abstraction and framework and contrast it to our approach in Section 4.

The next subsections define the notion of an execution and describe how extra constraints may be placed on the ordering of memory sub-operations in an execution in order to satisfy the semantics of various memory models.

#### 2.2 Definition of an Execution

The abstraction presented in the previous section provides the motivation and intuition for the formalism we present below. Based on this abstraction, the system consists of n processors,  $P_1, \ldots, P_n$ . We use the same terminology used in the previous section to refer to read and write operations (and sub-operations) to shared-memory. A shared read operation R by  $P_i$  is comprised of a single atomic sub-operation, R(i). A shared write operation W by  $P_i$

<sup>&</sup>lt;sup>4</sup>Such implementations are covered more thoroughly in Section 3.

is comprised of (n+1) atomic sub-operations: the initial write sub-operation  $W_{init}(i)$  and n sub-operations W(1), ..., W(n) (all sub-operations of W access the same location and write the same value).<sup>5</sup>

We define an execution of a multiprocessor program as follows. A multiprocessor execution consists of a set of instruction instances and a relation called the program order on these instruction instances. The program order relation is a partial order on the instruction instances, where the partial order is total for the instruction instances issued by the same processor and is determined by the program text for that processor [SS88]. In addition, the execution consists of a set of shared-memory sub-operations that correspond to the instruction instances that access shared-memory. Note that read and write sub-operations to private memory are not included in this set. The notion of an execution is formalized in Definition 1. Below we discuss two conditions that every execution should obey.

The first condition on the execution (Condition 1) is that each processor performs its computation correctly. We refer to this as the uniprocessor correctness condition. Since this work is directed towards specifying multiprocessor behavior, we do not fully formalize a correct uniprocessor, but rely on the intuitive notion. Some of the aspects of correctness we assume involve executing the correct set of instruction instances, returning correct values from private memory, and performing all register operations and local computation correctly. There is a characteristic of the uniprocessor correctness condition as stated in Condition 1 that has a subtle implication on multiprocessor systems. Given an execution E of a correct uniprocessor, if an instruction instance *i* is in E, then the number of instruction instances in E that are ordered before *i* by program order should be finite. Effectively, this disallows a processor from issuing instructions that follow (by program order) infinite loops in the program. The exact effect of this requirement on multiprocessor implementations is discussed in Section 3; Appendix D discusses how this requirement may be relaxed to allow more aggressive implementations.

The second condition (Condition 2) is that for every execution, there should exist at least one total order, called the *execution order* (and denoted by  $\xrightarrow{xo}$ ), on all memory sub-operations in the execution that is "consistent" with the values that are returned by the read sub-operations in the execution. The notion of when a total order is "consistent" with the read values is formalized in Condition 2 below. Intuitively, this captures the notion that values returned by read sub-operations should obey the abstraction of the system presented in the previous section. Note that corresponding to each execution, there may be several execution orders that satisfy Condition 2.

#### **Definition 1: Execution**

An execution of a program consists of the following three components and should obey Conditions 1 and 2 specified below.

- (i) A (possibly infinite) set I of instruction instances where each instruction instance is associated with the processor that issued it, registers or memory locations it accessed, and values it read or wrote corresponding to the accessed registers and memory locations.

- (ii) A set S of shared-memory read and write sub-operations that contains exactly the following components. For every instruction instance i in I that reads a shared-memory location, the set S contains the memory sub-operation for the reads of i with the same addresses and values as in i. For every instruction instance i in I that writes a shared-memory location, the set S contains the  $W_{init}$  sub-operation for the writes of i with the same addresses and values as in i, and possibly other sub-operations of these writes in the memory copies of different processors.

- (iii) A partial order, called the program order (denoted  $\xrightarrow{po}$ ), on the instruction instances in I, where the partial order is total for the instruction instances issued by the same processor.

### **Condition 1: Uniprocessor Correctness Condition**

For any processor  $P_i$ , the instruction instances of  $P_i$  in the set I (including the associated locations and values) belonging to an execution, and its corresponding program order  $\xrightarrow{po}$ , should be the same as the instruction instances and program order of a conceptual execution of the code of processor  $P_i$  on a *correct* uniprocessor, given that the shared-memory reads of  $P_i$  (i.e., the R(i)'s) on the uniprocessor are made to return the same values as those specified in the set I.

$<sup>^{5}</sup>$ It is not necessary to explicitly model the  $W_{init}$  sub-operation. As will become apparent however, modeling this sub-operation makes it easier to reason about properties such as the value condition (Condition 2).

<sup>&</sup>lt;sup>6</sup>In general, we assume that for any total or partial order  $\xrightarrow{to}$  defined on a (possibly infinite) set K,  $\xrightarrow{to}$  orders only a finite number of elements of set K before any element k in the set K, and the remaining (possibly infinite) elements are ordered after k.

$<sup>^{7}</sup>$ To model initial values in the memory copies, we assume there are hypothetical write sub-operations writing the values and for any such write sub-operation W(i) to the same location as a sub-operation X(i) in the execution order, W(i) is before X(i).

#### **Condition 2: Value Condition**

Consider the set S of shared-memory read and write sub-operations. If set S is part of an execution, then there must exist a total order called the *execution order* (denoted  $\xrightarrow{xo}$ ) on the memory sub-operations of S such that (a) only a finite number of sub-operations are ordered by  $\xrightarrow{xo}$  before any given sub-operation, and (b) any read sub-operation R(i) by  $P_i$  returns a value that satisfies the following conditions. If there is a write operation W by  $P_i$  to the same location as R(i) such that  $W_{init}(i) \xrightarrow{xo} R(i)$  and R(i)  $\xrightarrow{xo} W(i)$ , then R(i) returns the value of the last such  $W_{init}(i)$  in  $\xrightarrow{xo}$ . Otherwise, R(i) returns the value of W'(i) (from any processor) such that W'(i) is the last write sub-operation to the same location that is ordered before R(i) by  $\xrightarrow{xo}$

Although an execution is defined in terms of a set of instructions and memory sub-operations, we also implicitly associate it with a set of memory operations that comprise the memory sub-operations. We will often refer to this set as memory operations or operations of the execution. We also extend the notion of program order to both sub-operations and operations. Thus, an operation or sub-operation precedes another by program order if their corresponding instructions do so. Further, if an instruction contains multiple memory operations, then we assume that all constituent operations are ordered by  $\stackrel{po}{\longrightarrow}$  with the exact ordering being defined by the specific instruction. Finally, except in Appendices A and D, the description of system constraints in the paper only concerns the interaction between shared-memory operations. For this reason, we may often ignore the set I of the execution, and use only S and the program order relation on S to describe the execution.

Our definition of execution is influenced by the work by Adve and Hill [AH92] and by Sindhu et al. [SFC91] and combines concepts from both. Adve and Hill define an execution similar to the above except that they do not allow a read, R(i), to return the value of a write whose sub-operation, W(i), occurs after the read in the execution order. On the other hand, Sindhu et al. model write operations as a single sub-operation. However, unlike these two definitions, we chose to include all instructions in the execution as opposed to only shared-memory operations.

From this point on, we assume the above two conditions (1 and 2) are satisfied by all specifications presented in this paper. The next section describes how extra constraints can be placed on an execution to satisfy the semantics of a given memory model.

# 2.3 Memory Model Specific Requirements

This section describes our methodology for specifying constraints on an execution to reflect memory ordering restrictions that are specific to each memory model. We first discuss general conditions that need to be satisfied by an execution and an implementation in order to maintain the semantics of a memory model. We then present specific system constraints for satisfying sequential consistency and other more relaxed memory models.

We use the following terminology below. We denote program order by  $\stackrel{po}{\longrightarrow}$ . Two operations (or sub-operations) conflict if both are to the same location and at least one is a write [SS88]. We use R (or Ri, Rj, Rk, etc.) and W (or Wi, Wj, Wk, etc.) to denote any read and write operations respectively. RW denotes either a read or a write. For RCpc, we use R\_acq and W\_rel to denote acquire and release operations, respectively.

The conditions for each model consist of three parts: the initiation condition (for memory sub-operations), the  $\xrightarrow{sxo}$  condition, and the termination condition (for memory sub-operations). Each of these parts specifies a restriction on the execution order relation. For a system to obey a memory model, any execution allowed by the system must have an execution order that satisfies each of the above three parts as specified for the corresponding model. We discuss each of these parts below.

The initiation condition for memory sub-operations is a restriction on the order of the initial write sub-operations (i.e.,  $W_{init}(i)$ ) with respect to other sub-operations. Its main purpose is to capture the program order among read and write sub-operations to the same location.

# Condition 3: Initiation Condition (for memory sub-operations)

Given two operations by  $P_i$  to the same location, the following must be true. If  $R \xrightarrow{po} W$ , then  $R(i) \xrightarrow{xo} W_{init}(i)$ . If  $W \xrightarrow{po} R$ , then  $W_{init}(i) \xrightarrow{xo} R(i)$ . If  $W1 \xrightarrow{po} W2$ , then  $W1_{init}(i) \xrightarrow{xo} W2_{init}(i)$ .

The  $\xrightarrow{sxo}$  condition imposed on the execution order is based on the  $\xrightarrow{sxo}$  relation ( $\xrightarrow{sxo}$  is a *subset* of  $\xrightarrow{xo}$ , thus the name) among memory operations that is defined for each model (examples of this follow in the next section). This condition requires certain sub-operations to execute in the same order as that specified by  $\xrightarrow{sxo}$  on their corresponding operations. The formal description follows.

# Condition 4: $\xrightarrow{sxo}$ Condition

Let X and Y be memory operations. If  $X \xrightarrow{sxo} Y$ , then X(i) must appear before Y(j) in the execution order for some i,j pairs (the i,j pairs used are specific to each model). The  $\xrightarrow{sxo}$  relation is individually specified for each memory model.

The termination condition for memory sub-operations requires that certain write sub-operations take effect in finite "time". The subset of write sub-operations that obey this condition is specified by each memory model. The condition is as follows.

#### Condition 5: Termination Condition (for memory sub-operations)

Suppose a write sub-operation  $W_{init}(i)$  (belonging to operation W) by  $P_i$  appears in the execution. The termination condition requires that the other n corresponding sub-operations,  $W(1) \dots W(n)$ , appear in the execution as well. A memory model may restrict this condition to a subset of all write sub-operations.

We define a valid execution order as one that satisfies the constraints specified by a memory model. A valid execution is then an execution that has a corresponding valid execution order. A correct implementation for a model can then be defined as one that allows valid executions only. The definitions for these terms are presented below.

#### **Definition 2: Valid Execution Order**

An execution order is valid for a memory model iff it satisfies the conditions (Conditions 3, 4, and 5) specified for that model.

#### **Definition 3: Valid Execution**

An execution is a valid execution under a memory model iff at least one valid execution order can be constructed for the execution.

# Definition 4: Correct Implementation of a Memory Model

A system correctly implements a memory model iff *every* execution allowed by the system is a *valid* execution for that model.

Typical implementations obey the constraints on execution order directly (and usually conservatively); i.e., constraints on the execution order are enforced among sub-operations in real time. However, a system designer is free to violate the constraints imposed by a specific memory model as long as the resulting executions *appear* to obey these constraints. While this provides room for flexibility, in practice, we believe it is difficult for a designer to come up with less restrictive constraints and guarantee that the resulting executions will be the same as with the original constraints. Therefore, it is important to initially provide the designer with as minimal a set of constraints as possible.

To avoid execution order constraints that are unnecessary for maintaining the semantics of a model, we exploit the following observation in our framework. Given a valid execution order  $\xrightarrow{xo}$ , any execution order  $\xrightarrow{xo'}$  that maintains the same order among conflicting sub-operations as  $\xrightarrow{xo}$  is also a valid execution order. The reason is that the order among conflicting sub-operations completely determines the values read and written by the sub-operations. Therefore, to specify valid execution orders, it is sufficient to constrain the execution order among conflicting sub-operations only. Specifically, the use of this observation in the  $\xrightarrow{sxo}$  condition is the primary distinguishing feature of our methodology. (It is possible that two execution orders may impose different orders among conflicting sub-operations and yet result in the same values being read and written by the sub-operations; however, exploiting this observation to provide the minimal possible constraints on the execution orders seems difficult.)

<sup>&</sup>lt;sup>8</sup>Note that our framework covers infinite executions since an execution is a set which can be infinite, and the conditions for different models are specified only as restrictions on this set. In practice, on a real system, one may want to test whether a partial execution (potentially leading to an infinite execution) generates a valid outcome. For this, we can define a partial execution as a set I' of instructions, a set S' of sub-operations, and a program order relation that represent the instructions and sub-operations that have been generated so far in the system and the corresponding program order. Then the partial execution generates a valid outcome or is valid if it could possibly lead to a valid complete execution; i.e., a partial execution is valid if its sets I' and S' are respectively subset of sets I and S of the instructions and sub-operations of some valid execution. Note here that in forming I' and S', we should not include speculative instructions or sub-operations that may have been generated but are not yet committed in the system.

<sup>&</sup>lt;sup>9</sup>This would not be possible for models such as linearizability [HW90] where correctness depends on the real time occurrence of events. However, for the models we have been discussing, the real time occurrence of events is assumed to be unobservable.

```

define \xrightarrow{sxo}: X \xrightarrow{sxo} Y if one of

1. X \xrightarrow{po} Y

2. X \xrightarrow{co} Y

3. atomic read-modify-write (AR,AW): if W conflicts with AR,AW, then either W \xrightarrow{sxo} AR or AW \xrightarrow{sxo} W

Conditions on \xrightarrow{xo}:

Initiation condition holds.

\xrightarrow{sxo} condition: if X \xrightarrow{sxo} Y, then X(i) \xrightarrow{xo} Y(j) for all i,j.

Termination condition holds for all sub-operations.

```

Figure 2: Conservative conditions for SC.

The above observation has been previously made by others as well. For example, Shasha and Snir [SS88] exploit a similar observation in identifying a minimal set of orders (derived from the program order) that are sufficient for achieving sequential consistency for a given program. Collier [Col92] also uses this observation for proving equivalences between different sets of ordering constraints. However, previous specifications of memory models have not exploited this observation to its full potential. Specifically, many of the specifications impose unnecessary ordering constraints on non-conflicting pairs of memory operations; even Shasha and Snir's implementation involves imposing delays among non-conflicting memory operations that occur in program order. In contrast, our framework presents a unified methodology for specifying ordering constraints that apply to pairs of conflicting memory operations only. We next present the constraints for sequential consistency in our framework and contrast the two approaches of specifying the execution order constraints among both conflicting and non-conflicting sub-operations versus among conflicting sub-operations only. We then proceed with specifications for other more relaxed memory models.

## 2.3.1 Requirements for Sequential Consistency

This section develops the system requirements for maintaining SC. We first develop a set of sufficient constraints on the execution order and then show how our framework allows us to express a substantially weakened set of constraints that still satisfy SC.

First, we define some terminology below. As before, we denote the program order by  $\xrightarrow{po}$  and the execution order by  $\xrightarrow{xo}$ . A condition like "X(i)  $\xrightarrow{xo}$  Y(j) for all i,j" implicitly refers to pairs of values for i and j for which both X(i) and Y(j) are defined [AH92]. We also implicitly assume that X(i) and Y(j) appear in the execution for all such pairs. For example, given R is issued by  $P_k$ , "W(i)  $\xrightarrow{xo}$  R(j) for all i,j" reduces to "W(i)  $\xrightarrow{xo}$  R(k) for all i" because R is not defined for any value other than k. As mentioned before, two operations conflict if both are to the same location and at least one is a write [SS88]. Two sub-operations conflict if their corresponding operations conflict with one another. The conflict order relation (denoted  $\xrightarrow{co}$ ) is defined as follows. For an execution order  $\xrightarrow{xo}$  and two conflicting operations X and Y, X  $\xrightarrow{co}$  Y iff X(i)  $\xrightarrow{xo}$  Y(i) holds for some i. If X and Y are on different processors and X  $\xrightarrow{co}$  Y, then X and Y are also ordered by the interprocessor conflict order X  $\xrightarrow{co'}$  Y. Since atomic read-modify-write operations (e.g., test-and-set and fetch-and-increment) are common in shared-memory machines, we include them in our framework as well. Given an atomic read-modify-write operation, RMW denotes the operation itself and AR and AW denote the individual read and write operations, respectively. We assume AR  $\xrightarrow{po}$  AW.

Lamport [Lam79] defines sequential consistency as follows: A system is sequentially consistent "if the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program". While this definition specifies the possible outcomes for a program, it does not directly translate into an implementation of SC. Therefore, to aid designers, we need to specify a set of conditions that more closely relate to an implementation. For example, Dubois et al. [SD87] have shown that to satisfy SC, it is sufficient to maintain program order and make writes appear atomic in an implementation. Figure 2 shows these conditions expressed in our framework.

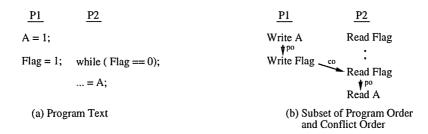

Figure 3: Example code segment.

#### Conservative conditions for SC in our framework

Figure 2 gives conservative conditions for SC in our framework. The  $\xrightarrow{sxo}$  relation ( $\xrightarrow{sxo}$  is a subset of  $\xrightarrow{xo}$ ) captures some of the conditions used to constrain the execution order  $\xrightarrow{xo}$ . The figure shows three conditions under  $\xrightarrow{sxo}$ . The first condition under  $\xrightarrow{sxo}$  captures the program order between operations from the same processor. The second condition captures the conflict order between conflicting operations (related to making writes appear atomic). And finally, the third condition captures the atomicity of read-modify-write operations with respect to other writes to the same location. (Read-modify-write operations are usually not covered in other frameworks in the literature.) Given the definition of  $\xrightarrow{sxo}$ , the constraints on the execution order  $\xrightarrow{xo}$  are as follows: (i) the initiation condition holds, (ii) if two operations are ordered by  $\xrightarrow{sxo}$ , then all sub-operations of the first operation are ordered by  $\xrightarrow{xo}$  before any sub-operation of the second operation, and (iii) the termination condition holds among all sub-operations.

To better understand the conservative conditions, consider the example code segment in Figure 3. The left side of the figure shows a program where one processor writes a location and sets a flag, while the other processor waits for the flag to be set and then reads the location. Assume the values of A and Flag are initially zero. The right side of the figure shows the program order arcs  $(\stackrel{po}{\longrightarrow})$  and the conflict order arcs  $(\stackrel{co}{\longrightarrow})$  between the write and the successful read of the flag. With sequential consistency, the read of A should return the value 1 in every execution. Let us consider how the conditions on the execution order in Figure 2 ensure this. The program order condition constrains  $\stackrel{xo}{\longrightarrow}$  as follows:  $W_A(i) \stackrel{xo}{\longrightarrow} W_{Flag}(j)$  and  $R_{Flag}(i) \stackrel{xo}{\longrightarrow} R_A(j)$  for all i,j. The conflict order condition constrains  $\stackrel{xo}{\longrightarrow}$  such that  $W_{Flag}(i) \stackrel{xo}{\longrightarrow} R_{Flag}(j)$  for all i,j. By transitivity, we have  $W_A(i) \stackrel{xo}{\longrightarrow} R_A(j)$  for all i,j, which denotes that all sub-operations of the write to A happen before the read A sub-operation, ensuring that the read returns the value 1 in all executions. It is possible to weaken the conditions in Figure 2 while maintaining the semantics of SC; we explore this more aggressive set of conditions next.

## Aggressive conditions for SC in our framework

The conditions in Figure 2 impose constraints on the execution order between both conflicting and non-conflicting sub-operations. The key insight behind the more aggressive conditions for SC is to impose constraints on the execution order among conflicting sub-operations only. Figure 4 shows these aggressive conditions for SC. As before, the  $\xrightarrow{sxo}$  relation captures the conditions that constrain the execution order. We have added two other relations,  $\xrightarrow{spo}$  and  $\xrightarrow{sco}$ , for notational convenience ( $\xrightarrow{spo}$  is a subset of  $\xrightarrow{sco}$  is a subset of the transitive closure of  $\xrightarrow{co}$ ). These relations capture certain  $\xrightarrow{po}$  and  $\xrightarrow{co}$  orders that are used in the  $\xrightarrow{sxo}$  relation. Note that  $\xrightarrow{sxo}$  is only defined among conflicting operations. Given  $\xrightarrow{sxo}$ , the constraints on  $\xrightarrow{xo}$  are as follows: if  $X \xrightarrow{sxo} Y$  (X and Y conflicting), then  $X(i) \xrightarrow{xo} Y(i)$  for all i.

Let us now consider the different conditions for the  $\stackrel{sxo}{\longrightarrow}$  relation. The first condition under  $\stackrel{sxo}{\longrightarrow}$  is uniprocessor dependence and captures the order of operations from the same processor and to the same location. Together with the initiation condition (Condition 3) and the value condition (Condition 2), this condition ensures that a read returns either the value of the last write to the same location that is before it in program order or the value of a subsequent write to that location. The second condition is coherence which ensures that write sub-operations to the same location take effect in the same order in every memory copy. The third set of conditions, denoted as the multiprocessor dependence chain, captures the relation among conflicting operations that are ordered by  $\stackrel{po}{\longrightarrow} \cup \stackrel{co}{\longrightarrow}$ . As we will see shortly, this set of conditions is the key component of our aggressive specification that differentiates it from the conservative conditions (as in Figure 2). The notation " $\{A \xrightarrow{sco} B \xrightarrow{spo} \}$ +" denotes

```

define \xrightarrow{spo}: X \xrightarrow{spo} Y if X and Y are to different locations and X \xrightarrow{po} Y

define \xrightarrow{sco}: X \xrightarrow{sco} Y if X,Y are the first and last operations in one of

X \xrightarrow{co'} Y

R \xrightarrow{co'} W \xrightarrow{co'} R

define \xrightarrow{sxo}: X \xrightarrow{sxo} Y if X and Y conflict and X,Y are the first and last operations in one of uniprocessor dependence: RW \xrightarrow{po} W coherence: W \xrightarrow{co} W multiprocessor dependence chain: one of

W \xrightarrow{co'} R \xrightarrow{po} R

RW \xrightarrow{spo} {A \xrightarrow{sco} B \xrightarrow{spo} }+ RW

W \xrightarrow{sco} R \xrightarrow{spo} {A \xrightarrow{sco} B \xrightarrow{spo} }+ RW

atomic read-modify-write (AR,AW): if W conflicts with AR,AW, then either W \xrightarrow{sxo} AR or AW \xrightarrow{sxo} W

Conditions on \xrightarrow{so}:

Initiation condition holds.

\xrightarrow{sxo} condition: if X \xrightarrow{sxo} Y, then X(i) \xrightarrow{xo} Y(i) for all i.

Termination condition holds for all sub-operations.

```

Figure 4: Aggressive conditions for SC.

one or more occurrences of this pattern within the chain. <sup>10</sup> Finally, the condition on atomic read-modify-writes is the same as in the conservative conditions. The formal proof of equivalence between these aggressive conditions and Lamport's definition of SC appears in Appendix C.

Consider the program in Figure 3 again, this time with the aggressive conditions. The relevant condition in Figure 4 that ensures the correct behavior for this program is the second condition under the multiprocessor dependence chain category. This condition applies as follows:  $W_A \xrightarrow{sxo} R_A$  because  $W_A \xrightarrow{spo} W_{Flag} \xrightarrow{sco} R_{Flag} \xrightarrow{spo} R_A$ . In turn,  $W_A \xrightarrow{sxo} R_A$  constrains the execution order among the sub-operations such that  $W_A(i) \xrightarrow{xo} R_A(i)$  for all i (this reduces to  $W_A(2) \xrightarrow{xo} R_A(2)$  since  $R_A(i)$  is only defined for i=2). Therefore, every execution is required to return the value of 1 for the read of A. Note that there are many more valid execution orders possible under the aggressive conditions as compared to the conservative conditions. For example, the following execution order,  $W_{Flag}(2) \xrightarrow{xo} R_{Flag}(2) \xrightarrow{xo} W_A(2) \xrightarrow{xo} R_A(2)$ , is allowed under the aggressive but not under the conservative conditions (because program order is violated on the first processor).

Even though the aggressive constraints place much fewer constraints on the execution order, the resulting executions "appear the same as if" the strict conditions were maintained. While the difference between the two sets of conditions is not discernable by the programmer, from a system design perspective, the aggressive conditions allow more flexibility with respect to optimizations that are possible. For example, more aggressive implementations of SC such as the lazy caching technique [ABM89] do not directly satisfy conditions in Figure 2, but can be shown to directly satisfy the aggressive conditions in Figure 4. We further explore such implications on system implementation in Section 3.

#### 2.3.2 Requirements for Other Models

The previous section presented system requirements specific to sequential consistency. However, the framework we described is general and can be used to express the system requirements for other memory models as well. While the conditions for various models differ in the specific execution orders they allow, the basic categories of conditions captured by the  $\xrightarrow{sxo}$  relation and the way  $\xrightarrow{sxo}$  is used to constrain the execution order among conflicting sub-operations is uniform across many of the specifications. We present the conditions for one of the hardware-centric models, RCpc, in this section. The conditions for several other relaxed models in addition to proofs of their correctness are provided in Appendices B and C. We have also used this framework for specifying

<sup>&</sup>lt;sup>10</sup>This is similar to regular expression notation. We also use "\*" to denote zero or more occurrences of a pattern.

```

define \xrightarrow{spo}, \xrightarrow{spo'}:

X \xrightarrow{spo'} Y if X,Y are the first and last operations in one of

RW \xrightarrow{po} W_rel

R_{-acq} \xrightarrow{po} RW

X \xrightarrow{spo} Y \text{ if } X \left\{ \xrightarrow{rch} \mid \xrightarrow{spo'} \right\} + Y

define \xrightarrow{sco}: X \xrightarrow{sco} Y if X,Y are the first and last operations in one of

R1 \xrightarrow{co} W \xrightarrow{co} R2 where R1,R2 are on the same processor

define \xrightarrow{sxo}: X \xrightarrow{sxo} Y if X and Y conflict and X,Y are the first and last operations in one of

uniprocessor dependence: RW \xrightarrow{po} W

coherence: W \xrightarrow{co} W

multiprocessor dependence chain: one of

W \xrightarrow{co} R \xrightarrow{spo} R

RW \xrightarrow{spo} \{A \xrightarrow{sco} B \xrightarrow{spo} \} + RW

atomic read-modify-write (AR,AW): if W conflicts with AR,AW, then either W \xrightarrow{sxo} AR or AW \xrightarrow{sxo} W

Conditions on \xrightarrow{xo}:

Initiation condition holds.

\xrightarrow{sxo} condition: if X \xrightarrow{sxo} Y, then X(i) \xrightarrow{xo} Y(i) for all i.

Termination condition holds for W_rel sub-operations

```

Figure 5: Aggressive conditions for RCpc.

sufficient system requirements for programmer-centric models such as PLpc [AGG+93].

Figure 5 presents the conditions for RCpc [GLL+90, GGH93] in their aggressive form where the constraints on the execution order are present among conflicting sub-operations only. We use R\_acq and W\_rel to denote a read acquire and a write release, respectively, and R and W still denote any read or write, including acquires and releases. Note that even though we are representing a different model than SC, the way the conditions are presented is quite similar to the conditions for SC in Figure 4. Of course, at the detailed level, the exact orders that are maintained do differ. As before, we use the  $\frac{spo}{s}$  and  $\frac{sco}{s}$  relations for notational convenience in order to capture the relevant  $\frac{po}{s}$  and  $\frac{co}{s}$  orders that are used in the  $\frac{sxo}{s}$  conditions. Consider the  $\frac{spo}{s}$  relation first. While for SC,  $\frac{spo}{s}$  holds between any two operations ordered by  $\frac{po}{s}$ , in RCpc,  $\frac{spo}{s}$  holds for only a subset of the operations ordered by  $\frac{po}{s}$ : (i) if the first operation is an acquire, or (ii) if the second operation is a release, or (iii) if the two operations are related by the reach relation  $\frac{rch}{s}$  (will be discussed shortly), or (iv) the transitive closure of the above. Similarly, R1  $\frac{co}{s}$  W  $\frac{co}{s}$  R2 does not constitute an  $\frac{sco}{s}$  for RCpc unless R1 and R2 are on the same processor. The conditions under  $\frac{sxo}{s}$  are also similar in form to those of SC except the third chain under multiprocessor dependence is not present in the conditions for RCpc. The manner in which the  $\frac{sxo}{s}$  relation is used to constrain  $\frac{sco}{s}$  is also identical to SC. However, the constraints imposed by the termination condition apply only to release sub-operations under RCpc. The manner in which the definition of the condition apply only to release sub-operations under RCpc.

Consider our example code segment in Figure 3 with the conditions for RCpc. Assume the write to Flag is identified as a release and the read of Flag is identified as an acquire. Therefore, we have  $W_A \xrightarrow{spo} W_{Flag}$  and  $R_{Flag} \xrightarrow{spo} R_A$ . In addition,  $W_{Flag} \xrightarrow{co} R_{Flag}$  translates to  $W_{Flag} \xrightarrow{sco} R_{Flag}$ . By the second condition under multiprocessor dependence chain, we have  $W_A \xrightarrow{sxo} R_A$  since  $W_A \xrightarrow{spo} W_{Flag} \xrightarrow{sco} R_{Flag} \xrightarrow{spo} R_A$ , which in turn imposes the constraint  $W_A(i) \xrightarrow{co} R_A(i)$  for all i. Therefore, given the read and write operations to Flag are labeled as release and acquire, respectively, the read of A will always return the value 1. However, consider the

<sup>&</sup>lt;sup>11</sup>For simplicity, we treat all read and write nsync operations [GLL+90] as acquires and releases, respectively. Appendix B shows the conditions without this simplification.

<sup>&</sup>lt;sup>12</sup>This termination condition is sufficient for properly-labeled programs (PL [GLL+90] and PLpc [GAG+92]) where all races are identified. For programs that do not identify all races (e.g., chaotic relaxation), it may be desirable to prescribe time intervals at which termination is upheld for all writes (e.g., writes may be forced to take effect in all memory copies every so many cycles).

case, for example, where the write to Flag is not labeled as a release. In this case,  $W_A \xrightarrow{spo} W_{Flag}$  no longer holds, and none of the conditions in RCpc constrain the execution order between operations to location A any more. Therefore,  $R_A(2) \xrightarrow{xo} W_A(2)$  is an allowed execution order and the read of A may return the value of 0 in some executions (an analogous situation occurs if the read of Flag is not labeled as an acquire).

We now describe the reach relation  $(\stackrel{rch}{\longrightarrow})$  that is used as part of the  $\stackrel{spo}{\longrightarrow}$  definition in Figure 5. The reach relation captures the interaction between memory operations that arise due to uniprocessor control and data dependences in each process' program and extends these dependences to include multiprocessor specific interactions as well (e.g., "dependence" implied by the  $\stackrel{spo}{\sim}$  relation). To motivate this, consider the code example in Figure 6. Here, we show P1 reading location A, testing its value, and conditionally writing location B, while P2 does the symmetric computation with accesses to A and B interchanged. Assume all memory locations are initialized to zero. In each processor, whether the write occurs depends on the value returned by the read. Assume that each processor waits for its read to take effect before allowing its write to take effect in the other processor's memory copy. In such an implementation, the writes do not appear in the execution of either processor since both conditionals fail. Now consider an implementation that speculatively allows writes to occur before the result of the conditional is resolved (e.g., possible in systems using branch prediction with speculative execution past branches). In such an implementation, it is possible to get an execution in which both conditionals succeed and both writes occur in the execution. However, the above execution is somewhat anomalous since writes in the future affect the value of previous reads that in turn determine whether the writes should have been executed at all. This type of anomalous behavior is automatically eliminated in models such as SC, PC, TSO, and PSO that maintain the  $\xrightarrow{spo}$  relation from a read to writes that follow it in program order. On the other hand, such anomalous executions could occur with models such as RCsc, RCpc, and WO if the  $\xrightarrow{rch}$  relation is not included in  $\xrightarrow{spo}$ . However, these models are intended to appear SC to a class of well-behaved programs [AH90b, GLL+90, AH93, GAG+92], and executions such as the one described above violate this intent. Therefore, it is necessary to give precise conditions that would prohibit the above type of anomalous executions.

The main purpose for the reach condition is to disallow the types of anomalous executions that arise if we allow "speculative" write sub-operations to take effect in other processors' memory copies. In most previous work, such conditions were either implicitly assumed or assumed to be imposed by informal descriptions such as "intra-processor dependencies are preserved" [AH90b] or "uniprocessor control and data dependences are respected" [GLL+90]. Some proofs of correctness (e.g., proof of correctness for PL programs executing on the RCsc model [GLL+90]) formalized certain aspects of this condition, but the full condition was never presented in precise terms. Recent work by Adve and Hill specifies this condition more explicitly in the context of the DRF1 model [AH92] and proves that it is sufficient for ensuring sequentially consistent results to data-race-free programs on models such as WO and RCsc. More recently, we have jointly formalized an aggressive form of this condition as part of specifying sufficient conditions for PLpc [AGG+93] and have proven that PLpc programs provide sequentially consistent results on models such as RCpc. Our use of the  $\stackrel{rch}{\longrightarrow}$  relation for WO, RCsc, and RCpc is a straightforward adaptation of the condition developed for PLpc. The formal proof that this type of a condition is sufficient for providing sequentially consistent results for a general class of programmer-centric models will appear in [Adv93].

Intuitively, a read operation reaches a write operation that follows it in program order (R  $\xrightarrow{rch}$  W) if the read determines whether the write will execute, the address accessed by the write, or the value written by it. <sup>13</sup> In addition, R  $\xrightarrow{rch}$  W if the read controls the execution or address of another memory operation that is before W in program order and is related to W by certain program order ( $\xrightarrow{po}$ ) arcs (e.g.,  $\xrightarrow{spo}$ ) that are used in the  $\xrightarrow{sxo}$  relation. <sup>14</sup> The formal definition of the  $\xrightarrow{rch}$  relation is provided in Appendix A and is a straightforward adaptation of the conditions developed for PLpc [AGG+93]. This formulation represents the most aggressive condition developed so far and allows for several optimizations while disallowing the anomalous executions (e.g., speculative reads are allowed; writes that do not depend on the outcome of a branch are allowed to execute before the branch is resolved).

Compared to the original conditions for RCpc [GLL+90, GGH93], the conditions presented here are more complete (with respect to precisely specifying data and control dependences) and expose more aggressive opti-

<sup>&</sup>lt;sup>13</sup>Similar to the uniprocessor correctness condition, the reach condition requires considering all instructions (not just memory instructions) to determine whether the relation holds between a pair of memory operations.

<sup>&</sup>lt;sup>14</sup>This aspect of the reach relation makes it memory model dependent since different models have different  $\xrightarrow{spo}$  relations.

$$\begin{array}{ccc} \underline{P1} & & \underline{P2} \\ \text{if } (A == 1) \left\{ & & \text{if } (B == 1) \left\{ \\ & & A = 1; \\ \end{array} \right. \right\}$$

Figure 6: Example to illustrate the reach condition.

mizations while maintaining the same semantics. We have provided the specification for several other models in Appendix B and in each case, the new specification exposes more aggressive optimizations than the original one. Similar to RCpc, the new specifications for WO and RCsc are also more complete. The next section will further discuss how exposing more optimizations expands the range of efficient implementations for each model.

# 3 Implementation Techniques

This section describes how to implement a memory model that is specified within our framework. The first part describes issues related to the architecture (i.e., hardware and any runtime software) while the second part describes compiler-related issues.

#### 3.1 Architectural Issues

This section discusses implementing the system requirements specified by our methodology at the architectural level. We assume the uniprocessor correctness condition (Condition 1) is trivially satisfied. <sup>15</sup> The remaining requirements consist of constraints on the execution order due to the the value, initiation,  $\stackrel{sxo}{\longrightarrow}$ , and termination conditions (Conditions 2-5). We use the following terminology below. A write operation W by  $P_i$  whose  $W_{init}(i)$  sub-operation appears in the execution but whose W(i) sub-operation is yet to appear is referred to as a pending write. We will use the term uniprocessor dependence condition to imply the constraint imposed on the execution order due to the uniprocessor dependence component of the  $\stackrel{sxo}{\longrightarrow}$  condition. We will use the terms coherence condition, multiprocessor dependence chain condition, and read-modify-write condition similarly, and will discuss each of these conditions separately. Of all the conditions discussed below, the multiprocessor dependence chain condition is the most important contribution of this work since it allows a wider range of optimizations and implementations than previous specifications by imposing constraints among conflicting operations only.

## 3.1.1 Value, Initiation, Uniprocessor Dependence, and Coherence Conditions

The value, initiation, uniprocessor dependence, and coherence conditions interact in a close way and so we discuss them together. The intent of the value, initiation, and uniprocessor dependence conditions is to maintain the intuitive notion of uniprocessor data dependences; i.e., a processor should "see the effect of" its own conflicting operations in program order. An intuitive way of ensuring uniprocessor data dependence would be to require that the sub-operations of two conflicting operations of a single processor should execute in program order (e.g., if  $R \xrightarrow{po} W$  on  $P_i$ , then  $R(i) \xrightarrow{xo} W_{init}(i)$  and  $R(i) \xrightarrow{xo} W(i)$ ). With our methodology, for SC and RCpc, the initiation and uniprocessor dependence conditions (Figures 4 and 5) ensure the above for two conflicting writes in program order (i.e.,  $W1 \xrightarrow{po} W2$  on  $P_i$  implies  $W1_{init}(i) \xrightarrow{xo} W2_{init}(i)$  and  $W1(i) \xrightarrow{xo} W2(i)$ ) and for a write following a conflicting read in program order. However, if a read R follows a write W in program order on  $P_i$ , the uniprocessor condition does not require  $W(i) \xrightarrow{xo} R(i)$ . While this may imply a possible violation of uniprocessor data dependence, the initiation condition requires  $W_{init}(i) \xrightarrow{xo} R(i)$  and even if  $R(i) \xrightarrow{xo} W(i)$  (i.e., write is pending), the value condition still ensures that R will return the value of W (or a later conflicting write that is before R by program order). This ensures that the essential notion of uniprocessor data dependence is maintained; i.e., a read sees the effect of the conflicting writes that are before it in program order. Below, we first describe how the value, initiation, uniprocessor dependence, and coherence conditions can be implemented, and

<sup>&</sup>lt;sup>15</sup>To satisfy Condition 1, one of the requirements is that operations following an unbounded loop (by program order) should not be executed until it is known that the loop will terminate. Appendix D discusses how this restriction may be relaxed in certain cases.

(a)

$$A = 1$$

$P2$   $A = 2$  (b)  $A = A$  (c)

Figure 7: Example code segment showing interaction between the various conditions.

then discuss their interaction which requires our less intuitive form for the value and uniprocessor dependence conditions.

# Implementation of value, initiation, uniprocessor dependence, and coherence conditions

A typical way in which the value, initiation, and uniprocessor dependence conditions are maintained is as follows (all sub-operations below are from the same processor  $P_i$ ). A write sub-operation is delayed until previous read and write sub-operations to the same location have executed in the memory copy of the issuing processor (i.e.,  $R \xrightarrow{po} W$  implies  $R(i) \xrightarrow{xo} W_{init}(i)$  and  $R(i) \xrightarrow{xo} W(i)$ ;  $W1 \xrightarrow{po} W2$  implies  $W1_{init}(i) \xrightarrow{xo} W2_{init}(i)$  and  $W1(i) \xrightarrow{xo} W2(i)$ ). Read sub-operations do not need to be delayed for previous (in program order) read and write sub-operations (except  $W \xrightarrow{po} R$  implies  $W_{init}(i) \xrightarrow{xo} R(i)$ ), but if there are pending memory write sub-operations to the same location, the read has to return the value of the pending write to the same location that is the last one before it in program order. For example, in an implementation that uses write buffers, the appropriate value is forwarded to the read if there is a conflicting write in the buffer. The above techniques are well understood since similar conditions need to be maintained in uniprocessors.

The coherence condition constrains write sub-operations to the same location to occur in the same order with respect to every memory copy (i.e., W1(i)  $\xrightarrow{xo}$  W2(i) for all i). This is typically achieved through a logical serialization point per location where writes to that location are serialized (e.g., at the home directory in a directory-based coherence protocol). Techniques for maintaining coherence are also well understood and have been covered in the literature (e.g., see [GLL+90, LLG+90] for a description of the Dash coherence protocol).

### Interaction between value, initiation, uniprocessor dependence, and coherence conditions

There is a subtle interaction between the value, initiation, uniprocessor dependence, and coherence conditions when all of them are to be satisfied by operations to a location. Consider the code segment in Figure 7. Assume all values are initially 0. Both P1 and P2 write to location A and P2 also reads this location. Let W1 denote the write on P1 and W2 the write on P2. Coherence requires all processors to observe the two writes of A in the same order. As discussed above, this is usually achieved by sending the two writes to a serialization point from where their sub-operations are sent to different memory copies in the same order. Thus, the write sub-operation of P2 (i.e., W2(2)) cannot execute in P2's memory copy as soon as it is issued. Instead, it has to be sent to a serialization point and is executed in P2's memory copy only after all other write sub-operations to A that are serialized before this write have executed in P2's memory copy. For our case, assume that P1's write is serialized before P2's write. Now consider the state when P2's write is waiting to be serialized and P2 issues its read of A. For the traditional notion of data dependences to be satisfied, this read should return the value of P2's write on A or a write that is serialized after P2's write. Thus, to satisfy data dependences, it is always safe for P2's read to return the value of P2's write. The key question that determines the form of our conditions is: can this read return the value of P2's write before the write is serialized, and hence possibly before P1's and P2's write sub-operations (W1(2) and W2(2)) are executed in P2's memory copy? The answer to this question, and the form of the uniprocessor, initiation, and value conditions, depends on the memory model.

For models which do not allow the read to return the value of P2's write before it is serialized, we do not need to model the  $W_{init}(i)$  sub-operation and we do not need an explicit value condition (i.e., the value condition would simply require a read to return the value of the last write to the same location that is before it in the execution order). Instead, we can make the uniprocessor dependence condition require that for a read following a write in program order, the read sub-operation should appear after the write sub-operation in the execution order. However, such models impose a delay on the read since it has to wait for a previous write to be serialized.

<sup>&</sup>lt;sup>16</sup>The coherence condition discussed below ensures that the sub-operations of two conflicting writes of a processor execute in the correct relative order in memory copies of other processors.

Other models (including all models discussed in this paper) can eliminate the above delay by allowing P2's read to return the value of P2's write before the write is serialized. However, with this optimization, the write sub-operation in P2's memory copy appears after the read in the execution order, and thus we cannot require the uniprocessor dependence condition to include a constraint on the order of execution of a read following a write. Instead, the traditional notion of data dependence is maintained by using the initiation and value conditions. These two conditions ensure that even if a write that is before a read by program order is executed after the read, the read will still see the effect of the write. In particular, if a write that is before a read by program order appears after the read in the execution order (i.e.,  $R(i) \xrightarrow{xo} W(i)$  even though  $W_{init}(i) \xrightarrow{xo} R(i)$ ), then the read will return the value of the last conflicting write ordered before it by program order. For example, referring back to Figure 7, let W1(2) and W2(2) denote the sub-operations for the two writes (by P1 and P2) destined for P2's memory copy and let R(2) denote the sub-operation for P2's read. Assume W1(2)  $\xrightarrow{xo}$  W2(2) by coherence, as we did above. The uniprocessor condition for the models that allow the read to occur while the write is pending corresponds to allowing  $R(2) \xrightarrow{xo} W2(2)$ . Then one possible execution order is  $R(2) \xrightarrow{xo} W1(2) \xrightarrow{xo} W2(2)$ . The value and initiation conditions for such models ensure that the value returned by R(2) is that of W2(2), and not of any write that is before W2(2), thereby maintaining data dependence.

Thus, our notions of uniprocessor dependence, initiation, and value conditions precisely and directly capture the optimization of allowing a read to return the value of its own processor's write before it is serialized. This optimization is important since it is used by commercial multiprocessors such as those by Silicon Graphics and SUN, and many of the memory models considered in this paper allow it (for SC, this had not been explicitly stated in previous work).

Often, the above optimization of allowing a read to return the value of a write that is not yet serialized is implemented in the form described by our abstraction; i.e., through early reads from the write buffer. An alternate form of implementing this optimization is as follows. A write is allowed to update the logical memory copy of the issuing processor before it is serialized. A read in this case simply returns the value in the processor's memory copy. However, care must be taken in handling the conflicting write sub-operations that arrive from other processors while the serialization of the current write is pending. This typically involves ignoring any write sub-operations (e.g., invalidation or update messages) that arrive for this location while this processor's write is still awaiting its response from the serialization point. Therefore, it effectively appears as if writes that were serialized before this processor's write took effect before it in this processor's memory copy. Some systems like DASH [LLG+90] use a hybrid scheme that is a merge of the two techniques discussed above. In DASH, a write updates the write-through first level cache immediately (second technique), but the update to the second level cache is delayed by the write-buffer until ownership is granted (first technique).

## 3.1.2 Multiprocessor Dependence Chain Condition

The multiprocessor dependence chain condition captures the relation among conflicting operations that are ordered by certain program order and conflict order arcs. This condition is a key contribution of this work since it allows a much wider range of optimizations and implementations than most previous specifications. The strength of our framework is that it makes this wide range of implementations relatively obvious, and consequently, simplifies the task of verifying if an aggressive implementation obeys a memory model.

Below, we first discuss the more conservative (and consequently simpler) implementations for satisfying the multiprocessor dependence chain condition. Then we follow with more aggressive (and consequently more difficult) implementations that exploit the extra flexibility offered by our specification approach. The discussion below focuses on implementing the multiprocessor dependence conditions for SC (Figure 4). However, the implementation techniques apply to specifications for the other models as well.

# Conservative implementations of the multiprocessor dependence chain condition

The first multiprocessor dependence chain for SC is of the form W  $\xrightarrow{co}$  R1  $\xrightarrow{po}$  R2, where all three operations are to the same location. Assume R1 and R2 are issued by  $P_i$ . Given such a chain, the condition on the execution

<sup>&</sup>lt;sup>17</sup>We assume sub-operations to the same location arrive in order from the coherence serialization point.

<sup>&</sup>lt;sup>18</sup>Invalidations may apply to more than one location since they are typically at a cache line granularity. In this case, the specific locations that are pending should not be invalidated while other locations in the cache line need to be invalidated. This can be achieved by keeping valid bits per word, for example.

order is W(i)  $\xrightarrow{xo}$  R2(i). This condition can be trivially satisfied by maintaining program order among reads to the same location. In other words, the implementation ensures that if R1  $\xrightarrow{po}$  R2 on  $P_i$  and both are to the same location, then R1(i)  $\xrightarrow{xo}$  R2(i).

The second and third conditions under multiprocessor dependence comprise of chains of  $\frac{spo}{}$  and  $\frac{sco}{}$  arcs which represent a subset of the program order ( $\frac{po}{}$ ) and conflict order ( $\frac{co}{}$ ), respectively. Given two conflicting operations X and Y at the beginning and end of such a chain, the execution order is required to obey X(i)  $\xrightarrow{xo}$  Y(i) for all i. The simple way to maintain this order is to enforce an order between the consecutive operations in the chain. This is similar to how the conservative conditions for SC (shown in Figure 2) implicitly satisfy this condition. For consecutive operations related by  $\xrightarrow{spo}$ , we can maintain the program order such that A  $\xrightarrow{spo}$  B ensures A(i)  $\xrightarrow{xo}$  B(j) for all i,j. This can be achieved by delaying sub-operations of B until all sub-operations of A are completed. ([GLL+90] gives a set of fence operations that provide one general way of achieving this delay; Appendix A further discusses the particular case when the delay is due to the  $\xrightarrow{rch}$  component of  $\xrightarrow{spo}$ .) The above is sufficient to maintain the required order for chains that do not begin with W  $\xrightarrow{sco}$  R (e.g., the third multiprocessor dependence chain for SC) and do not contain an  $\xrightarrow{sco}$  of the form R1  $\xrightarrow{co}$  W  $\xrightarrow{co}$  R2. For chains that begin with W  $\xrightarrow{sco}$  R or comprise of  $\xrightarrow{sco}$  of the form R1  $\xrightarrow{co}$  W  $\xrightarrow{co}$  R2 (where R1 and R2 are on different processors), the additional sufficient requirement is to make the writes that occur in such  $\xrightarrow{sco}$  s appear atomic. One way of making a write appear atomic is to ensure that no read is allowed to return the value of the write until all old copies of the line being written are either invalidated or updated with the new value [SD87, GLL +90].

#### Aggressive implementations of multiprocessor dependence chain condition

The primary reason our aggressive conditions lead to more flexible implementations is because we constrain the execution order only among conflicting accesses. This is most important for the specification of the orders implied by the multiprocessor dependence chain. Conservative conditions (e.g., Figure 2) typically specify the overall order by requiring order between all intermediate operations in the chain; the simple implementation of the multiprocessor dependence condition that we described above maintains the order in a similar way. However, maintaining the order between intermediate operations is not necessary for correctness. Below, we discuss implementations proposed in the literature that maintain the multiprocessor dependence condition more aggressively. We discuss the first implementation in some detail, and only give the key ideas for the others.

The first implementation is the lazy caching technique proposed by Afek et al. [ABM89]. This implementation uses a bus-based update protocol to keep the caches coherent. Sequential consistency is maintained in an aggressive way as explained below. When a processor issues a write, it only waits for the updates of its write to be queued into the FIFO input queues of the other processors and can continue with its next operation before the updates actually take effect in the caches. Therefore, the implementation does not directly satisfy the conservative conditions for SC specified in Figure 2 or the conditions specified by Dubois et al. [SD87], since  $X \xrightarrow{po} Y$  does not necessarily imply  $X(i) \xrightarrow{xo} Y(j)$  for all i,j. However, it is relatively simple to show that the implementation satisfies the aggressive conditions for SC shown in Figure 4 (i.e., the implementation directly maintains the required order between the first and last operations for any of the multiprocessor dependence chains).

A number of other aggressive implementations have been proposed for SC. Scheurich proposes a similar idea to lazy caching in his thesis, but his description of the implementation is very informal [Sch89]. Landin et al. [LHH91] propose an implementation of SC based on "race-free networks." Such networks maintain certain transactions in order, and this inherent order allows a processor to continue issuing operations as soon as its previous write reaches the appropriate "root" in the network (as opposed to waiting until the write reaches its destination caches). This is similar to the lazy caching technique since the write reaching the root in a race-free network is analogous to it being placed in the input queues of other processors in a bus-based system. Collier proposes a similar implementation for ring-based systems where one node in the ring acts as the "root" that serializes all writes [Col92]. Adve and Hill [AH90a] also propose an implementation of SC for cache-based systems that in certain cases allows a processor that has issued a write to proceed as soon as the write is serialized (as opposed to delaying the processor for the write to take affect in all cache copies). While none of the above techniques satisfy the conservative conditions for SC, they all satisfy the aggressive conditions.

Above, we discussed aggressive implementations in the context of SC. Similar optimizations are possible for more relaxed models. Landin et al. extend their observations for SC on race-free networks to aggressive implementations of PC on such networks. Again, this implementation satisfies the aggressive conditions for PC

(provided in Appendix B). <sup>19</sup> Dubois et al.'s delayed consistency implementation of release consistency [DWB+91] delays doing the invalidations at a destination cache until the destination processor reaches an acquire as opposed to performing the invalidations before the release on the source processor. While this does not directly satisfy the original conditions for RC [GLL+90], it can be easily shown to satisfy the aggressive conditions for RC presented in Appendix B. Adve and Hill's implementations for the data-race-free-0 [AH90b] and data-race-free-1 [AH93] programmer-centric models also use an aggressive form of the multiprocessor dependence chain condition to provide more aggressive implementations than allowed by WO and RCsc. Zucker [Zuc92] makes a similar observation in the context of software cache coherence, and finally, similar observations have led to more efficient software distributed shared memory implementations [BZ91, KCZ92].