# Register Allocation and Code Scheduling for Load/Store Architectures

by

Wei-Chung Hsu

**Computer Sciences Technical Report #722**

October 1987

(

# REGISTER ALLOCATION AND CODE SCHEDULING

# **FOR**

#### LOAD/STORE ARCHITECTURES

by

#### **WEI-CHUNG HSU**

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy (Computer Sciences)

at the

**UNIVERSITY OF WISCONSIN -- MADISON**

1987

|  |  |  | • |

|--|--|--|---|

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

#### **Abstract**

To achieve high performance, the structure of on-chip memory in a single-chip computer must be appropriate, and it must be allocated effectively to minimize off-chip communication. Since the off-chip memory bandwidth of single-chip computers is severely limited, data caches that exploit spatial locality to achieve high hit rates are not appropriate. A register file, which can be managed by compilers, might be more effective than a data cache as an on-chip memory structure. With a load/store architecture, compilers can separate operand fetches from their use by scheduling code, thus achieving high hit rates without increasing memory traffic. Register allocation also exploits temporal locality better than a data cache does.

This thesis investigates how effective register allocation could be and studies the interdependency problem between register allocation and code scheduling. A model of perfect register allocation is explored. An algorithm for optimal local register allocation is then developed. Since the optimal algorithm needs exponential time in the worst case, a heuristic algorithm which has near-optimal performance is proposed and compared with other existing heuristic algorithms. Through trace simulation, the perfect register allocation model is shown to be much more effective in reducing off-chip memory traffic than cache memory of the same size.

Code scheduling interferes with register allocation, especially for large basic blocks. Two methods are proposed to solve this interference: (1) an integrated code scheduling technique; and (2) a DAG-driven register allocator. The integrated code scheduling method combines two scheduling techniques—one to reduce pipeline delays and the other to minimize register usage—into a single phase. By keeping track of the

number of available registers, the scheduler can choose the appropriate scheduling technique to schedule a better code sequence. The DAG-driven register allocator uses the Dependency DAG to assist in assigning registers; it introduces much less extra dependency than does an ordinary register allocator. Both approaches are shown to generate more efficient code sequences than conventional techniques in the simulations.

#### Acknowledgements

It has been my privilege and good fortune to work and study with Professor James Goodman for whom I have the greatest respect. I would like to take this opportunity to thank him for all his encouragement, support, and direction. His enthusiasm, encouragement and patience have made this thesis possible.

I would like to thank the other members of my committee: Charles Fischer, Marvin Solomon, Guri Sohi, and John Beetem. I learned how to write a compiler from Charles. Marvin taught me the optimizing compilers skills. Guri spent many hours discussing with me. John offered me extremely helpful comments.

Thanks are also due to my dear friends, especially, Phil Pfeiffer and Matt Farrens, for their help in revising my writing.

I would be amiss, if I didn't acknowledge how fortunate I've been to have a family that has given me the strength to follow my dreams. I would like to express my deepest gratitude to my wife, Diane, for her sacrifice and endurance over these many years.

| • |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

# **Table of Contents**

| Acknowledgement                                                             | ii iv 1 2 5 5 7 |

|-----------------------------------------------------------------------------|-----------------|

| -<br>-                                                                      | 2<br>5<br>5     |

| 1.1. On-Chip Memory                                                         | 2<br>5<br>5     |

|                                                                             | 5<br>5          |

|                                                                             | 5               |

| A A B B B B B B B B B B B B B B B B B B                                     |                 |

| A A A A A A A A A A A A A A A A A A A                                       | 7               |

| <b>1.3.2.</b> Code Scheduling                                               |                 |

| 4 A A                                                                       | 8               |

| Chapter 2: On the Use of Registers vs Data Cache to Minimize Memory Traffic |                 |

| 2.1. The Behavior of Local Accesses and Global Accesses                     | 0               |

| 2.1.1. Temporal Locality and Spatial Locality                               | 1               |

| 2.1.2. On-chip Memory for the Stack                                         | 7               |

| 2.2. Register Allocation and Procedure Calls                                | 0               |

| 2.3. A Model for Perfect Register Allocation                                | 4               |

| 2.3.1. How Realistic is the Perfect Register Allocation? 24                 | 4               |

| 2.3.2. An Initial Evaluation                                                | 5               |

| Chapter 3: Optimal Allocation in Basic Blocks                               |                 |

| <b>3.1.</b> The Model                                                       | 8               |

| 3.2. Finding a Shortest Path in the WDAG                                    |                 |

| 3.3. The Rules for Pruning the WDAG                                         |                 |

| 3.4. The Algorithm to Find An Optimal Allocation                            |                 |

| 3.5. Special Cases                                                          | 5               |

| 3.6. A Heuristic Algorithm                                     | 46 |

|----------------------------------------------------------------|----|

| 3.7. Existing Heuristic Algorithms                             | 51 |

| <b>3.8.</b> Evaluation                                         | 51 |

| 3.9. Replacement vs Graph Coloring                             | 56 |

| 3.10. The Reevaluation of the Perfect Allocation Model         | 58 |

| 3.11. Global Register Allocation                               | 59 |

| <b>3.11.1.</b> Previous Work                                   | 60 |

| 3.11.2. Important Considerations for Good Allocations          | 63 |

| 3.11.3. Branch Frequency                                       | 64 |

| 3.11.4. The Extension of Local Allocation to Global Alloca-    |    |

| tion                                                           | 64 |

| 3.11.5. Some Required Modifications                            | 66 |

| 3.12. Register Allocation of Global Variables                  | 67 |

| Chapter 4: Compiler Techniques for Increasing Basic Block Size |    |

| 4.1. Reducing Conditional Jumps                                | 69 |

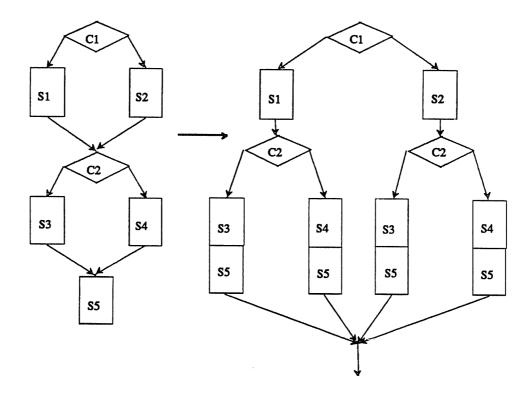

| <b>4.2.</b> Code Duplication                                   | 70 |

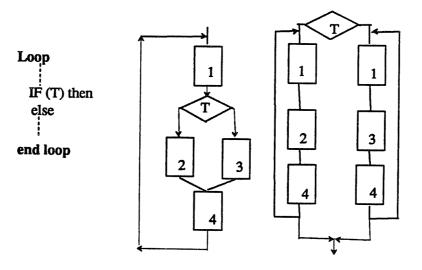

| 4.2.1. Loop Unrolling                                          | 70 |

| 4.2.2. In-Line Expansion                                       | 73 |

| 4.2.3. Code Replication                                        | 76 |

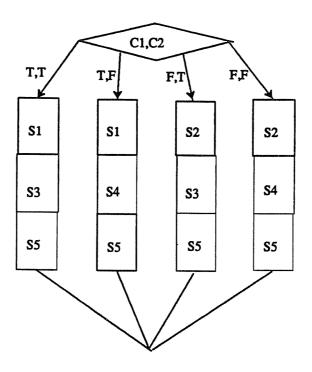

| 4.2.4. Trace Scheduling                                        | 76 |

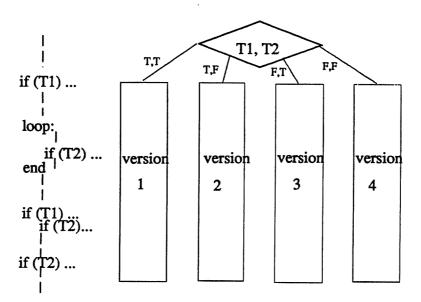

| 4.2.5. Unswitching and Multi-version                           | 81 |

| <b>4.3.</b> Others                                             | 83 |

| <b>4.3.1.</b> Loop Fusion                                      | 83 |

| Chapter 5: Code Scheduling with Limited Register Spilling      |    |

| 5.1. Introduction                                              | 86 |

| 5.2. Background                                                | 88 |

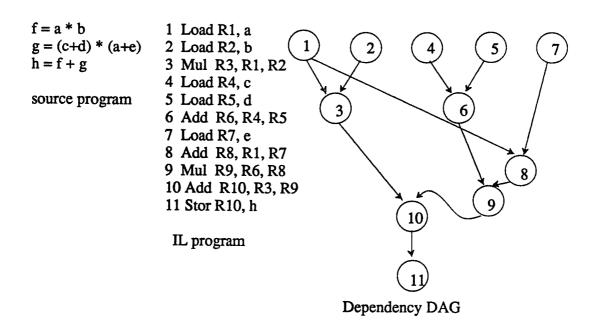

| 5.2.1. Code Scheduling Constraints: The Dependency DAG         |    |

|                                                                | 88 |

|                                                                |    |

| 5.2.2. The Use of Low Level Intermediate Languages        | 88  |

|-----------------------------------------------------------|-----|

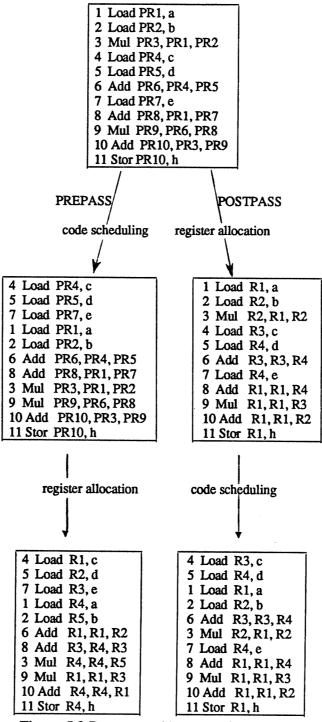

| 5.2.3. Prepass or Postpass?                               |     |

|                                                           | 89  |

| 5.2.4. Two Conflict Scheduling Techniques                 | 90  |

| 5.3. A Solution for Prepass Scheduling                    | 93  |

| 5.4. Implementation Notes                                 | 95  |

| 5.4.1. CSP, CSR and AVLREG                                | 95  |

| 5.4.2. Renaming of Pseudo-Registers                       | 97  |

| 5.4.3. Interlock Checking at Scheduling Time              | 97  |

| 5.4.4. Leader Set and Ready Set                           | 99  |

| 5.4.5. Integrated Scheduling Algorithm                    | 100 |

| <b>5.4.6.</b> A Variation on Profitable Register Spilling | 102 |

| 5.5. Scheduling Loads and Stores                          | 104 |

| 5.6. Simulation Studies and Discussion                    | 106 |

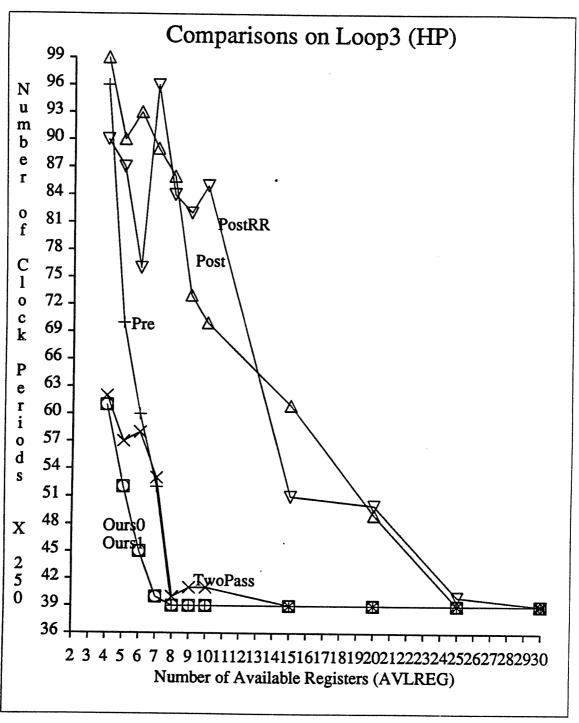

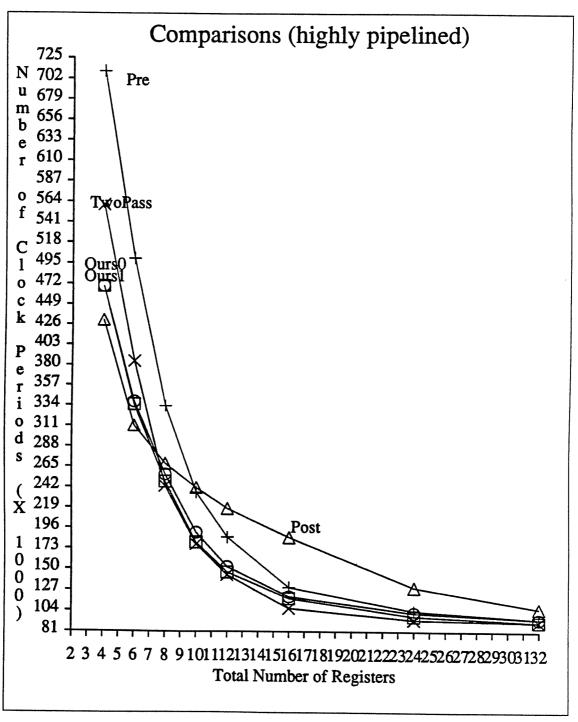

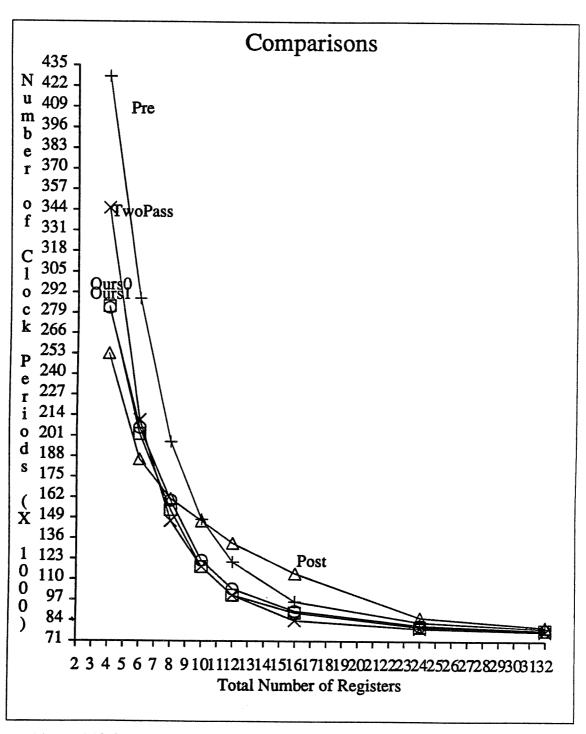

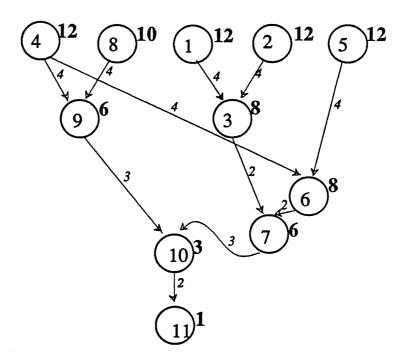

| <b>5.6.1.</b> Simulations                                 | 106 |

| <b>5.6.2.</b> Discussion                                  | 115 |

| 5.6.2.1. General Discussion                               | 115 |

| 5.6.2.2. Total vs Available Registers                     | 120 |

| 5.6.2.3. Problems with Multiple Functional Pipelines      | 124 |

| Chapter 6: DAG-Driven Register Allocation                 |     |

| 6.1. Motivation                                           | 130 |

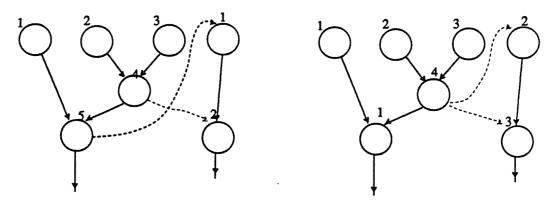

| 6.2. Balancing DAG Reconstruction                         | 131 |

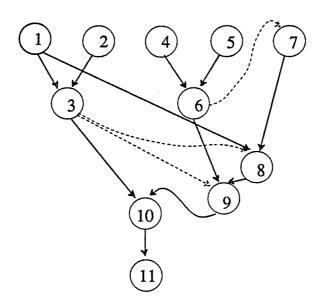

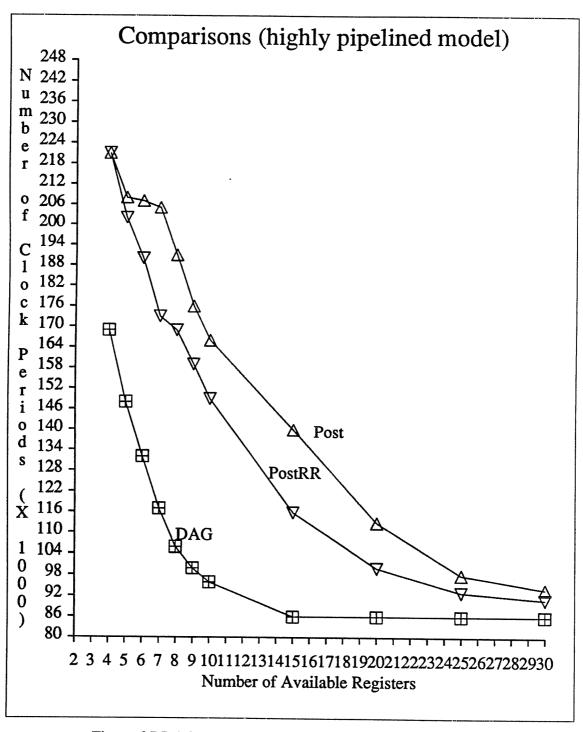

| <b>6.2.1.</b> Free WAR Dependencies                       | 132 |

| 6.2.2. Balancing the Growth of the DAG                    | 134 |

| 6.3. Implementation Notes                                 | 138 |

| 6.3.1. Update Dependent Relation Incrementally            | 138 |

| 6.3.2. Update EIT Dynamically                             | 139 |

| 6.3.3. Replacing Live Registers                           | 141 |

| 6.3.4. The Algorithm                                      | 141 |

| <b>6.3.5.</b> Example                                     | 143 |

| 6.4. The Performance of DAG-driven Register Allocation    |     |

| 0.4. The renormance of DAO-differ Register Amocation      | 148 |

# **List of Figures**

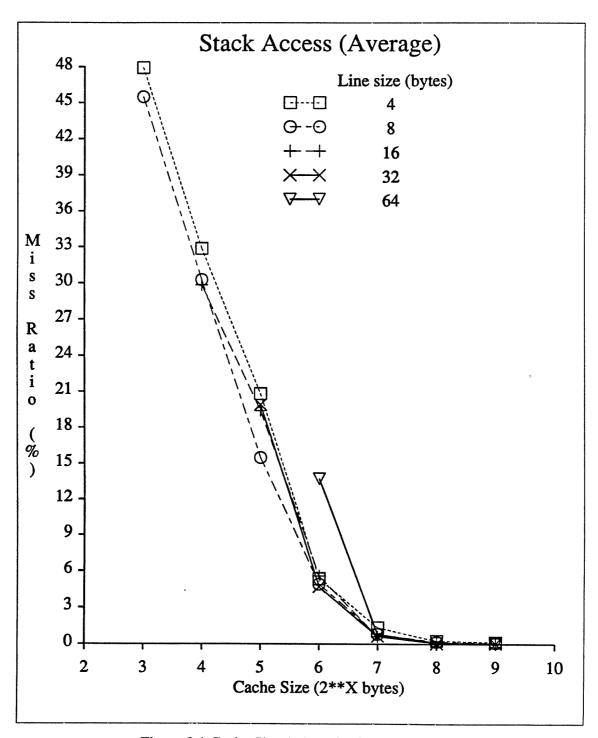

| Figure 2.1 Cache Simulations for Stack Accesses                  | 14  |

|------------------------------------------------------------------|-----|

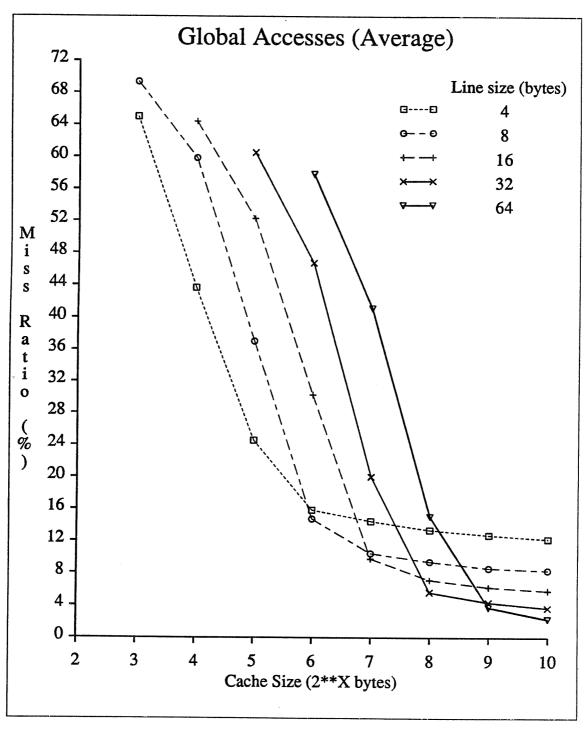

| Figure 2.2 Cache Simulations for Global Accesses                 | 15  |

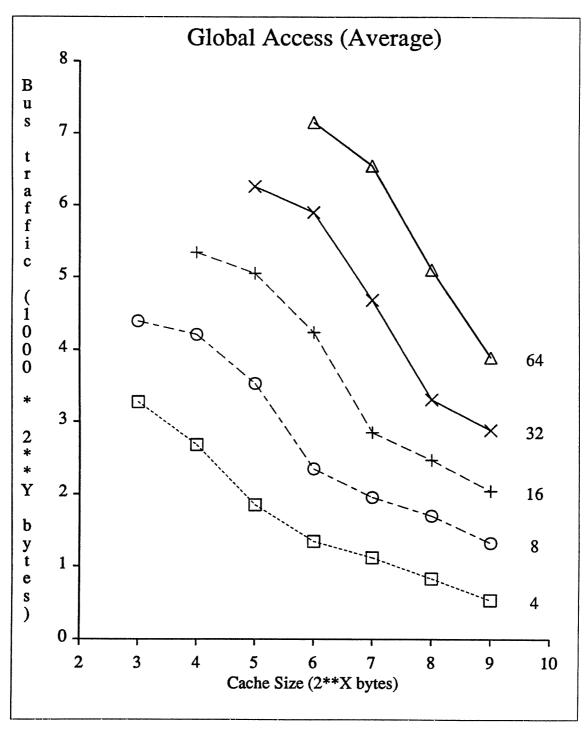

| Figure 2.3 Cache Simulations for Global Accesses (Bus Traffic)   | 16  |

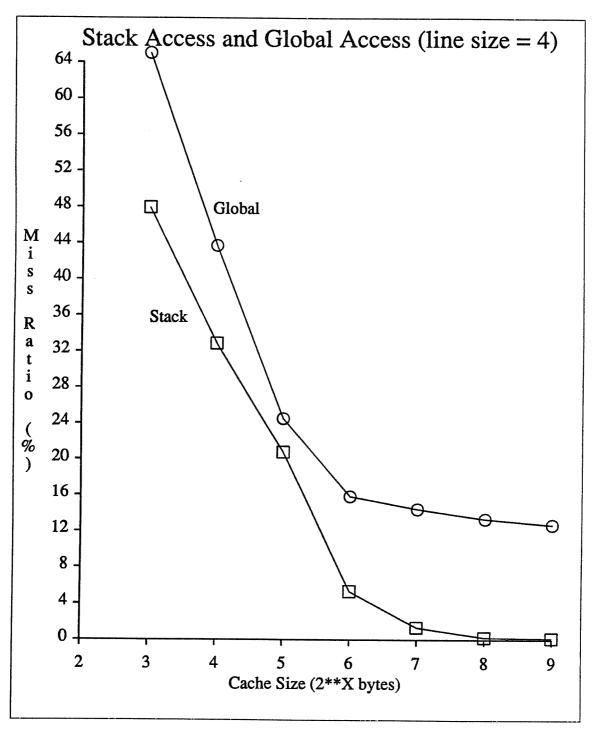

| Figure 2.4 Compare Global Accesses to Stack Accesses             | 17  |

| Figure 3.1 WDAG for Optimal Register Allocation                  | 34  |

| Figure 3.2 Selection between Clean and Dirty Registers           | 46  |

| Figure 3.3 Selection between Dirty-Live and Dirty-Dead Registers | 47  |

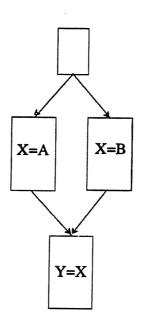

| Figure 3.4 Extension to Global Register Allocation               | 6.  |

| Figure 4.1 Unrolling A Fortran DO Loop                           | 7   |

| Figure 4.2 Loop Unrolling and Register Allocation                | 72  |

| Figure 4.3 Unrolling A WHILE Loop                                | 7:  |

| Figure 4.4 Code Replication                                      | 7   |

| Figure 4.5 Code Replication with Multi-way Branch                | 7   |

| Figure 4.6 Trace Scheduling                                      | 79  |

| Figure 4.7 Unswitching                                           | 82  |

| Figure 4.8 Multi-version                                         | 83  |

| Figure 4.9 Loops Before Loop Fusion                              | 84  |

| Figure 4.10 Loop After Loop Fusion                               | 84  |

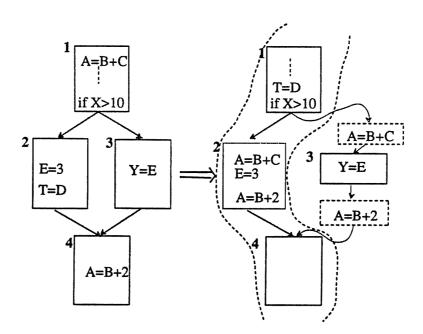

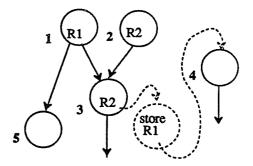

| Figure 5.1 Example Program and its Dependency DAG                | 89  |

| Figure 5.2 Prepass and Postpass Scheduling                       | 92  |

| Figure 5.3 New Dependency Edges Added by Register Allocation     | 92  |

| Figure 5.4 CSR Minimizing the Use of Registers                   | 9:  |

| Figure 5.5 Code Sequence Using Integrated Scheduling             | 9:  |

| Figure 5.6 Local Variables Make Single Assignments Non-Trivial   | 98  |

| Figure 5.7 Renaming of Local Variables                           | 98  |

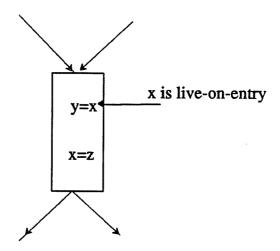

| Figure 5.8 WAR Detection for Live-On-Entry Variables             | 99  |

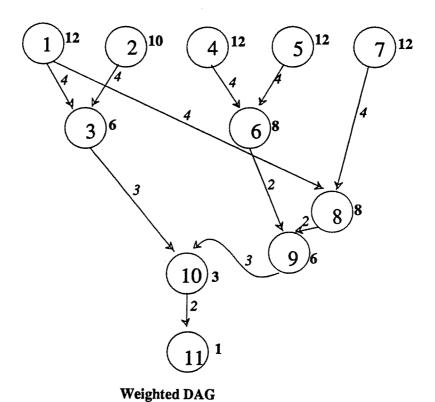

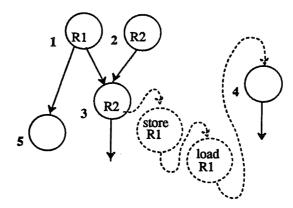

| Figure 5.9 Weighted DAG Identifying Critical Paths               | 103 |

| Figure 5.10 Comparisons of Scheduled Code Sequences              | 104 |

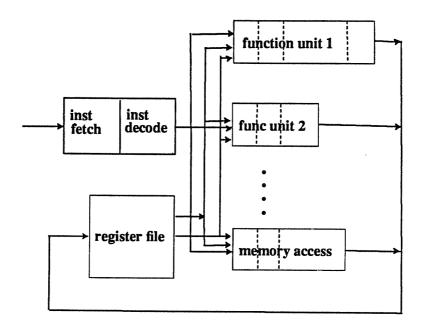

| Figure 5.11 Pinelined Implementation of Our Model Architecture   | 10  |

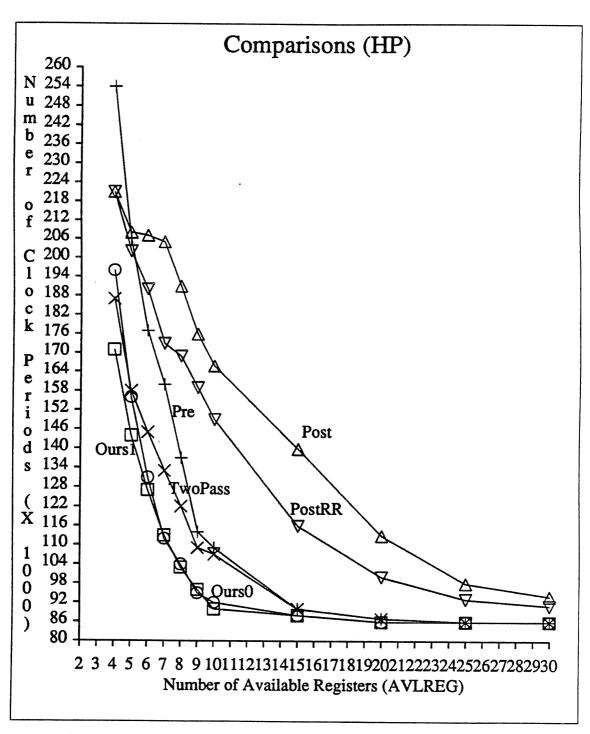

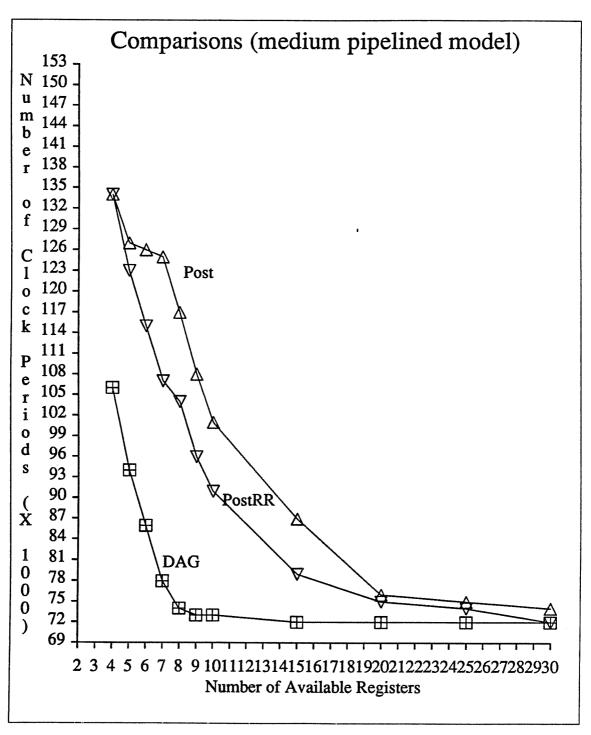

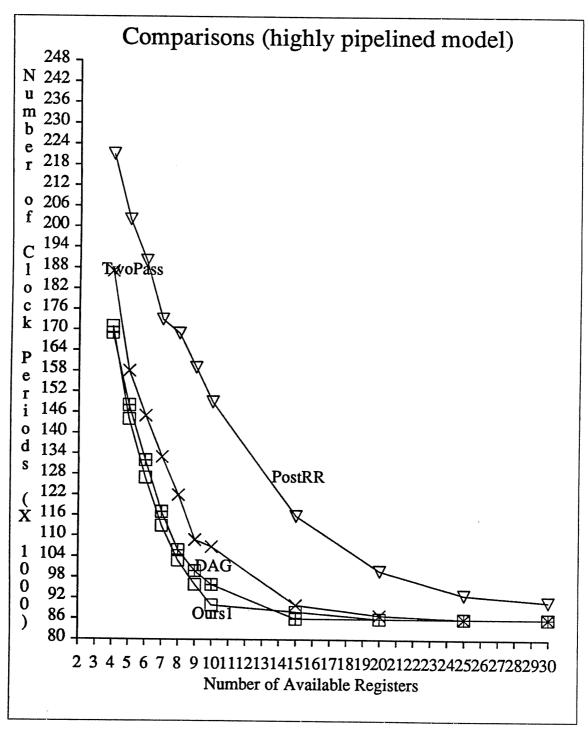

| Figure 5.12 Comparisons of Execution Cycles (Highly Pipelined Model)       |     |

|----------------------------------------------------------------------------|-----|

| •••••••••••••••••••••••••••••••••••••••                                    | 111 |

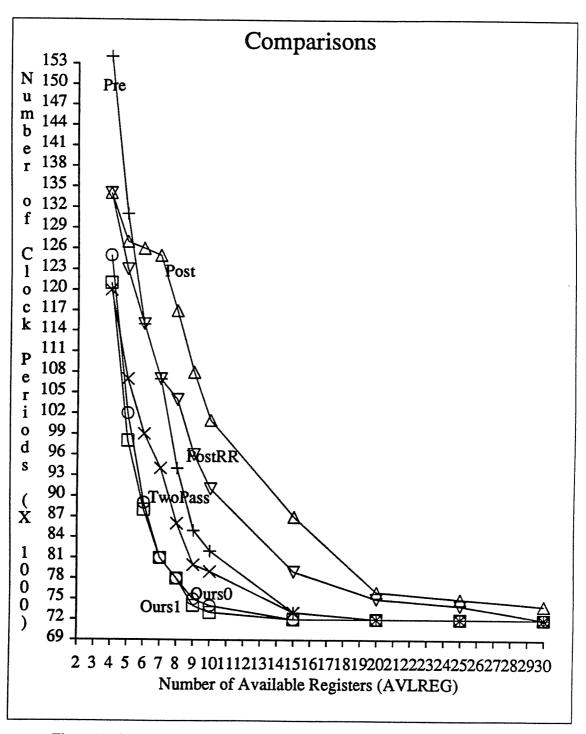

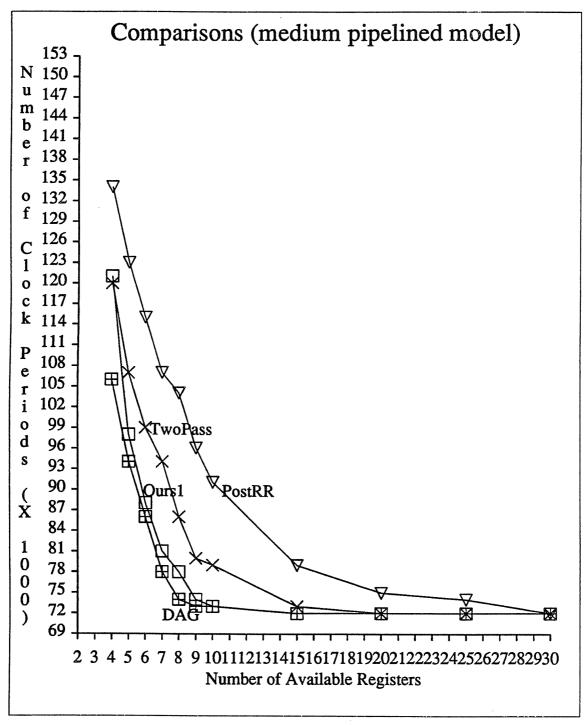

| Figure 5.13 Comparisons of Execution Cycles (Medium Pipelined Model)       |     |

|                                                                            | 112 |

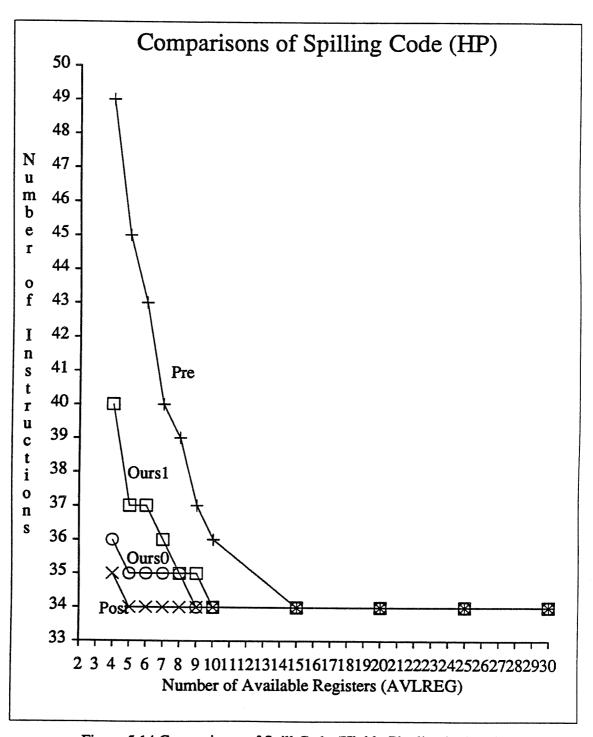

| Figure 5.14 Comparisons of Spill Code (Highly Pipelined Model)             | 113 |

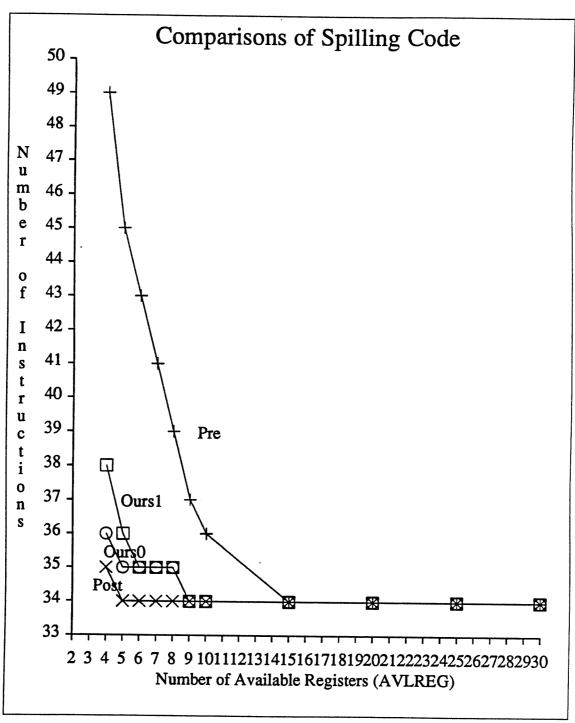

| Figure 5.15 Comparisons of Spill Code (Medium Pipelined Model)             | 114 |

| Figure 5.16 Comparisons Based on A Single Loop                             | 115 |

| Figure 5.17 One Explanation of the Anomaly in Postpass Scheduling          | 119 |

| Figure 5.18 Comparisons Using Total Number of Registers (Highly Pipe-      |     |

| lined)                                                                     | 122 |

| Figure 5.19 Comparisons Using Total Number of Registers (Medium Pipelined) | 123 |

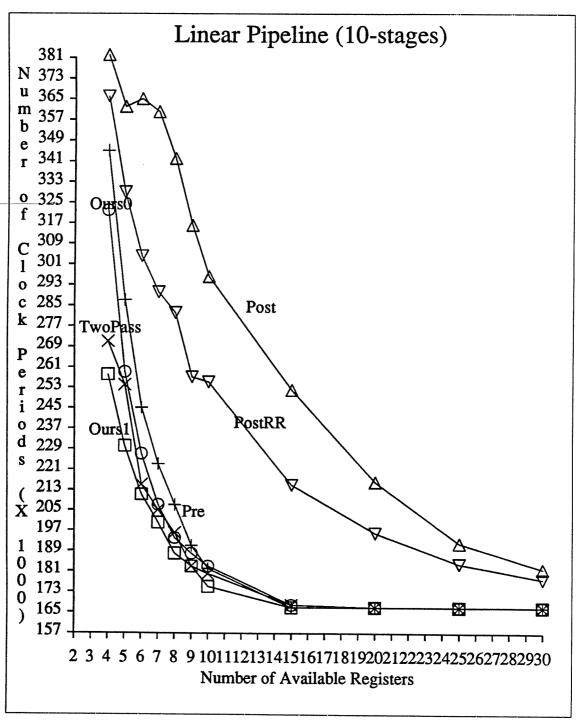

| Figure 5.20 Linear Pipelined Model (10-stages)                             | 126 |

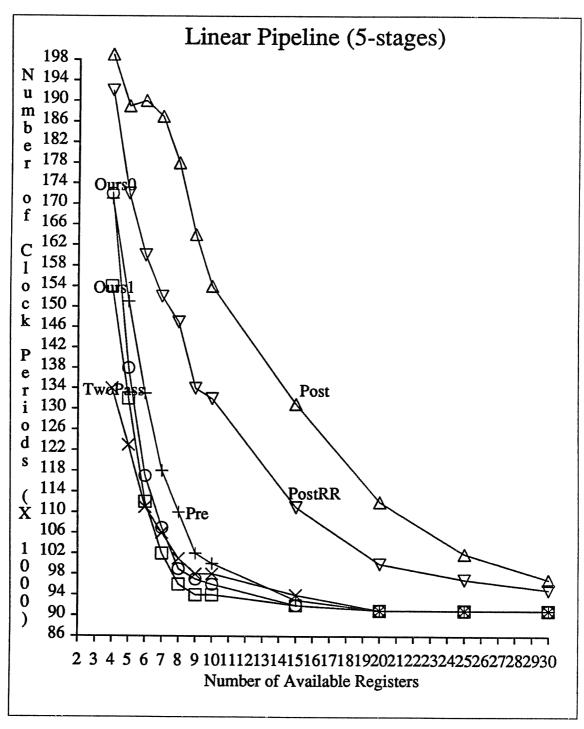

| Figure 5.21 Linear Pipelined Model (5-stages)                              | 127 |

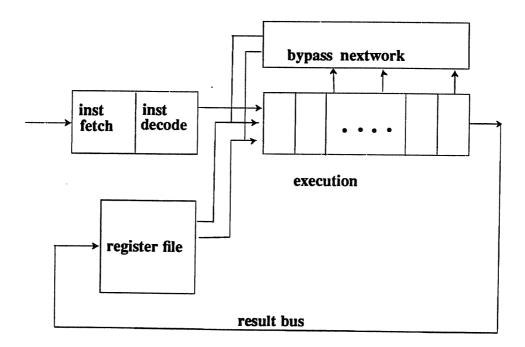

| Figure 5.22 Bypass Network                                                 | 129 |

| Figure 6.1 Free WAR Dependencies                                           | 133 |

| Figure 6.2 Computations of EIT and EFT                                     | 136 |

| Figure 6.3 Example DAG                                                     | 137 |

| Figure 6.4 Another Example DAG                                             | 138 |

| Figure 6.5 Complications due to Spilling                                   | 142 |

| Figure 6.6 WDAG with Computed EFT                                          | 145 |

| Figure 6.7 DAG-Driven Allocation vs Postpass Scheduling I                  | 152 |

| Figure 6.8 DAG-Driven Allocation vs Postpass Scheduling II                 | 153 |

| Figure 6.9 DAG-Driven Allocation vs Integrated Prepass Scheduling I        |     |

| •••••••••••••••••••••••••••••••••••••••                                    | 154 |

| Figure 6.10 DAG-Driven Allocation vs Integrated Prepass Scheduling II      |     |

|                                                                            | 155 |

# List of Tables

| Table 3.1 Rapid Growth of Register Configurations                   | 35 |

|---------------------------------------------------------------------|----|

| Table 3.2 Replacement Process of Example 1                          | 49 |

| Table 3.3 Replacement Process of Example 2                          | 50 |

| Table 3.4 Evaluation of Heuristic Register Allocation Algorithms I  | 53 |

| Table 3.5 Evaluation of Heristic Register Allocation Algorithms II  | 55 |

| Table 3.6 Bus Traffic of Perfect Register Allocation and Data Cache | 58 |

#### Chapter 1

#### Introduction

#### 1.1. On-Chip Memory

Advances in semiconductor technology have made it possible to design and fabricate an extremely high-performance CPU on a single chip. It will soon be possible to fabricate a single chip containing more transistors than the CPU of a modern supercomputer. However, the performance of these single-chip processors will be severely limited by the memory systems. This is because off-chip memory access is slow and, more importantly, the *pin bandwidth*— the rate at which data can be moved through the pins of the chip — is limited.

Many recent innovations in single-chip processors involve ways to bypass this rigid constraint on memory/processor interaction, primarily by introducing additional memory in one form or another on the processor chip. The on-chip memory can be accessed much faster than off-chip memory, and can supply a bandwidth as high as necessary. Unfortunately, the on-chip memory cannot be as large as needed for high-performance computers. In fact, the memory necessary to support a single-chip, high-performance processor will require many chips for the foreseeable future. So the on-chip memory can only be thought of as the top of the memory hierarchy.

A memory hierarchy is effective because of two kinds of locality of memory references: spatial and temporal. Spatial locality refers to the property that memory accesses over a short period of time tend to be clustered in space. Temporal locality refers to the property that references to a given location tend to be clustered in time. Using spatial locality is very effective in increasing the hit ratio of a memory hierarchy.

However, techniques for exploiting spatial locality, such as prefetching or using a large transfer unit often increase the bandwidth requirement of the memory system. Due to the limited pin-bandwidth, features of the on-chip memory that exploit spatial locality must be used carefully to avoid increasing the off-chip traffic. In other words, temporal locality should be favored in designing the on-chip memory.

#### 1.2. Data Cache or Registers

Memory references can be divided into three kinds: instruction accesses, local variable accesses (i.e. the run-time stack), and global variable accesses. Since instructions exhibit temporal and spatial locality in a very consistent manner, some form of on-chip memory is clearly warranted, as suggested in several studies [SmitJ83, Moto82, Alpe83, Henn84]. The organization of such memory is also well-understood [SmitJ85].

In Chapter 2, a study of data reference behavior shows that local data accesses exhibit a very high temporal locality. This implies that local data, like instructions, is a good candidate for the on-chip memory. Global data accesses, on the other hand, rely primarily on spatial locality to achieve high hit rate. Due to the pin-bandwidth limitation, a large transfer unit may result in long latency times because the unit must be time-multiplexed over only a few pins. In addition, much of the transferred data may be useless (for example, when the stride of the array references is not one). The redundant traffic is harmful to the already limited bandwidth. One possible solution to this problem is to have a smart data cache which can correctly prefetch the needed data, thus achieving a high hit rate without increasing data traffic. However, it is hard to envision an efficient hardware prefetch algorithm which will handle intermixed

reference patterns. Even if there is such an algorithm, it may be costly to implement and may slow down the basic cache operations. Therefore, on-chip data caches for global data references are unlikely to be effective.

Unlike instruction memory, the data memory can be controlled to some extent by the programmer. For example, frequently used variables can be allocated to registers, reducing redundant address calculations and memory traffic. In addition, data can be preloaded into a register and referenced several instructions later. With a pipelined implementation, memory access operations can be overlapped with computation operations, effectively hiding the memory latency.

Ideally, this "exact prefetch" scheme which fetches exactly the data needed will always have a data "hit" without increasing off-chip data traffic. A load/store architecture (also referred to as register-oriented architecture; e.g. the Cray-1S [Cray82]) serves such a purpose. Such architectures encourages the heavy use of registers to decrease redundant memory traffic [Henn82], and are easy to pipeline [Kogg81]. Although programs for load/store architectures may be larger, which implies an increased instruction bandwidth, load/store architectures have significantly lower data memory bandwidth [Radi82, Henn84]. Lower data memory bandwidth is highly desirable since data access is less predictable than instruction access. Thus, it can be advantageous to trade increased instruction bandwidth for decreased data bandwidth. Load/store architectures have been adopted in some recent high-performance VLSI architectures [Henn84, Patt85, Radi82, Good85, Birn86, Neff86].

The use of a set of registers has additional advantages: (1) it outperforms a data cache by nearly a factor of two in both speed and cost [Ditz82]; (2) it potentially can use better replacement algorithms with information available at compile time to

allocate and purge data more effectively than a data cache; (3) registers make the coherency problem for multiple processors easier to deal with — registers should perhaps be thought of as local memory. The major problem with the use of a set of registers is that static (compile-time) binding may perform poorly when most of the information for management cannot be obtained until run-time. For example, memory aliasing and conditional branching often force compilers to perform conservative allocation and scheduling, decreasing the efficiency of the static management. However, improvements in compiler technology (i.e. anti-alias [Nico85,Coop84,CoutB86] and software branch prediction [Fish81]) enable compilers to perform efficient allocation and scheduling for certain applications, notably scientific computations. For applications which make static binding more difficult, a data cache may be a better candidate, since the cache is better adapted to dynamic program behavior.

The other argument which favors data caches is that data caches are architecture-independent — they can be used to improve system performance without affecting programs. This is a more compelling argument for implementations of architectures defined before the availability of cache. In order to increase performance, many newer computers make the cache visible. For example, the IBM 801 [Radi81] and the HP Spectrum [Birn86] have instructions to allocate and free cache lines. Also, system programmers make the control program share the same stack with user programs to increase the cache hit ratio [Radi82]. Therefore, data caches are no longer transparent to programmers in some high-performance architectures. Although a visible cache can be more effective through the use of cache hints, we believe the effort necessary to provide effective hints to the cache is comparable to the effort necessary to allocate

registers effectively.

#### 1.3. Research Problems

Load/store architectures simplify code generation in some aspects, but they need more optimizations to realize the full advantage of the architecture features [Birn86]. Two compiler optimization techniques, register allocation and code scheduling, are crucial to the effectiveness of a load/store architecture.

#### 1.3.1. Register Allocation

Register allocation is a difficult but important function of an optimizing compiler. In the literature, the phrase "register allocation" has been used to describe two phases in a compilation: (1) register allocation, which refers to the decision of what names in a program should reside in registers; and (2) register assignment, which refers to the association of preallocated symbolic registers with real registers. Since the register file is the top of the memory hierarchy, it should be small and must be used efficiently. In this thesis, we are primarily dealing with the register assignment problem.

Local allocation refers to the assignment of registers over an entire block of straight-line code. An early exposition of this problem appears in the description of the Fortran I compiler [Back54, Cock70]. Horwitz et al. [Horw66] published a paper on this subject, giving an optimal algorithm for index register allocations. Kennedy [Kenn72] provided a refined version of Horwitz's algorithm. Freiburghouse [Frei74] proposed the "usage count" algorithm, compared it to some other heuristic algorithms, and concluded "usage count" is efficient for local allocation. His paper assumed the memory always keeps a correct copy of the contents in registers, therefore, Belady's

algorithm [Bela66] is optimal in his case. Fischer [Fisc87] gave an allocation algorithm that favors replacing clean registers to reduce the number of necessary store instructions. Although Horwitz's and Belady's algorithm are known to be optimal in local register assignment, they are inadequate for general purpose register allocations. Detailed explanations will be given in Chapter 3. A model for finding an optimal assignment, which generates a minimal number of loads and stores for spilling, has been established in Chapter 3. Rules for speeding up the computation have been provided.

Global allocation refers to the assignment of registers over a portion of the program that includes branches or high-level control constructs. A simple solution, known as "reference count" [Aho86], identifies frequently used data items (statically) and allocates them to registers over a portion of program (e.g. a loop), has been used in Fortran H compiler [Lowr69] and a Modula II compiler [Powe84]. More sophisticated approaches [Day70, Beat74, Kim78, Wulf75, Leve81] try to allocate more variables to registers by assigning a register to several variables which have disjoint lifetimes. Approaches [Chai81, Chow84] based on graph coloring model have claimed to be effective and elegant for global register allocation. However, instruction traces from IBM 801 and MIPS, which applied graph coloring allocation in their optimizing compilers, showed that there are still many load/store instructions compared to the trace from RISC [Patt85]. This is probably due to the increased cost of procedure calls: the more registers allocated, the more loads and stores needed for procedure calls to save and restore them. Wall [Wall86] proposed delaying register allocation until link time so that simultaneously live procedures will be allocated different sets of registers to avoid register saving and restoring. Two mutually exclusive procedures can share the

same set of registers. This is similar to a procedure-level graph coloring approach. Wall used 52 registers to perform the link time allocation. In Chapter 2, we study a model of "perfect" register allocation. Assuming all procedures are in-line expanded, all loops are fully unrolled, and all branches are correctly predicted, we would like to know how many registers can be effectively allocated. The effective number found is about 32, much smaller than the number in the RISC microprocessor, which is 138. The key point of effectively using a small number of registers is judicious spilling, a weak point of graph coloring allocation. We discuss the issue of register spilling in Chapter 2 and 3.

#### 1.3.2. Code Scheduling

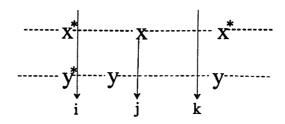

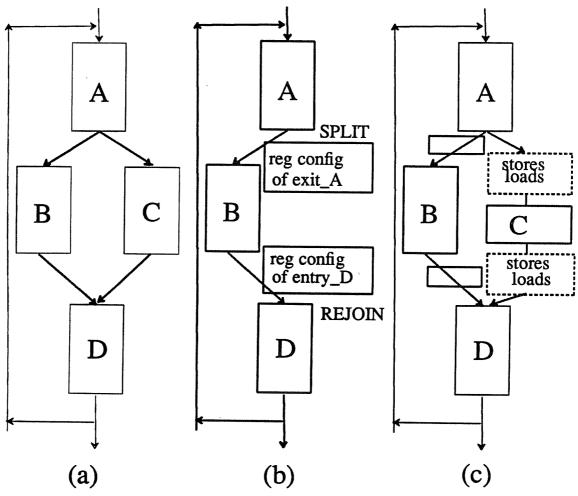

Code scheduling creates a semantically equivalent code sequence that has more overlapped operations and less wait time in a pipelined execution. It effectively hides latency of memory and functional units. Hiding latency has the effect of reducing pipeline interlocks. Code scheduling can be performed by hardware during execution, using dynamic code scheduling [Wiss84], or by the compiler at compile time, using static code scheduling. Dynamic code scheduling has been used in CDC 6600 and IBM 360/91. Due to its expense and its complexity, which may slow down the basic clock period, dynamic code scheduling has not been widely applied today. Research on static code scheduling includes [Arya85, Ausl82, Henn83, Youn85, Gibb86, Site78]. Arya formulates code scheduling as an integer programming problem [Arya85]. Auslander [Ausl82] describes code scheduling before register allocation (Prepass), while the others [Henn83, Gibb86, Site78] are concerned with scheduling after code generation and register allocation (Postpass). Prepass scheduling may introduce extra register

spilling since code scheduling lengthens pseudo-register lifetimes, increasing the number of simultaneously live registers. Postpass scheduling, on the other hand, may suffer from more restricted parallelism due to improper allocation of registers. This interdependence between register allocation and code scheduling has been studied in Chapter 5. Two solutions have been proposed and tested in Chapter 5 and 6.

#### 1.3.3. Large Basic Blocks

Typically, basic blocks are small. For small basic blocks, performance differences between spilling algorithms are minuscule, and the interdependency problem is almost negligible. However, small basic blocks offer limited parallelism. Without sufficient parallelism, the latency of the memory or the function units cannot be hidden since there are not enough independent instructions to be executed while one instruction is waiting. With the increasing emphasis on parallel processing, especially on instruction level parallelism, researchers are looking for ways to obtain large basic blocks.

Usually, the smaller a unit (e.g., a procedure, a basic block), the higher the overhead for unit transitions. For example, the procedure call overhead (saving and restoring registers) is proportionately higher for small procedures. Branches are relatively more expensive for small basic blocks in pipelined processors. Furthermore, small basic blocks often require more load/store instructions: Temporaries which reside in registers and are live on exit are stored to memory and reloaded when referenced in some later basic block. With large basic blocks, many such redundant loads and stores can be avoided.

Fifteen years ago, when saving memory space was the major concern, most optimizing compilers produced code that was as small as possible. Since small program

units permit more code sharing, they were favored. For example, the BLISS/11 optimizing compiler [Wulf75] tried to detect groups of similar expressions and replace them by a single subroutine. With decreasing memory cost and rapidly increased main memory size [Pohm83], static code size is not as important as before in determining system performance. In Chapter 4, techniques for generating large basic blocks are discussed. Those techniques that increase static code size but not dynamic code size are favored. In order to support pipeline/parallel processing, future optimizing techniques may favor large basic blocks, increasing the importance of this research.

#### Chapter 2

# On the Use of Registers vs Data Cache to Minimize Memory Traffic

# 2.1. The Behavior of Local Accesses and Global Accesses

Recent research papers [e.g. Patt82, Hase85] have examined the use of on-chip memory to reduce local data accesses from off-chip memory. In order to understand how the on-chip memory could be used more effectively to reduce off-chip communications, we conducted an experiment to study the behavior of local data accesses and global data accesses.

To investigate data access locality, we used a trace-driven cache simulator. We generated and used five different traces for a VAX-11<sup>1</sup> architecture running UNIX<sup>2</sup> version 4.2BSD:

- SORT The standard UNIX sorting program sorting the first 1000 entries in the online dictionary.

- GREP The UNIX string matching program, searching through the dictionary for a string.

#### **COMPACT**

A program using an on-line algorithm which compresses files using an adaptive Huffman code.

- CACHE A cache simulator program simulating a fully associative, write-through cache.

- AS The standard UNIX (VAX-11) assembler translating an assembly program jmalloc.s.

<sup>&</sup>lt;sup>1</sup> VAX is a trademark of Digital Equipment Company.

<sup>&</sup>lt;sup>2</sup> UNIX is a trademark of AT&T.

The traces were collected on a VAX-11 by a program using the UNIX ptrace system call, which sets the VAX trace bit to trap after each instruction. The instruction is then interpreted and memory references are recorded. Thus the trace represents a single process executing without interruption. This is unrealistic in a time-sharing environment where frequent interruptions occur for task-switching and terminal handling. It is reasonable here because we are studying the locality characteristics of local and global accesses, not the effectiveness of a cache, which is profoundly affected by task switches. As we mentioned in the previous section, we are only interested in data caches. Therefore, the traces we used here include only data fetches and stores. In addition, the traces are split into two independent streams — global data accesses and stack accesses. Since some local variables may be allocated in registers rather than the stack by the standard C compiler (because of the use of register "hints" in C), we removed all register hint declarations from the source programs to force all local variables to be allocated in the stack.

Two cache parameters, total cache size and line size, were varied in this experiment. The other parameters we used were: fully associative placement algorithm, write-back policy, LRU replacement algorithm, four byte bus width, and write allocation policy (fetch-on-write [Smit82]) for a write miss. These parameters may be unrealistic, but are indicative of the best case. Traces are typically 100,000 instructions long so that cold start effects can be ignored.

# 2.1.1. Temporal Locality and Spatial Locality

Figure 2.1 shows that a small data cache for the stack can have a very high hit ratio by taking advantage only of temporal locality. This confirms observations of

others [Haik84]. A 128-byte cache with four-byte lines has a hit ratio as high as 98.6% on the average for stack accesses. Since the stack reuses the same storage, it has high and consistent temporal locality. An on-chip cache favors high and consistent temporal locality since a single-chip processor cannot have a wide bus due to the pin limitation.

In Figure 2.2, which is for global accesses, the miss ratio for larger line size is higher when the cache is small and is lower when the cache is large. When the cache size is fixed, a small line size means that there are more lines in the cache; that is, the cache can exploit more temporal locality. A large line size means that there are fewer lines in the cache, so that temporal locality is sacrificed for spatial locality. One interesting observation in this figure is that all the knee points occur when the cache has eight lines. Beyond the knee points, increasing the cache size has little effect on hit ratio. This implies that for global accesses, there are a few "hot spots" which contribute largely to the observed temporal locality. When the cache is small and the line is large, the number of lines in the cache is not large enough to catch all the "hot spots". Therefore the miss ratio is much higher than the cache with the same size but smaller lines. This is also known as "cache pollution" [Smit82].

According to Figure 2.2, it is possible to have a small data cache (smaller than 2K) with high hit ratio (over 95%) for global accesses. However, the cache must use large lines to exploit spatial locality to get the high hit ratio. From Figure 2.3, we learn that doubling the line size often doubles the bus traffic. Since the pin-bandwidth is limited, a large line size is undesirable for an on-chip cache.

Figure 2.1 Cache Simulations for Stack Accesses

Figure 2.2 Cache Simulations for Global Accesses

Figure 2.3 Cache Simulations for Global Accesses (Bus Traffic)

Figure 2.4 Comparison of Global Accesses to Stack Accesses

#### 2.1.2. On-chip Memory for the Stack

We have found that an on-chip data cache for the stack can be very effective. Other on-chip memory structures are also possible for the stack. For example, the register stack and the Top-of-Stack (TOS) approaches. The register stack approach organizes an on-chip register file as a stack of register sets, allocated dynamically on a per procedure basis. This feature encourages compilers to allocate as many local variables as possible to the registers. Since each procedure call allocates a new register set, there are no memory accesses required to save/restore registers until the register stack overflows. It has been used by a wide range of machines (e.g. RISC I, C/70, Pyramid). The TOS approach automatically keeps the top of the stack in a high speed buffer. It has been exploited in the Symbolics 3600 machine. The C machine [Ditz82, Ditz87] demonstrates an elegant combination of the above two approaches. It works as a register stack with variable set size and preserves the semantics of the stack. Another interesting variation can be found in the Dragon computer [McCr84].

It is interesting to note the similarities between the "stack cache" and a data cache. The stack cache uses the LRU algorithm for replacement. Its (variable) line size is a stack frame. Only two address tags are required in the stack cache — the highest and the lowest address (MSP and SP) of data in the register stack. The stack cache has the advantage that replacements caused by pop up underflows (when a catch is executed) do not require the replaced frame to be flushed out to memory, since the frame is dead. Nevertheless, the stack cache is more restrictive than a conventional cache since it can only hold TOS variables. Non-TOS variables are likely to be active as well because procedures may pass their local variables as by-reference parameters to other procedures, though the compiler can allocate space for such variables on TOS if making

a redundant copy is allowed.

The stack cache (also a register stack) uses a relatively large line size — a frame. As we have discussed in the previous section, when a cache uses a large line size, it requires a larger size to capture the same number of active lines due to temporal locality. This explains why a register stack typically needs more entries. For example, equating four bytes of cache memory to one register, we found that 32 or 64 registers (i.e., 128 or 256 bytes of cache memory) yielded 98.6% and 99.7% hit ratios respectively. Though it is possible to achieve such high hit ratios using 32 or 64 registers, RISC I uses 128 and the C/70 uses 1024 registers. Then why does the stack cache in CRISP have only 32 cache registers? This is because the CRISP optimizing compiler [Band87] performs stack compression to minimize the frame size (line size). We note that the top of the memory hierarchy should be very fast. The basic cycle time of the machine may well be constrained by register access, which is a function of the register file size [Henn84, Ditz86]<sup>3</sup>.

We feel that using small lines to exploit temporal locality is especially important for on-chip memory. Not only does it produce less bus traffic, but its fine granularity allows small storage to capture temporal locality more effectively (the samller the line, the more lines can be kept in the cache). For example, if only half of the variables in a procedure are active during a call (the other half may be used for error handling or in a path which is not executed during this call), it is wasteful to keep the whole frame on the cache. It may be argued that a high hit rate is also important to minimize the effect

<sup>&</sup>lt;sup>3</sup> Ditzel reports that doubling the number of registers increases the basic clock cycle by roughly 30%.

of memory latency. However, if the small storage is a register file, then the latency can be overlapped with instruction execution in a pipelined processor by separating operand load from operand use, a common technique in supercomputers.

In order to use a small storage as effectively as a data cache for the stack without paying the cost of space overhead (e.g. address tags) and time overhead, we studied the use of a register file, managing it as a nearly perfect cache at compile time. Radin said [Radi82]:

All the registers which the CPU can afford to build in hardware should be *directly* and *simultaneously* addressable. Stack machines, machines that hide some of the registers to improve Call performance, and multiple-interrupt-level machines all seem to make poorer use of the available registers.

There are similarities between the function of register allocation and the function of a cache. For example, in register allocation, the placement algorithm is essentially fully associative, the line size is a register, the replacement algorithm might be Belady's MIN [Bela66], the write policy is write-back, and so on. The compiler has the advantage of better algorithms, but the disadvantage that it lacks run-time information. If necessary, compilers can use profiling information collected from previous runs to optimize the code generation, as has been proposed in the Bulldog compiler [Elli85] as well as the Fortran I compiler [Back57]. In addition, using registers has the potential to reduce more memory traffic than using a data cache. Two examples will serve to illustrate this: (1) When a new activation record is pushed and the first local variable is initialized, a write miss might occur. If write allocation is used, a whole line will be fetched. Because this is a new activation record, all old values in the fetched line are useless, resulting in unnecessary fetches. Radin points this out as a motivation for cache hints. (2) When replacing a dirty line, a write operation is required. However, if

the dirty value will never be used again, then the write operation is not necessary. Caches cannot identify those "dead" lines while a compiler usually can. Note that even cache hints will not work in this case unless an entire block is dead. In register allocation, when a register is replaced, if the variable currently in the register is dead, no store instruction is needed.

One obvious question is how to deal with the register saving/restoring overhead across a procedure call. We will discuss this question in detail in the next section.

# 2.2. Register Allocation and Procedure Calls

An elegant method of register allocation has been developed by G. Chaitin, primarily for the PL.8 compiler in the IBM 801 project [Chai81, Ausl82, Radi82]. In this approach, the problem is formulated as a graph coloring problem: Each node in the graph stands for a computed quantity or a local variable that resides in a machine register, and two nodes are connected by an edge if the quantities are simultaneously live. The goal is to assign different colors (registers) to connected nodes. When the compiler cannot color the graph with a number of colors equal to the number of available registers, it must add code to store and reload register contents to and from storage. The implementation showed that a fast heuristic method for assigning colors to these particular graphs generally resulted in a very good assignment. A later algorithm (developed at Stanford and used in the MIPS project) is based on a similar model, supplemented with an enhanced spilling algorithm [Chow84]. Both graph coloring algorithms claim to work very well: rarely is there a need for code spilling [Radin82, Chow84]. However, Patterson has claimed:

About 30 percent of the 801 instructions are LOAD or STORE when large programs are run; the MIPS has 16 registers compared to 32 for the 801, about 35 percent of

them [sic] being LOAD or STORE instructions. For the Berkeley RISC machines, this percentage drops to about 15 percent, including the LOADs and STOREs used to save and restore registers when the register-window buffer overflows. [Patt85]

If the graph coloring algorithm requires little code spilling, why is the number of loads and stores so high? Apparently because of procedure calls.

Normally, register allocation is done only within a procedure. If more registers are used in a procedure, then the opening cost of the procedure is higher: More stores/loads are required to save/restore those registers when a procedure call or return is executed. The observation that register allocation increases the cost of procedure calls has been reported several times [e.g. Ditz82, Henn84]. Because of the register saving/restoring overhead, procedure calls become the most costly source language statement [Patt82]. Multiple register sets have been adopted in architectures such as RISC I, Pyramid [Raga83] to speed up procedure calls. Though the approach of multiple register sets is effective for eliminating the load/store overhead on procedure calls, this technique introduces new problems: the large number of registers may slow down the basic cycle time, consume a large area of silicon, and increase process switching time.

#### Again quoting Patterson,

If compiler technology can reduce the number of LOADs and STOREs to the extent that register windows can, an optimizing compiler will be clearly superior to a multiple register window scheme [Patt85].

We are therefore interested in knowing if compiler technology can achieve a more effective use of the chip area than that of a more complex architectural scheme.

Modern compilers use procedure integration, or *in-line expansion* to reduce the procedure call overhead [Alle80, Ausl82, Chow83, Macl84]. Procedure integration is a

good program optimization technique though it may increase program size. It can reduce procedure calls, create larger basic blocks, remove parameter passing overhead. remove dead code and perform some computation at compile time through constant propagation, and allow better global optimizations [Alle72, Alle80, Sche77, Mac184, Ball79]. The experimentation with complex instructions in the 70s was an attempt to introduce the notion of an assembly language-level procedure corresponding to a highlevel language statement. The recent interest in simple instructions [Radi82, Henn84, Patt85] is in part motivated by the observation that in-line expansion of these procedures (i.e., compiling a program down to the micro-instruction level) reduces the number of steps in the execution of the program. Although in-line expansion increases the code space if procedures are called more than once (statically), it usually increases only the static code size, not the dynamic memory bandwidth (the latter is especially important for designing VLSI processors with instruction caches). In addition, modern programming practice encourages the use of many small procedures, many of which may be called from exactly one place. If most of the procedures in a program are just called once in the text, in-line expansion will decrease rather than increase the code space [Sche77]. When an on-chip instruction cache is used, in-line expansion must be done more carefully, since a procedure that is called more than once in a loop may overflow the cache after expansion. This suggests a judicious in-line expander which takes the size of the instruction buffer into account.

Procedure integration can reduce the number of procedure calls, but it cannot remove register saving/restoring overhead entirely. In-line expansion creates many more local variables in the calling procedure, and increases the degree of their interference. More registers are required to color the more complex interference graph.

When compilers run out of registers, they must resort to register spilling. Therefore, rather than eliminating register saving/restoring overhead, the procedure integration technique may merely shift the problem from procedure calls to spilling. Alternatively, it allows a compiler to make effective use of more registers, if they are available [Radin82].

One weak point of the graph coloring algorithm is that it does not handle spilling very well. The spilling process (at compile time) is slow and may generate many more loads/stores than necessary. When the coloring algorithm is blocked, it will spill the node for which the cost of spilling is the smallest (where the cost is defined as the estimated number of references to that node). This process continues spilling, node by node, until the interference graph can be colored. This method has two drawbacks: (1) the estimated cost of each node may be misleading since, at run time, some branches are traversed more frequently than others; (2) spilling the node with least cost may not lead to the minimal number of load/stores. Sometimes, spilling a combination of two or more nodes may cause fewer loads/stores [Hsu85].

Chaitin claims spilling is not a problem, because (1) it occurs rarely; and (2) it converges quite rapidly [Chai82]. However, if we want to reduce the overhead of procedure calls by procedure integration, then many more variables will interfere with each other. The interference graph becomes more complex, which makes the spilling process slow and results in poor code. Therefore, allocation algorithms based on graph coloring will not work well with procedure integration techniques. In other words, procedure integration works by increasing use of registers until spilling occurs.

If we have a very large number of registers available, say 1024, then the performance of a spilling algorithm is perhaps not so important. However, VLSI

constraints force the most effective use of limited area. Therefore, we need a model which is amendable to efficient spilling.

# 2.3. A Model for Perfect Register Allocation

We have explained that using a set of registers may reduce bus traffic better than a data cache for the stack. In this section, a model is introduced to examine the performance of an optimal register allocation compared to a near-perfect data cache for the stack, and to study the degree of performance degradation resulting from conventional compilers. If the performance difference is insignificant, further research in this area may not be worthwhile. A load/store architecture is used and a "perfect" register allocation is defined as follows:

- (1) Every memory word can be allocated to a register.

- (2) Future memory reference information is known.

- (3) Registers can be dynamically allocated (e.g. a variable can be allocated in different registers at different iterations of a loop).

# 2.3.1. How Realistic is the Perfect Register Allocation?

There is a gap between the perfect allocation model and today's practice in compilers. With improving compiler techniques and innovative architectural features, the gap could be reduced. We discuss the gap as follows.

(1) Non-scalar variables are not easily allocated to registers. For example, arrays and strings are typically assigned to primary memory. However, with appropriate architecture support, non-scalar variables can be allocated in registers. For example, arrays can be allocated in vector registers [Cray82]. Moreover, a section

of memory can be allocated in contiguous registers, for example, Cray-1 has instructions to move blocks of data from memory to B or T registers.

Possible memory aliases—a data item can be reached through different names (or pointers)—often prevent variables from being allocated in registers. With improving anti-alias analysis techniques [Nico85, Coop84, CoutB86], this restriction will become less severe. In-line expansions can also reduce much of the alias problem caused by parameter passing.

- (2) Due to conditional branches and loop structures, only a limited amount of information concerning future references can be obtained at compile time. Nevertheless, through the use of loop unrolling, code replication, and branch prediction, the available information concerning future references can be increased.

- (3) Usually, variables are bound to registers statically. Once the instruction has been generated, the register designation cannot be changed at run time. For example, in a loop, if variable A is allocated in register 1, the instruction to reference A is bound to register 1 and can not be rebound to other registers from one iteration to another. (Notice that the model essentially assumes all loops are fully unrolled and all procedures are in-line expanded) If we unroll the loop several times, it is possible to bind the different instances of variable A with different registers.

### 2.3.2. An Initial Evaluation

To measure the performance of a "perfect" register allocation, we use a simulator which is basically a cache simulator with the following characteristics:

- (1) It is fully associative;

- (2) It uses a Write Back strategy;

- (3) The transfer unit is equal to the addressing unit, which is one word, i.e. one register; and

- (4) The replacement algorithm should be an extension to Horwitz's algorithm, which optimizes the bus traffic.

Although in the literature, Horwitz's algorithm [Horw66] was referenced as the algorithm for minimum bus traffic, it is inadequate in our case. This will be discussed in detail in the next chapter. Two important performance metrics are often used in cache simulations: miss ratio and bus traffic. It is more precise to use the bus traffic as the performance measurement in our case. However, measuring the optimal bus traffic is much harder than measuring the optimal miss ratio (as will be shown in the next section). On the other hand, the Belady's MIN algorithm, which optimizes the miss rate, is simple, and fast. Therefore, we choose it to do the initial evaluation. This is not too unreasonable, since a lower miss ratio often means less bus traffic. In the next section, after the introduction of the algorithm for optimal bus traffic and its heuristic version, we will use them to reevaluate the perfect allocation model.

The traces are the same as in the previous section. For this experiment, "perfect" register allocation can achieve only the minimal miss ratio (since MIN is used), not the minimal bus traffic. In the initial study, "perfect" register allocation results in 15% ~ 35% less bus traffic than a data cache with the same size using LRU replacement algorithm. This initial evaluation is encouraging. In the next section, we will show that much more bus traffic can be eliminated by using the algorithm that optimizes the bus

traffic.

The performance of the "perfect" register allocation is also compared to conventional compilers, the UNIX C compiler and the Modula-2 compiler [Powe84]. From the experiment, on average, there are 190,000 memory references in a trace. The "perfect" register allocation results in about 35,000 memory accesses with 8 registers. This means it can decrease the memory accesses by about 80%. The percentage is 90% with 16 registers and 92% with 32 registers. If the register "hints" were used for the most frequently used variables (only 6 registers are available for allocation in VAX-11, but we modified the assembly programs to make use of 8 registers), the UNIX C compiler can decrease the number of memory accesses by 40% for *sort* program, 53% for *grep* and 32% for *cache*. The Modula-2 compiler performs more optimizations than the UNIX C compiler. It uses registers for subexpression temporaries, loop indices, loop limit values and scalar variables. It can decrease the number of memory accesses by 50% for the *sort* program (we rewrote the *sort* program in Modula-2).

Due to inaccessibility, we have not compared to some state of the art optimizing compilers, for example, the PL.8 compiler [Ausl82], the UOPT [Chow83], and the Wall's approach for interprocedure allocation [Wall86]. Wall claims that 60% to 90% of the loads and stores of scalar variables can be removed using his link-time allocation scheme with 52 registers.

The perfect register allocation shows a great potential of using registers to effectively decrease bus traffic. This potential has not been fully utilized by the conventional compilers. As will see in the next chapter, it can perform even better by saving unnecessary stores.

### Chapter 3

### **Optimal Allocation in Basic Blocks**

In 1966, Horwitz et al. [Horw66] published a definitive paper on index register allocation in straight-line programs. Their algorithm minimizes the number of loads and stores. Later algorithms [Lucc67, Kenn72] are mainly improvements of Horwitz's. Horwitz reduces the problem of index register allocation to that of finding a "shortest path" through a WDAG (Weighted Directed Acyclic Graph). In order to prevent the WDAG from growing too rapidly, Horwitz provides rules to restrict the growth. The weights that Horwitz uses in the WDAG are based on two basic operations for index registers: Read and Modification. A modification is, basically, a read followed by a write. Since the basic operations for general purpose registers are read and write (For example, the instruction "ADD  $r_3$ ,  $r_1$ ,  $r_2$ " reads registers  $r_1$  and  $r_2$  and writes register  $r_3$ ), the rules in Horwitz's algorithm are inadequate for general purpose register allocation.

### 3.1. The Model

We modify the cost function of Horwitz's model and build a new set of rules suitable for general purpose registers. Our model is based on a load/store machine architecture.

$X = \{r_1, r_2, ..., r_M\}$  is a set of pseudo-registers. We assume that, at the allocation phase, pseudo-registers are assigned to temporaries, local variables, frequently used constants, etc. Later in the assignment phase, a register allocator maps pseudo-registers to real registers. This technique has been used widely [Leve81, Kim78, Aus182, Madh82,

Davi84, CoutA86]. A pseudo-register is an *allocated* pseudo-register if it is currently associated with one real register, otherwise it is *unallocated*. We assume that each pseudo-register has an associated memory location in which to store its content.

S = {clean, dirty} is a set of two states. The clean state means that the value of an allocated pseudo-register is consistent with the value in the pseudo-register's corresponding memory location. The dirty state means the value of an allocated pseudo-register is not consistent with its value in memory.

$Q_i = (q_i^1, q_i^2, ..., q_i^N)$  is a register configuration, where N is the number of real registers and  $q_i^j$  belongs to  $X \times S$ . We assume that in the initial configuration  $Q_0$ , each  $q_0^j$  is a pseudo-register that will never be used.

$P = \{I_1, I_2, ..., I_n\}$  is a sequential program, a sequence of pseudo-register operations. There are two operations: read and write. A pseudo-register must be allocated before the operations are applied to it. A read from an allocated pseudo-register will not change its state, while a write to it will put it in a dirty state. A program here means a sequence of pseudo-register reads and writes. The *i*th symbol of the program is called

<sup>&</sup>lt;sup>1</sup> A load instruction, which copies data from the memory to a register, by definition, is a write operation to registers. Thus, a load instruction will put the allocated pseudo-register in a dirty state. However, if the load instruction copies data from the pseudo-register's corresponding memory location to the pseudo-register, then the pseudo-register should be in a clean state. Therefore, a load from the pseudo-register's corresponding memory location to the pseudo-register is treated as a read rather than a write.

<sup>&</sup>lt;sup>2</sup> The model we have defined is not a realistic one in that it does not deal with multiple register reads and writes in a single step. However, this simplified model is useful for making good replacement decisions. Simple extensions to accommodate such complications have been made in one of our implementations.

the *i*th step. As in Horwitz's paper [Horw66], we use r to denote a read from pseudoregister r, and  $r^*$  to denote a write to r. For the register configuration, we also use r to denote that pseudo-register r is in a clean state and  $r^*$  to denote that r is in a dirty state. We can specify an example program as follows:

$$r_2^* r_1 r_2 r_3^* r_0 r_3$$

The above program is a register access trace from the following sample program segment:

$A = (Q_1,...,Q_n)$  is a register allocation for a program P (of n steps). It is a sequence of register configurations.

If the pseudo-register accessed at the *i*th step is in the (*i-1*)st configuration (*i.e.* the pseudo-register is allocated), it is said to be a *hit*. If not, it is said to be a *miss*. No loads or stores are required for a hit. A read miss requires one load to fetch data from the memory location into a real register. A write miss needs no loads. Register replacement is required for a miss. When replacing a dirty pseudo-register, one store is required to update its corresponding memory location. However, if the dirty pseudo-register is dead (*i.e.* its content will never be used again), update is not necessary.

We define two distance functions: (1) NEXTRD(i,x) returns the number of steps from step i to the first step after i that reads pseudo-register x; and (2) NEXTWR(i,x) returns the number of steps from step i to the first step after i that writes x. If no instance of the appropriate access is found, the functions return  $\infty$ . An allocated pseudo-register x is said to be DEAD at step i if: (1) NEXTRD(i-1,x)= $\infty$  (x will never

be read again) or (2) NEXTWR(i-1,x) < NEXTRD(i-1,x) (the next access of x is a write).  $Q_{i-1}$  and  $Q_i$  are either equivalent or different in only one component. Suppose that  $Q_{i-1}$  differs from  $Q_i$  in that  $q_{i-1}^j = (x,s)$  whereas  $q_i^j = (x',s')$  and  $x \neq x'$ . We define the cost of a configuration change,  $Cost(Q_{i-1},Q_i)$ , as follows:

### A) Store cost:

```

If s=clean

then cost = 0

else If s=dirty and x is DEAD

then cost = 0

else cost = 1

```

If a register is clean, no register store is needed as its value is already in the corresponding memory location. If the register is dirty and dead, there is no need to store the value; if the register is dirty and live, one store instruction is needed to update memory.

### B) Load cost:

```

If s'=clean

then cost = 1

else If s'=dirty

then cost = 0

```

The state s' is clean means this is a read miss. A read miss needs one load instruction to fetch data from memory into a register.

The state s' is dirty means this is a write miss. A write miss needs no fetch.

$Cost(Q_{i-1}, Q_i)$  is the sum of the Store cost and the Load cost.

The above cost function differs from that of Horwitz in two aspects:

- (1) In our model, a write miss does not need an additional (read) memory access. In Horwitz's model, because the basic operation for writing an index register is a modification, it does.

- (2) In our model, if the next access of a pseudo-register x is a write, the replacement of x needs no stores to update the memory. This never happens in Horwitz's model because there are no direct write operations.

With our model, index register allocation [Horw66, Kenn72] is a special case of general purpose register allocation in which a write to pseudo-register r is always preceded by a read of pseudo-register r.

The cost of a register configuration  $Q_j$  is defined as:

$$Cost(Q_j) = \sum_{i=1}^{j} Cost(Q_{i-1}, Q_i)$$

The cost of an allocation A of a program with n steps is defined as:

$$Cost(A) = \sum_{i=1}^{n} Cost(Q_{i-1}, Q_i)$$

A WDAG can be constructed as follows: For each step of the program we associate a node of the graph with each configuration that may occur at this step; the given initial configuration is the only one associated with step zero. We can then draw a branch from any node associated with the *i*th step to any node associated with the (i+1)-st step, giving this branch a weight which is the cost of getting from the first configuration to the second. The problem of minimizing Cost(A) can then be considered as finding the shortest path in this graph from the initial node to some node

associated with the last step of the program. That is, we find an register allocation A which generates minimal number of loads and stores.

### Example

Assume there are only two real registers.

The input program is:  $r_1^* r_2 r_3 r_2^* r_1$

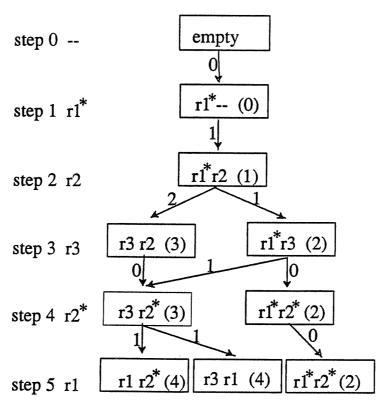

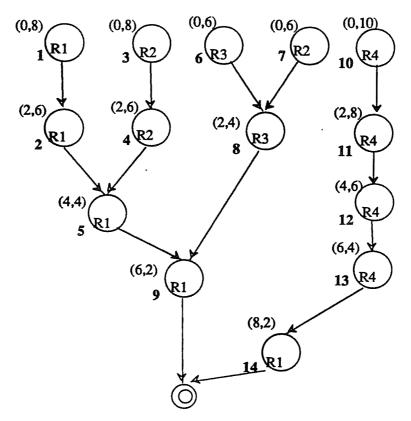

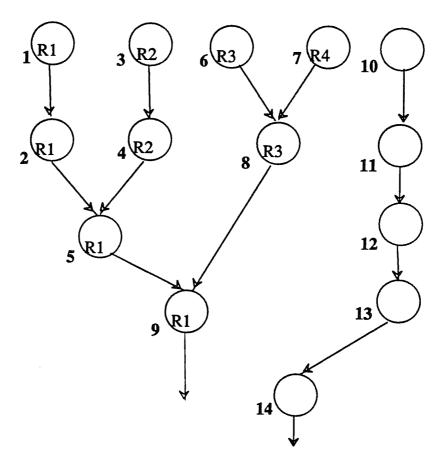

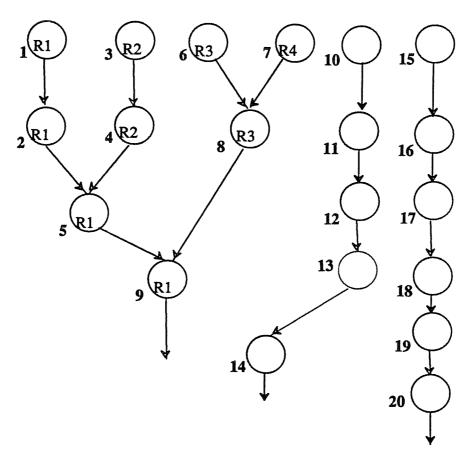

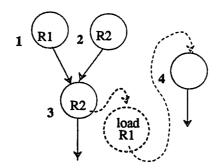

The complete WDAG is shown in Figure 3.1 (costs of allocation are shown in parentheses, costs of configuration changes are associated with edges). The optimal allocation of this example is obtained from the rightmost path with a cost of 2.

### 3.2. Finding a Shortest Path in the WDAG

The search of a shortest path in the WDAG can be conducted by the construction of a search path tree [Sedg83]. The obvious approach to finding such a shortest path (an optimal allocation) is to enumerate all possible (legal) allocations for a given program, and to pick the one with least cost. Since the number of different configurations is finite for fixed M (M is the number of pseudo-registers) and N (N is the number of real registers), the search tree will not grow exponentially proportional to n (n is the number of steps). It will be bounded by the maximal number of different configurations. However, the number of different configurations grows exponentially with N and M. In a legal allocation, the pseudo-register at the *i*th step must be in the *i*th configuration to become an allocated pseudo-register. And each allocated pseudo-register can be in a clean or a dirty state. The number of different configurations, therefore, is  $C(M-1, N-1) \times 2^N$ . From Table 3.1, which is generated from this formula,

Figure 3.1 WDAG for Optimal Register Allocation

we see that the search tree method is computationally infeasible even for moderate values of M and N. Horwitz *et al* [Horw66] provided some rules to restrict this exponential growth; we shall do likewise.

# 3.3. The Rules for Pruning the WDAG

In order to make this model computationally feasible, we define a set of rules to prune the WDAG. A configuration  $Q_i$  is partitioned into four disjoint sets as follows:

$\{x \mid x \text{ in } Q_i, \text{ NEXTRD}(i,x) < \text{NEXTWR}(i,x)\}\$  This set consists of all the variables which are clean and will be read after step i before being written.

| (M) Number of    | (N) Number of  | Number of      |

|------------------|----------------|----------------|

| Pseudo-registers | Real registers | Configurations |

| 10               | 2              | 36             |

| 10               | 4              | 1344           |

| 10               | 8              | 9216           |

| 15               | 2              | 56             |

| 15               | 4              | 5824           |

| 15               | 8              | 878592         |

| 20               | 2              | 76             |

| 20               | 4              | 15504          |

| 20               | 8              | 12899328       |

| 20               | 16             | 254017536      |

| 25               | 2              | 96             |

| 25               | 4              | 32384          |

| 25               | 8              | 88602624       |

| 25               | 16             | 85688582144    |

| 30               | 2              | 116            |

| 30               | 4              | 58464          |

| 30               | 8              | 399559680      |

| 30               | 16             | 5082890895360  |

Table 3.1 Rapid Growth of Register Configurations

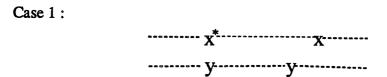

set 3 (DIRTY-DEAD set) =  $\begin{cases} x^* \mid x \text{ in } Q_i, \text{ NEXTRD}(i,x) < \text{NEXTWR}(i,x) \text{ and } x \text{ is DEAD after step} \end{cases}$ i+NEXTRD(i,x) } This is a set of pairs that exhibit the reference pattern:  $x^* \cdots x \cdots x^*$  or  $x^* \cdots x \cdots \infty$ .

set 4 (DIRTY-LIVE set) =  $\{x^* \mid x \text{ in } Q_i, \text{ NEXTRD}(i,x) < \text{NEXTWR}(i,x) \text{ and } x \text{ is not DEAD after step } i+\text{NEXTRD}(i,x) \}$  This is a set of pairs that exhibit the reference pattern  $x^* \cdots x \cdots x$ .

### Observations:

(1) Replacing an element from the DEAD set is always cheaper than replacing elements from other sets. This is obvious since the cost of replacing a dead register is 0.

(2) Among elements in the CLEAN set, replacement of the most distant one gives minimal cost. This is the Belady's MIN algorithm.

### Proof:

Suppose allocated pseudo-registers x and y in  $Q_i$ , operations  $I_j = x$ ,  $I_k = y$ , such that i < j < k, and that there is no  $x \in \{I_n \mid n=i+1, j-1\}$ , and no  $y \in \{I_n \mid n=i+1, k-1\}$ . Assume  $I_{i+1}$  is not in  $Q_i$ , and one of registers x, y will be replaced. Two possible configurations,  $Q_{i+1}^{-1}$  and  $Q_{i+1}^{-2}$ , are produced at step i+1, and they differ in exactly one element,  $x \in Q_{i+1}^{-1}$  and  $y \in Q_{i+1}^{-2}$ . Let us isolate the remaining N-1 elements from x and y so that they are replaced under the same replacement strategy. For example, if an element z is replaced from  $Q_{i+1}^{-1}$  then the z in  $Q_{i+1}^{-2}$  must be replaced too; if x is replaced from  $Q_{i+1}^{-1}$  then y must be replaced from  $Q_{i+1}^{-1}$ . At step j, there are two configurations:  $Q_{j-1}^{-1}$ , which comes from  $Q_{i+1}^{-1}$ , and  $Q_{j-1}^{-1}$  which comes from  $Q_{i+1}^{-1}$ . The cost associated with  $Q_{j-1}^{-1}$  and  $Q_{j-1}^{-1}$  are the same, because they use the same replacement strategy from step i+1 to step j-1.

At step j, there are two cases:

(A) x is in  $Q_{j-1}^1$ : this is a hit for  $Q_{j-1}^1$ .

Since there are no cost for a hit,

$$Cost(Q_j^1) = Cost(Q_{j-1}^1)$$

(1)

Because  $Q_{j-1}^2$  is originated from  $Q_{i+1}^2$  and there is no  $x \in \{I_n \mid n=i+1, j-1\}$ , x will not be in  $Q_{j-1}^2$ . This is a miss for  $Q_{j-1}^2$ . One load instruction is required to fetch x and a store cost of U (0 or 1, depending whether the replaced element, say z, is clean or dirty) for replacement.

$$Cost(Q_i^2) = Cost(Q_{i-1}^2) + 1 + U$$

(2)

(I) If the replaced element z = y:

Then U = 0 and  $Q_j^2$  has the same configuration as  $Q_j^1$ .

Because

$$\operatorname{Cost}(Q_j^2) = \operatorname{Cost}(Q_{j-1}^2) + 1$$

$$= \operatorname{Cost}(Q_{j-1}^1) + 1$$

$$= \operatorname{Cost}(Q_j^1) + 1$$

Therefore,  $Cost(Q_j^1) < Cost(Q_j^2)$ . Hence, replacing y at step i is cheaper.

(II) If the replaced element  $z \neq y$

$Q_j^1$  differs from  $Q_j^2$  in exactly one element, which is z in  $Q_j^1$  and y in  $Q_j^2$ .

Because the cost of changing configuration  $Q_j^1$  to  $Q_j^2$  is (1 + U), where 1 is the cost to fetch y and U is the cost to replace z, and

$$Cost(Q_{j}^{1}) + (1 + U)$$

=  $Cost(Q_{j-1}^{1}) + 1 + U$  from (1)

=  $Cost(Q_{j-1}^{2}) + 1 + U$

=  $Cost(Q_{j}^{2})$  from (2)

Therefore, if there exists an optimal cost path through  $Q_j^2$ , then there will be an optimal path through  $Q_j^1$ . Hence, replacing y at step i is not worse than replacing x.

(B) x is not in  $Q_{j-1}^1$ .

If x was replaced during the configuration changes from  $Q_{i+1}^1$  to  $Q_{j-1}^1$ ,

then y must have been replaced during the changes from  $Q_{i+1}^2$  to  $Q_{j-1}^2$ . Therefore,  $Q_{j-1}^1$  and  $Q_{j-1}^2$  have the same configuration. Both  $Q_{j-1}^1$  and  $Q_{j-1}^2$  have a miss at step j. By replacing the same element,  $Q_j^1$  and  $Q_j^2$  must have the same cost. Hence, replacing y at step i is not worse than replacing x.

From the above, it is clearly better to displace the variable with the greater distance. Thus we displace the one which is read farthest away.

(3) If there exists a dirty register  $x^*$  and a clean register y in  $Q_i$  such that NEXTRD(i,x) < NEXTRD(i,y) (the clean element y has distance greater than the dirty element x), then replacing y is always cheaper.

### Proof:

Suppose allocated pseudo-registers  $x^*$ , y in  $Q_i$ , operations  $I_j = x$ ,  $I_k = y$ , such that i < j < k, and that there is no  $x \in \{I_n \mid n=i+1, j-1\}$ , and no  $y \in \{I_n \mid n=i+1,k-1\}$ . Assume  $I_{i+1}$  is not in  $Q_i$ , and one of registers  $x^*$ , y will be replaced. Two possible configurations,  $Q_{i+1}^1$  and  $Q_{i+1}^2$ , are produced at step i+1, and they differ in exactly one element,  $x^* \in Q_{i+1}^1$  and  $y \in Q_{i+1}^2$ . Since one store instruction is required to update x's memory location,

$Cost(Q_{i+1}^2) = Cost(Q_{i+1}^1) + 1.$

Once again, we isolate the remaining N-1 elements from  $x^*$  and y so that they are replaced under the same replacement strategy. As described before,  $Q_{j-1}^1$  comes from  $Q_{i+1}^1$ , and  $Q_{j-1}^2$  comes from  $Q_{i+1}^2$ .

At step j, there are two cases:

(A)  $x^*$  is in  $Q_{j-1}^1$ : this is a hit for  $Q_{j-1}^1$ .

$x^*$  is in  $Q_{j-1}^1$  implies y is in  $Q_{j-1}^2$ .

Since  $Cost(Q_{i+1}^2) = Cost(Q_{i+1}^1) + 1$  and during the configuration changes, the identical elements from both configurations are replaced. Therefore,

$$Cost(Q_{j-1}^{2}) = Cost(Q_{j-1}^{1}) + 1$$

(3)

Because there are no cost associated with a hit,

$$Cost(Q_j^1) = Cost(Q_{j-1}^1)$$

(4)

Because there is a miss for  $Q_{j-1}^2$ , one load instruction is required to fetch x and a store cost of U (0 or 1) to replace an element z.

$$Cost(Q_j^2) = Cost(Q_{j-1}^2) + 1 + U$$

(5)

(I) If the replaced element z = y:

Then U = 0 and  $Q_j^2$  has the same configuration as  $Q_j^1$  except that x is dirty in  $Q_j^1$  but clean in  $Q_j^2$ . It takes one store instruction to change a dirty state to a clean state.

To make  $Q_j^1$  the same configuration as  $Q_j^2$ , one store instruction is required to change x from dirty state to clean state. Because  $Cost(Q_j^1)+1 < Cost(Q_j^2)$ , replacing y at step i is cheaper.

# (II) If the replaced element $z \neq y$

To make  $Q_j^1$  the same configuration as  $Q_j^2$ , z in  $Q_j^1$  should be

replaced by y and x in  $Q_j^{-1}$  should be changed from dirty to clean. This costs (2+U), one for fetching y, one for cleaning x, and U for replacing z.

$$Cost(Q_{j}^{1}) + (2 + U)$$

=  $Cost(Q_{j-1}^{1}) + 1 + (1 + U)$  from (4)

=  $Cost(Q_{j-1}^{2}) + 1 + U$  from (3)

=  $Cost(Q_{j}^{2})$  from (5)

Therefore, if there exists an optimal cost path through  $Q_j^2$ , then there will be an optimal path through  $Q_j^1$ . Hence, replacing y at step i is not worse than replacing x.

# (B) x is not in $Q_{j-1}^1$ .

If  $x^*$  was replaced during the configuration changes from  $Q_{i+1}^1$  to  $Q_{j-1}^1$ , then y must be replaced during the changes from  $Q_{i+1}^2$  to  $Q_{j-1}^2$ . Therefore, the cost of configuration changes from  $Q_{i+1}^1$  to  $Q_{j-1}^1$  is one higher than the cost of configuration changes from  $Q_{i+1}^2$  to  $Q_{j-1}^2$ .

$$\begin{aligned} & \operatorname{Cost}(Q_{j-1}^{\,2}) & = & \operatorname{Cost}(Q_{i+1}^{\,2}) + \sum_{k=i+2}^{j-1} \operatorname{Cost}(Q_{k-1}^{\,2}, Q_k^{\,2}) \\ & = & \operatorname{Cost}(Q_{i+1}^{\,1}) + 1 + (\sum_{k=i+2}^{j-1} \operatorname{C}(Q_{k-1}^{\,1}, Q_k^{\,1})) - 1 \\ & = & \operatorname{Cost}(Q_{i+1}^{\,1}) + \sum_{k=i+2}^{j-1} \operatorname{C}(Q_{k-1}^{\,1}, Q_k^{\,1}) \\ & = & \operatorname{Cost}(Q_{i-1}^{\,1}) \end{aligned}$$

Now,  $Q_{j-1}^1$  and  $Q_{j-1}^2$  have the same configuration and with same cost. Both  $Q_{j-1}^1$  and  $Q_{j-1}^2$  have a miss. Replacing the same element, both  $Q_j^1$  and  $Q_j^2$  have the same cost. Hence, replacing y at step i is not worse than replacing x.

From the above, it is clearly better to displace the clean variable with a greater distance.

(4) If x ∈ DIRTY-DEAD set (set 3) and y ∈ DIRTY sets (both set 3 and 4) such that NEXTRD(i,x) < NEXTRD(i,y), then replacing y is always cheaper.</p>

#### Proof:

Suppose allocated pseudo-registers  $x^*$ ,  $y^*$  in  $Q_i$ , operations  $I_j = x$ ,  $I_k = y$ , such that i < j < k, and that there is no  $x \in \{I_n \mid n=i+1, j-1\}$ , and no  $y \in \{I_n \mid n=i+1, k-1\}$ . x is DEAD after step j. Assume  $I_{i+1}$  is not in  $Q_i$ , and one of dirty registers  $x^*$ ,  $y^*$  will be replaced. Two possible configurations,  $Q_{i+1}^{-1}$  and  $Q_{i+1}^{-2}$ , are produced at step i+1, and they differ in that  $x^* \in Q_{i+1}^{-1}$  and  $y^* \in Q_{i+1}^{-2}$ . Because both  $x^*$  and  $y^*$  are dirty,  $Cost(Q_{i+1}^{-2}) = Cost(Q_{i+1}^{-1})$ . The remaining N-1 elements are separated from  $x^*$  or  $y^*$  so that they should be replaced under the same replacement strategy. As described before,  $Q_{i-1}^{-1}$  comes from  $Q_{i+1}^{-1}$ , and  $Q_{i-1}^{-2}$  comes from  $Q_{i+1}^{-2}$ .

At step j, there are two cases:

(A)  $x^*$  is in  $Q_{j-1}^1$ : this is a hit for  $Q_{j-1}^1$ .

Since  $Cost(Q_{i+1}^2) = Cost(Q_{i+1}^1)$  and the same elements are replaced during the configuration changes from  $Q_{i+1}$  to  $Q_{i-1}$ , therefore,

$$Cost(Q_{j-1}^2) = Cost(Q_{j-1}^1)$$

(6)

Because there is a hit for  $Q_{i-1}^1$ ,

$$Cost(Q_j^{-1}) = Cost(Q_{j-1}^{-1})$$

(7)

Because there is a miss for  $Q_{j-1}^2$ , one load instruction is required to fetch x and a store cost of U (0 or 1) to replace an element z.

$$Cost(Q_i^2) = Cost(Q_{i-1}^2) + 1 + U$$

(8)

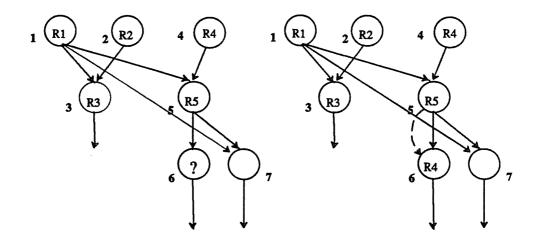

(I) If the replaced element  $z = y^*$ :