## Design of Pipelined Memory Systems for Decoupled Architectures

by

Koujuch Liou

Computer Sciences Technical Report #617

October 1985

# DESIGN OF PIPELINED MEMORY SYSTEMS FOR

# **DECOUPLED ARCHITECTURES**

by

Koujuch Liou

Computer Sciences Department University of Wisconsin-Madison Madison, Wisconsin 53706

October 1985

#### **ABSTRACT**

Design of memory systems for decoupled architectures is the theme of this dissertation. The decoupled architecture uses hardware queues to architecturally decouple memory request generation from algorithmic computation. This results in an implementation that has two separate instruction streams that communicate via hardware queues. Thus, performance is improved through parallelism and efficient memory referencing.

Techniques for increasing memory bandwidth and algorithms for servicing memory requests are incorporated into the memory system designs within these two constraints: (1) the operands placed in the hardware queue must be in the correct order, and (2) the needed operands are the only operands that can be placed in the hardware queue.

Techniques such as pipelining, interleaving, servicing requests out of arrival order, and cache memory are investigated. Two strategies for servicing memory requests are studied: (1) to service requests according to their priorities, and (2) to minimize the total request service time. For the first strategy, the priority of each request type is derived from the characteristics of memory reference and possible bottleneck during decoupled computations. The second strategy results in a request scheduling policy, *Free-Module-Request-First*, that is proven to be able to minimize the total request service time.

A sequence control scheme must be used with the Free-Module-Request-First scheduling policy in order to deliver the memory outputs to the hardware queue in the correct order. This sequence control scheme is also used to track cache hits and misses, so that a data cache can be implemented in the memory system without difficulty.

The designed data cache can not only support flexible fetch and replacement cache algorithms, it can also detect memory access hazards and short-circuit the Read-After-Write requests. Therefore, the penalty of memory access hazards can be greatly reduced.

The combination of the designed data cache and the pipelined interleaved memory system using Free-Module-Request-First scheduling policy results in a high-performance memory system, that is capable of servicing memory requests nearly no conflict delay under the particular workload defined in the trace files.

#### **ACKNOWLEDGEMENT**

Professor James R. Goodman has been an exceptional advisor to guide my graduate career with patience and wisdom. His enthusiasm to share his knowledge with me, to think seriously about my research, and to read carefully my revisions have made the final form of my thesis tighter and neater than it would have been. The constructive comments and valuable conversations of Professors Andrew R. Pleszkun and Mary K. Vernon did much to clarify many points in this thesis; I am indebted to them and to Professors Charles N. Fischer and Charles R. Kime for their efforts with my thesis.

Special thanks must also be given to the members of the PIPE research group for their assistance in the simulation study, and to the colleagues in the Academic Computing Center for their support during my graduate study. Also, I would like to thank Michael Caligiuri for his time in reading and correcting my manuscripts. Their friendship has made my stay in Madison a pleasant time.

Words are not adequate to express my deep gratefulness to my parents, my parents-in-law and my wife for their love and support. Especially my wife, Gloria, her thoughtfulness, patience and encouragement have turned many distressful moments to joyful memories.

| • |  |  |

|---|--|--|

|   |  |  |

## TABLE OF CONTENTS

| CHAPTER 1: Introduction                                         | 1  |

|-----------------------------------------------------------------|----|

| 1.1. The PIPE Architecture                                      | 3  |

| 1.2. Constraints On The Memory System                           | 8  |

| 1.3. Design Issues of the Memory System                         | 8  |

| CHAPTER 2: A Survey of High Performance Memory System Designs   |    |

|                                                                 | 11 |

| 2.1. Theory of Interleaved Memory System                        | 12 |

| 2.1.1. Memory Models without Conflict Queues                    | 14 |

| 2.1.2. Memory Models with Conflict Queues                       | 16 |

| 2.2. Methods to Reduce Memory Access Conflicts                  | 18 |

| 2.3. Memory Access Hazard and Its Resolution Schemes            | 23 |

| 2.3.1. The Storage System of the IBM SYSTEM/360 Model 91        | 24 |

| 2.3.2. Resolution of Access Hazards in the IBM SYSTEM/370 Model |    |

| 168                                                             | 32 |

| 2.3.3. Resolution of Access Hazards in the CSPI MAP-200         | 38 |

| 2.4. Summary and Discussion                                     | 41 |

| CHAPTER 3: An Analysis of Memory Reference Characteristics in   |    |

| Decoupled Computations                                          | 45 |

| 3 1 Request Types and Potential Deadlock in Request Scheduling  | 46 |

| 3.2. Some Observed Characteristics and Their Implications           |

|---------------------------------------------------------------------|

| 3.2.1. Simultaneous Memory Input Arrivals50                         |

| 3.2.1.1. Problem With More Than One Arrival Per Clock               |

| 3.2.1.2. Possible Solutions                                         |

| 3.2.1.3. Simulation Results54                                       |

| 3.2.1.4. Conclusions59                                              |

| 3.2.2. Flow Control Problems60                                      |

| 3.2.3. Shared Variables                                             |

| 3.2.3.1. Problems Resulting from Shared Variables64                 |

| 3.2.3.2. Solutions for the Shared Variable Problem66                |

| 3.2.3.2.1. Detecting Read-After-Write Hazard and Bypassing Store    |

| Data66                                                              |

| 3.2.3.2.2. Short-Circuiting Read-After-Write Request66              |

| 3.2.3.3. Analysis of Delay Due to Read-After-Write Access Hazards67 |

| 3.2.4. Simulation Results68                                         |

| 3.3. Summary and Discussion                                         |

| CHAPTER 4: Request Scheduling and Memory System Design81            |

| 4.1. Memory Request Scheduling Strategies                           |

| 4.1.1. Request Scheduling For a Single Request Type82               |

| 4.1.1.1. Theorem of Free-Module-Request-First Scheduling Policy92   |

| 4.1.2. Request Scheduling Among Request Types93                     |

| 4.1.2.1. Considerations of Separating Load and Store Requests94    |

|--------------------------------------------------------------------|

| 4.1.2.2. Priority of Instruction Fetch and Load Address Requests95 |

| 4.1.2.3. Three Steady-State Models in Decoupled Computation —96    |

| 4.1.2.3.1. Access Processor is the Bottleneck                      |

| 4.1.2.3.2. Execute Processor is the Bottleneck98                   |

| 4.1.2.3.3. Memory Controller is the Bottleneck98                   |

| 4.2. Pipelined Memory System Design99                              |

| 4.2.1. Basic Model of A Memory Controller99                        |

| 4.2.1.1. Primary Functions of Memory Controller                    |

| 4.2.1.2. Organization of Memory Operation Status Table             |

| 4.2.2. VLSI Implications and Constraints on Memory System Design   |

|                                                                    |

| 4.2.3. Memory System Design Considerations                         |

| 4.2.4. Implementation of Free-Module-Request-First Policy          |

| 4.2.4.1. Distributed Sequence Control for the Free-Module-Request- |

| First Policy                                                       |

| 4.2.4.2. Distributed Sequence Number Assignment at Input Stage113  |

| 4.2.4.3. Distributed Store Address/Data Pairing at Issue Stage115  |

| 4.2.4.4. Distributed Output Sequence Control at Output Stage       |

| 4.2.4.4.1. Interleaving the Memory Output Bus for Avoiding Delays  |

| 11'                                                                |

| 4.2.4.4.2. Handshake Signals to Allow Continuous Output Flow1       | 18           |

|---------------------------------------------------------------------|--------------|

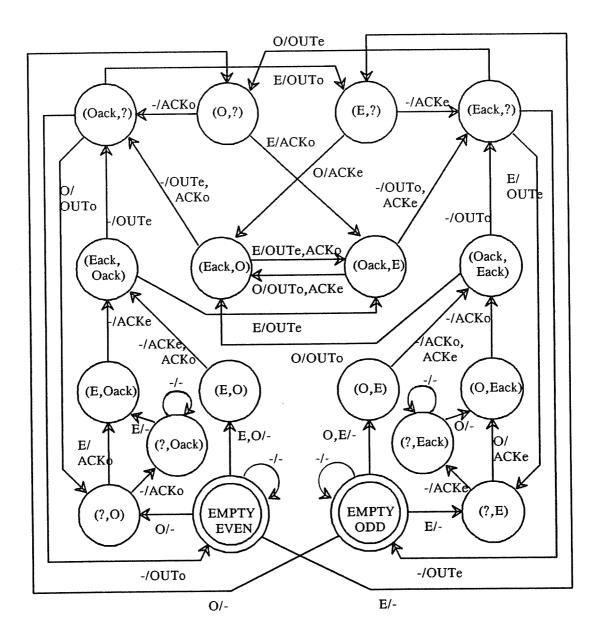

| 4.2.4.4.3. State Transition Diagram of Output Sequence Control17    | 27           |

| 4.2.4.4.4. Output Sequence Control Between Instruction and Data     |              |

| Fetches                                                             | 31           |

| 4.3. Summary and Discussion                                         | 34           |

| CHAPTER 5: Simulation and Evaluation of Memory Models1              | 37           |

| 5.1. The Simulation Model                                           | 37           |

| 5.2. Selection of Application Programs for Trace-Driven Simulations |              |

| 1                                                                   | 40           |

| 5.3. Assumptions and Parameters of Simulation Models1               | 41           |

| 5.4. A Method for Performance Evaluation1                           | .43          |

| 5.5. Performance Evaluation of Memory Models1                       | .45          |

| 5.5.1. Evaluation of Memory Models with Read-After-Write Hazards    |              |

| 1                                                                   | 48           |

| 5.5.2. Evaluation of Memory Models without Read-After-Write Ha-     |              |

| zards                                                               | l <i>5</i> 2 |

| 5.6. Summary and Discussion                                         | 155          |

| CHAPTER 6: The Design of a Data Cache                               | 158          |

| 6.1. Limitations of Data Cache in the Decoupled Architecture        | 158          |

| 6.2. Organization of the Memory Controller with Data Cache1         | 160          |

| 6.2.1. Organization of the Data Cache                               | 162          |

| 6.2.2. Selected Data Cache Algorithms                               | _163 |

|---------------------------------------------------------------------|------|

| 6.2.2.1. Servicing a Read Request                                   | _168 |

| 6.2.2.1.1. Variations of Servicing Read Requests                    | _171 |

| 6.2.2.2. Servicing a Write Request                                  | _171 |

| 6.2.3. Access Hazard Resolution and Read-After-Write Short-         |      |

| Circuiting                                                          | _174 |

| 6.2.4. First-Come-First-Serve Memory Model with Distributed Data    |      |

| Cache –                                                             | _176 |

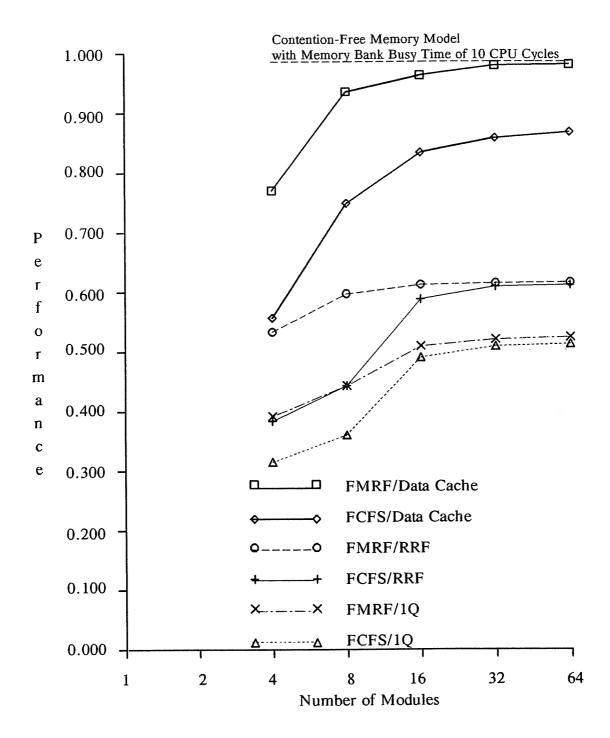

| 6.3. Performance Evaluation of the Data Cache                       | _178 |

| 6.4. Summary and Discussion                                         | _184 |

| CHAPTER 7: Summary and Conclusions                                  | _186 |

| 7.1. Summary                                                        | _186 |

| 7.2. Conclusions                                                    | _188 |

| 7.3. Contributions                                                  | _190 |

| 7.4. Further Research Plans                                         | _192 |

| REFERENCES                                                          | _193 |

| Appendix I: The First 13 Lawrence Livermore Loops                   | _198 |

| Appendix II: A Decoupled Code of LLL Loop 2                         | _206 |

| Appendix III: Simulation Results of the First 12 LLL Loops with     |      |

| Read-After-Write Access Hazards                                     | 207  |

| Appendix IV: Simulation Results of LLL Loops 4, 5, 6 and 11 without |      |

| Read-After-Write Access Hazards                                       | _220 |

|-----------------------------------------------------------------------|------|

| Appendix V: Simulation Results of Three Input Multiplexing Schemes    |      |

|                                                                       | _225 |

|                                                                       |      |

| Appendix VI: Simulation Results of Memory Model with FMRF/Data        |      |

| Cache                                                                 | _243 |

|                                                                       |      |

| Appendix VII: Simulation Results of RRF, AP-First, and EP-First Poli- |      |

| cies                                                                  | _247 |

## LIST OF FIGURES

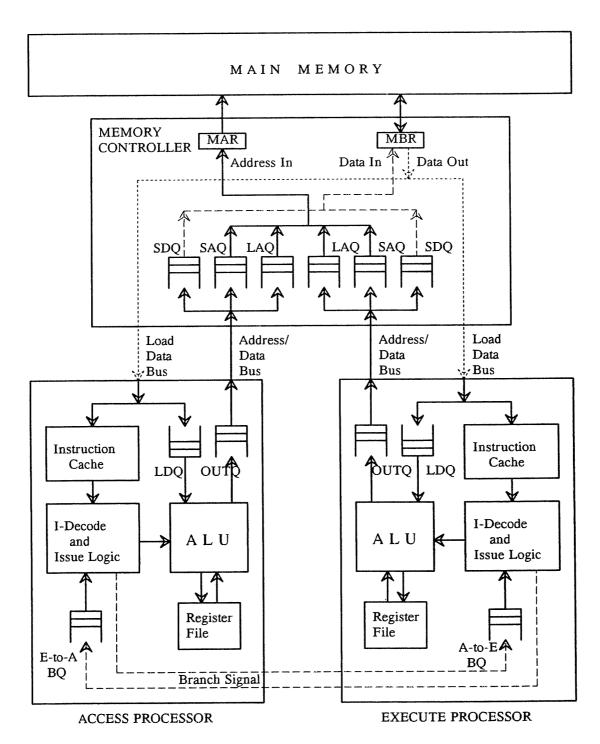

| 1.1. | Block Diagram of a PIPE Architecture                           | 5   |

|------|----------------------------------------------------------------|-----|

| 2.1. | Buffer Allocation and Function Separation within the IBM SYS-  |     |

|      | TEM/360 Model 91                                               | _26 |

| 2.2. | Block Diagram of the Main Storage Control Element of IBM SYS-  |     |

|      | TEM/360 Model 91                                               | _28 |

| 2.3. | Block Diagram of the Processor Storage Control Function of IBM |     |

|      | SYSTEM/370 Model 168                                           | _33 |

| 2.4. | Storage Addressing Flow within the PSCF of IBM SYSTEM/370      |     |

|      | Model 168                                                      | _35 |

| 2.5. | Block Diagram of MAP-200 Organization                          | _39 |

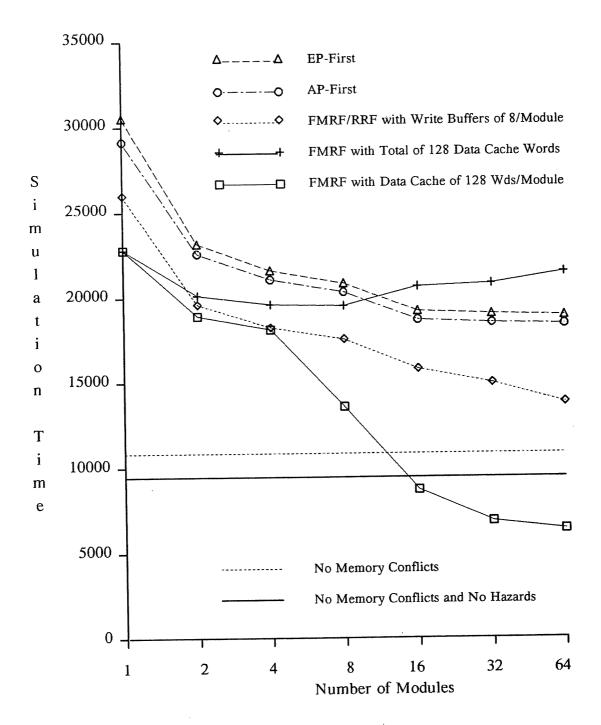

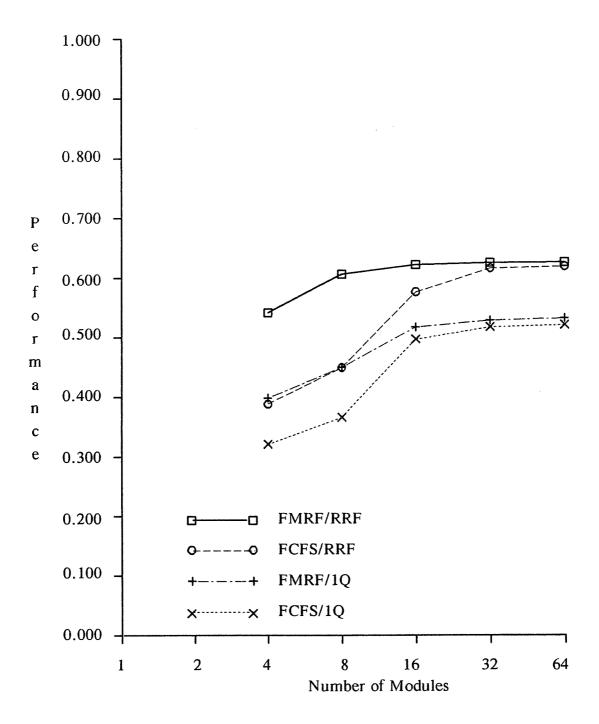

| 3.1. | Performance comparison of memory models in handling Read-      |     |

|      | After-Write hazards in LLL13 simulations                       | _72 |

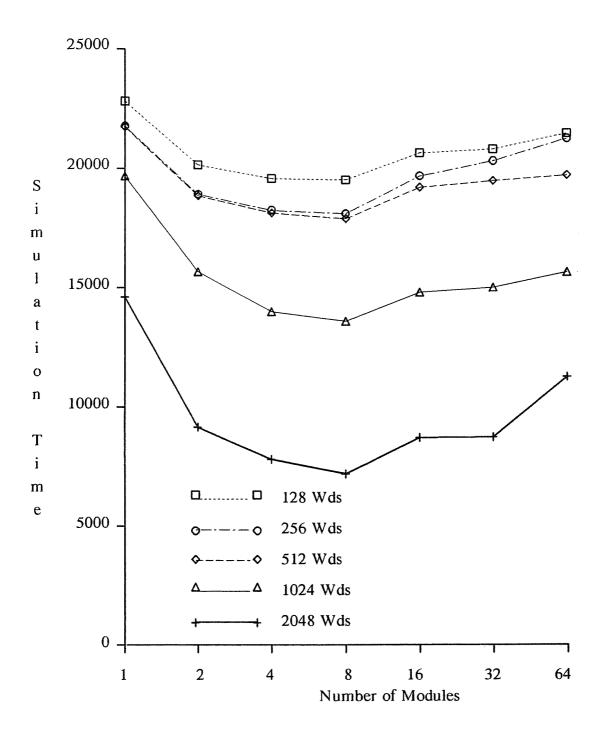

| 3.2. | Simulation Results of LLL13 with FMRF/Data Cache Policy of     |     |

|      | Different Cache Sizes                                          | 77  |

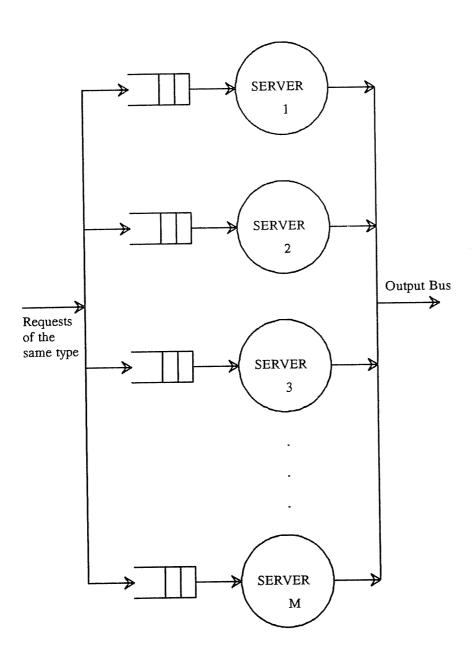

| 4.1. | A Queueing Model for Servicing Requests of the Same Type with  |     |

|      | Multiple Servers                                               | 84  |

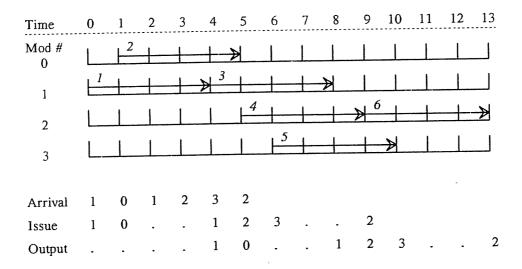

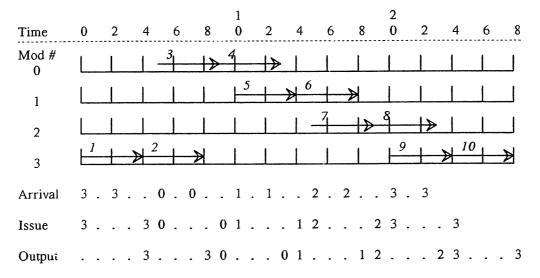

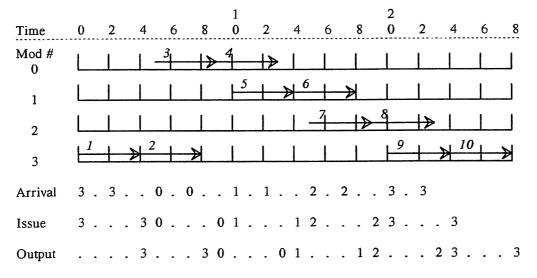

| 4.2. | Illustration of Free-Module-Request-First Scheduling Policy    | 86  |

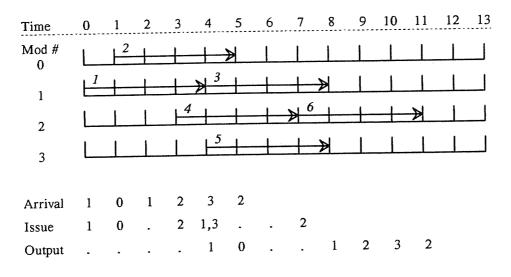

| 4.3. | Comparison of First-Come-First-Serve and Free-Module-Request-  |     |

|      | First Scheduling Policies when Memory Cycle is 6 CPU Cycles    | 89  |

| 4.4. Comparison of First-Come-First-Serve and Free-Module-Request-  |      |

|---------------------------------------------------------------------|------|

| First Scheduling Policies when Memory Cycle is 4 CPU Cycles         | _91  |

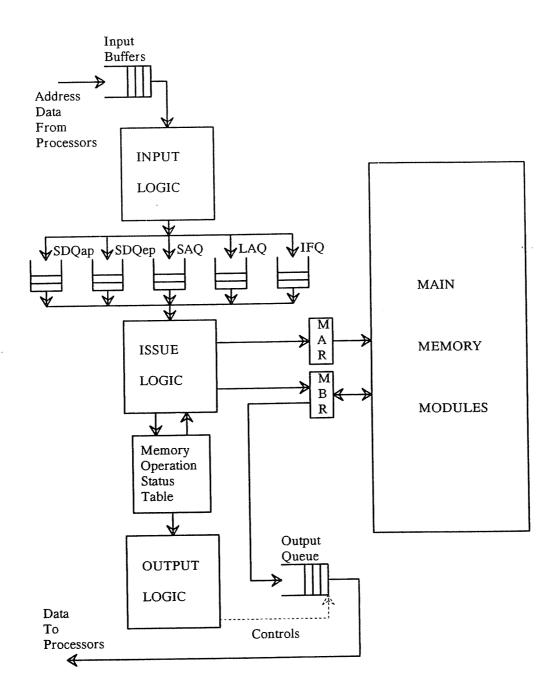

| 4.5. Basic Model of the Pipelined Memory System —                   | 100  |

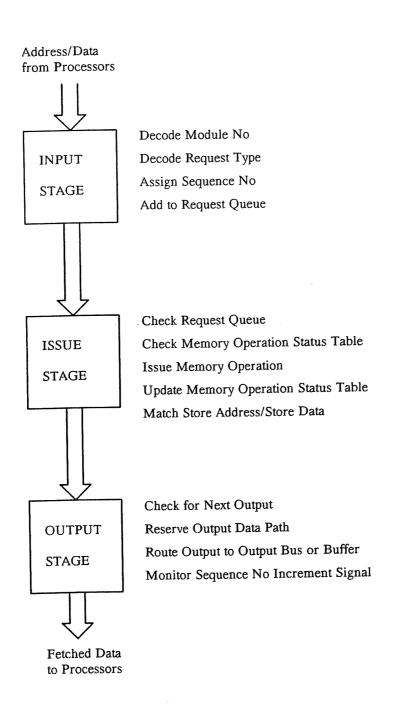

| 4.6. Memory Pipeline Stages and Their Functions                     | 102  |

| 4.7. Organization of the PIPE Architecture with FMRF Memory Con-    |      |

| troller—                                                            | 108  |

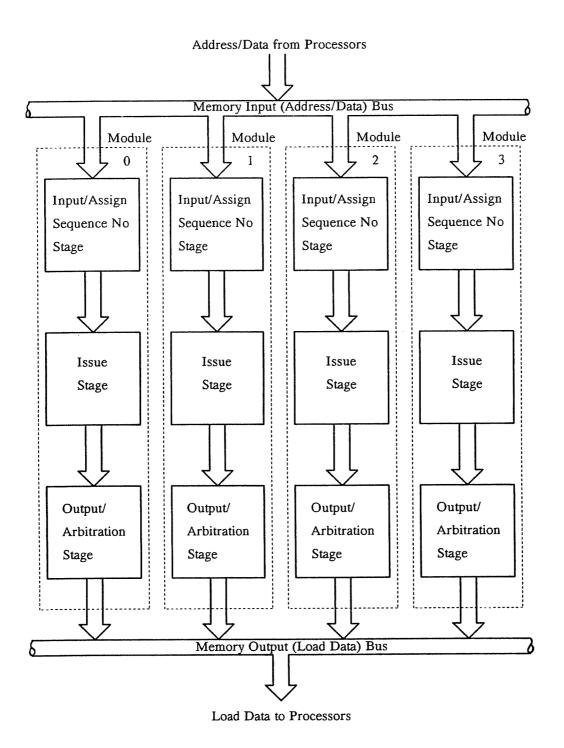

| 4.8. Pipeline Organization of the Memory Controller Using Free-     |      |

| Module-Request-First Scheduling Policy                              | .109 |

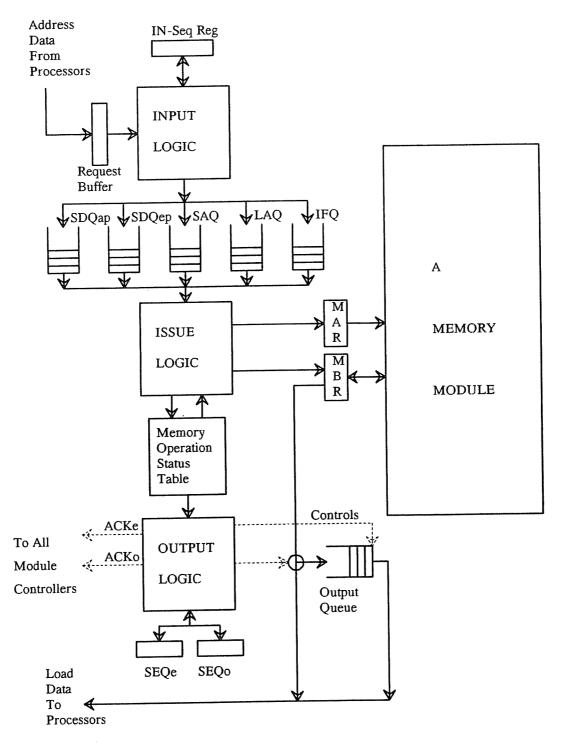

| 4.9. Block Diagram of the Module Controller Using Free-Module-      |      |

| Request-First Scheduling Policy                                     | .110 |

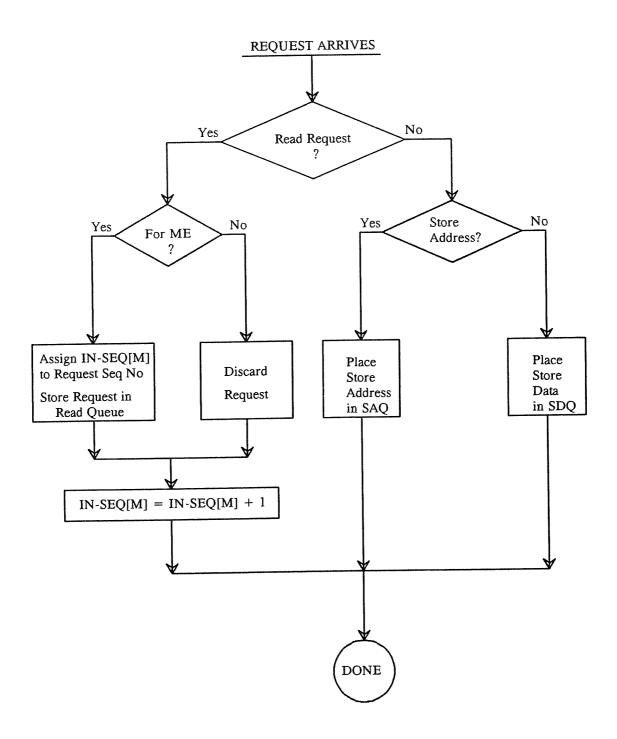

| 4.10. Input Stage Algorithm of Free-Module-Request-First Scheduling |      |

| Policy                                                              | .114 |

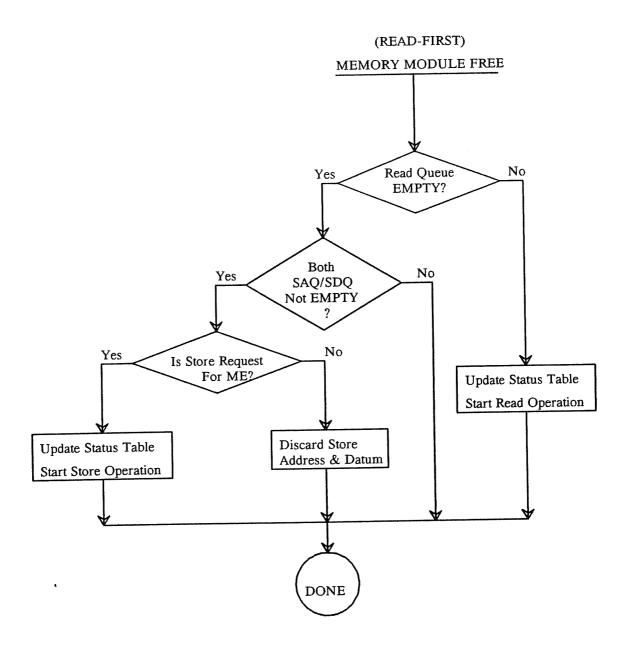

| 4.11. Issue Stage Algorithm of Free-Module-Request-First Scheduling |      |

| Policy —                                                            | _116 |

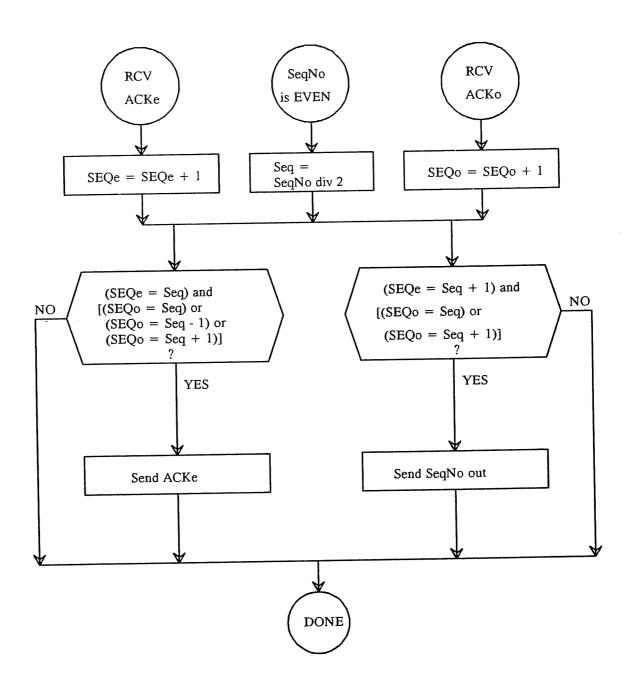

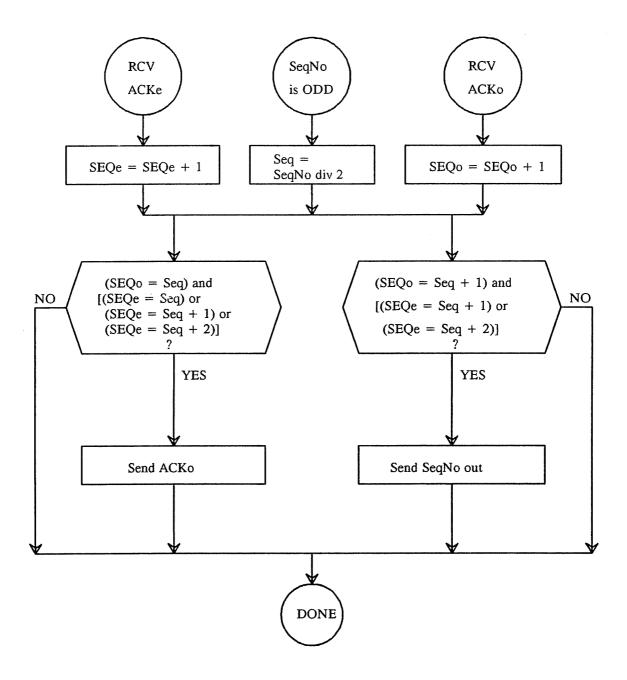

| 4.12. Output Stage Algorithm of Free-Module-Request-First Schedul-  |      |

| ing Policy –                                                        | _122 |

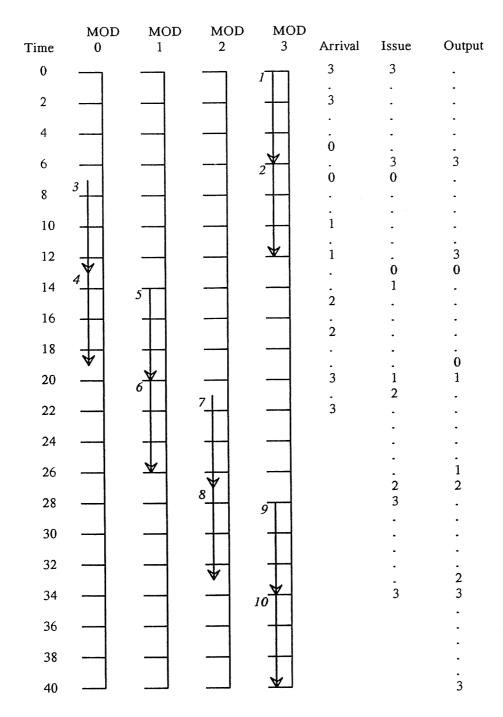

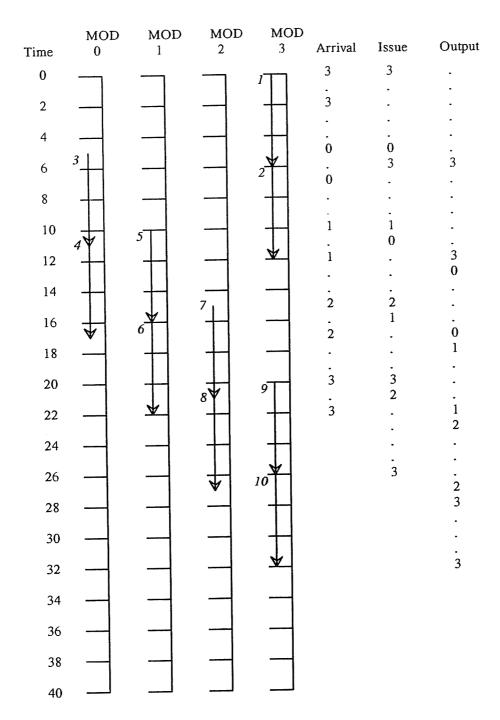

| 4.13. The Timing Diagram of Memory Output Sequence of Example       |      |

| 4.3                                                                 | _126 |

| 4.14. State Transition Diagram of Output Sequence Control for Free- |      |

| Module-Request-First Scheduling Policy                              | _128 |

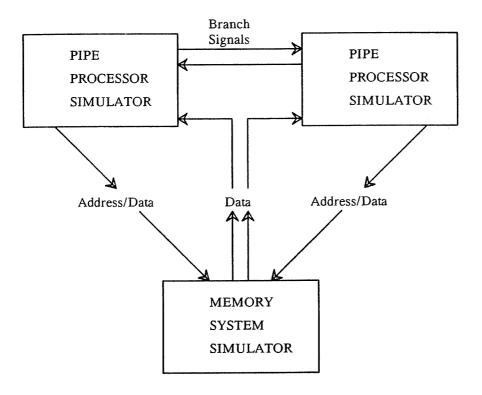

| 5.1. Closed-Loop Simulation Model of PIPE Architecture              |      |

| 5.2. | Performance Comparison of Memory Models When There Are     |     |

|------|------------------------------------------------------------|-----|

|      | Read-After-Write Hazards                                   | 150 |

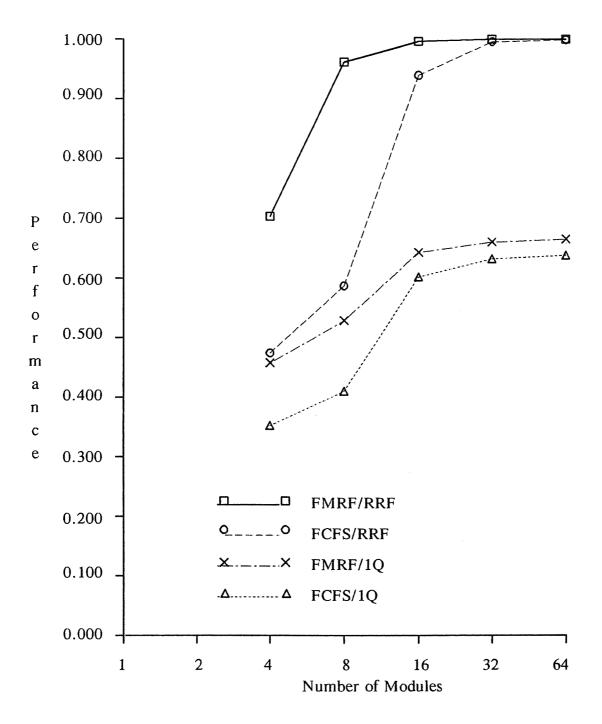

| 5.3. | Performance Comparison of Memory Models When There Are No  |     |

|      | Read-After-Write Hazards                                   | 154 |

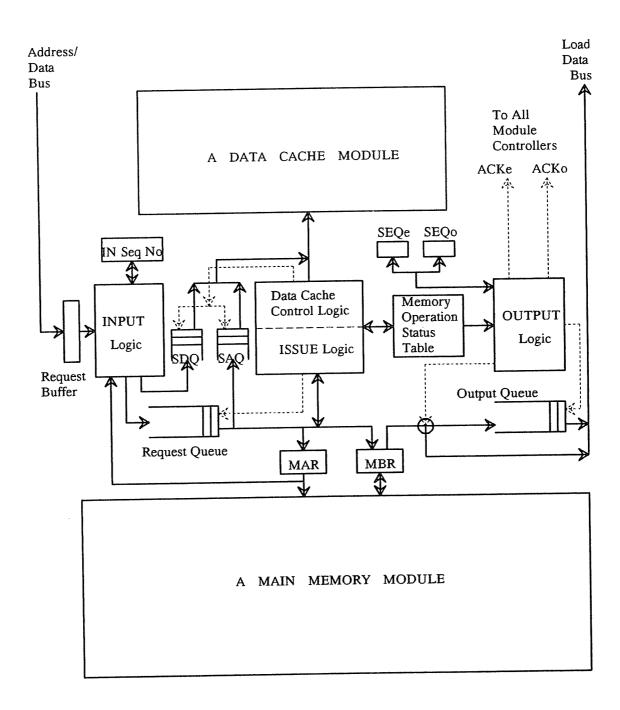

| 6.1. | Block Diagram of a Module Controller with Data Cache       | 161 |

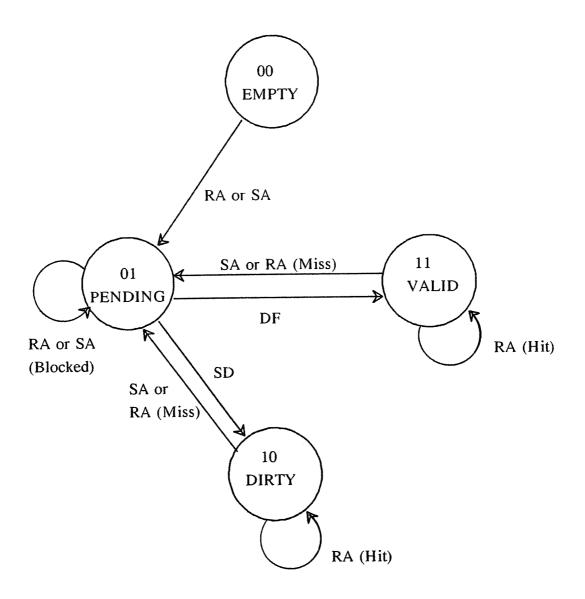

| 6.2. | State Transition Diagram of a Data Cache Entry             | 164 |

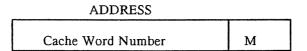

| 6.3. | Address Space of the Data Cache in the Memory System Using |     |

|      | Free-Module-Request-First Scheduling Policy                | 166 |

| 6.4. | Bit Assignment Scheme for Data Cache Placement/Replacement |     |

|      | Algorithm                                                  | 168 |

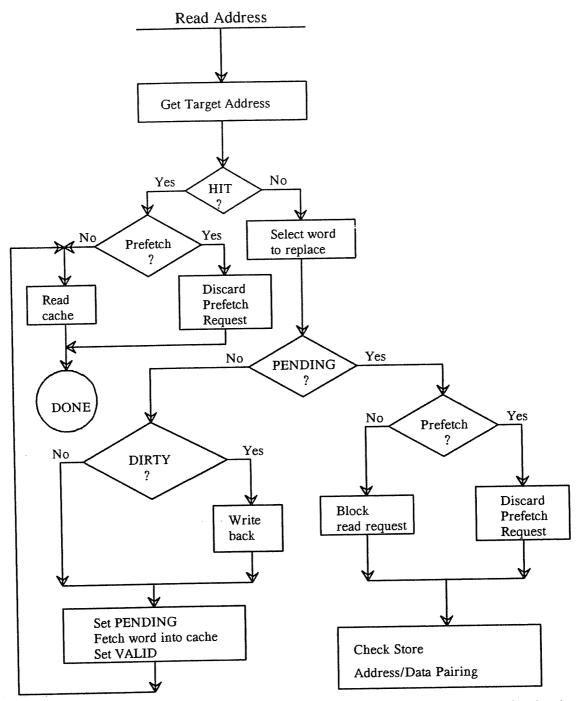

| 6.5. | Algorithm for Servicing a Read Request                     | 169 |

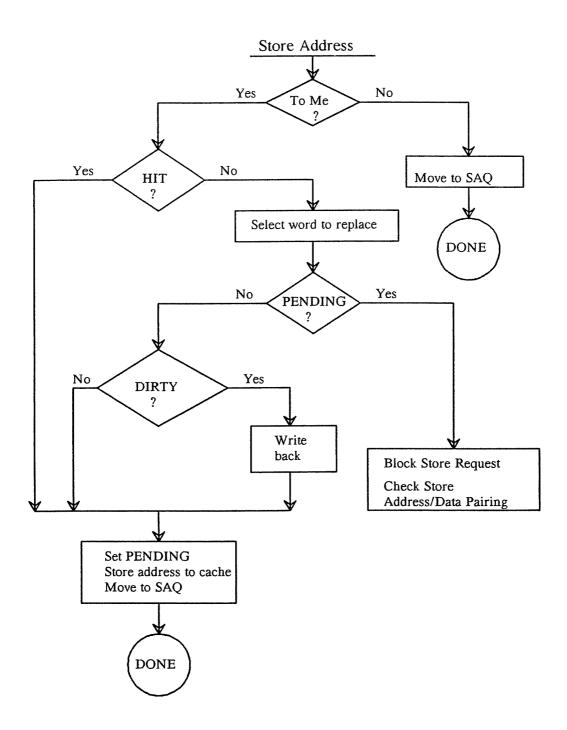

| 6.6. | Algorithm for Servicing a Store Address Request            | 172 |

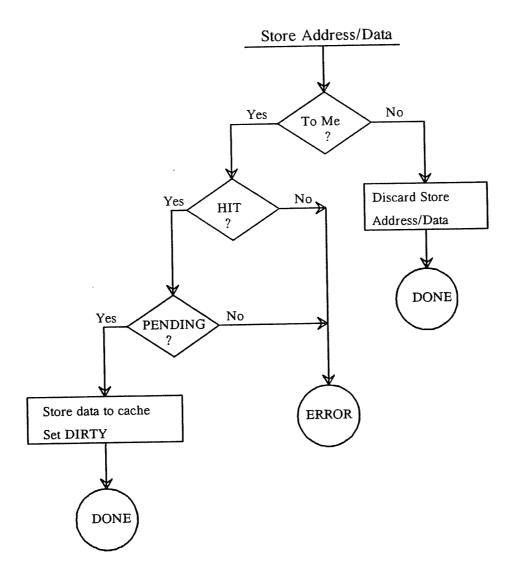

| 6.7. | Algorithm for Pairing Store Address/Data                   | 173 |

| 6.8. | Performance Comparison of Memory Models with and without   |     |

|      | Data Caches                                                | 182 |

|  | , |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

#### CHAPTER 1

#### INTRODUCTION

Several different systems using the technique of decoupled computation have been recently designed [CoSt81, SmiJ82, Ples82, SPKG83]. The CSPI MAP-200 array processor [CoSt81], the Decoupled Access/Execute (DAE) architecture [SmiJ82, SmiJ84], the Structured Memory Access (SMA) architecture [Ples82, PlDa83], and the PIPE (Parallel Instructions and Pipelined Execution) architecture [SPKG83, GHLP85] all share the same design concept: memory request generation is architecturally decoupled from algorithmic computations, resulting in improved performance through parallelism and efficient memory referencing. For example, Weiss and Smith [WeSm84] demonstrated that by decoupling data access from execution, it was possible to implement a computer architecture with minimal design complexity and to provide much of the performance improvement offered by complex issuing methods, such as issuing instructions out of order or issuing multiple instructions simultaneously. Decoupling also allows considerable memory access delay to be overlapped with other operations. The SMA machine of Pleszkun [Ples82, PlDa83] reduced addressing overhead by providing special

access mechanisms in the memory access processor to generate references efficiently for blocks of instructions and several data types. Pleszkun's results showed that the SMA machine reduced the number of memory references to between 1/5 and 2/5 of those required by a conventional VAX computer.

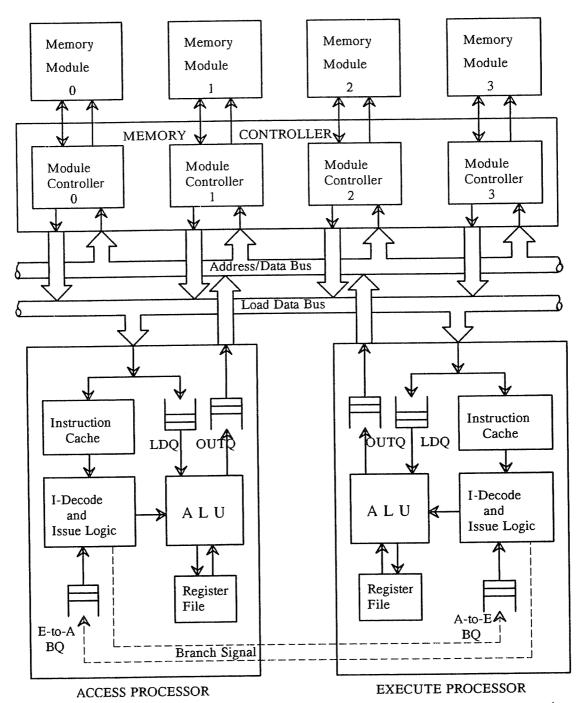

Unlike the von Neumann architecture which consists of one central processing unit (CPU), the decoupled architecture consists of two processors: the *Access Processor* and the *Execute Processor*. Likewise, a single task in the von Neumann architecture is now separated into two subtasks: the *access task* and the *execute task*. Both Access and Execute processors cooperate in executing these two subtasks in parallel and communicate via *hardware queues*. The Access Processor calculates all memory addresses and makes all memory data references for the Execute Processor. Fetched operands are placed in an input queue of the Execute Processor. The Execute Processor carries out the algorithmic operations required on a given operand stream. The results computed by the Execute Processor will be paired with the addresses calculated by the Access Processor, and then stored into main memory. The Access Processor can overlap memory transactions by sending more requests than the memory system can immediately satisfy, and the memory, in turn, may provide more data than the Execute Processor can immediately utilize.

In order for decoupled computation to proceed smoothly, the memory system should be able to service memory requests efficiently and provide operands in order and before they are needed by the Execute Processor. Therefore, the successful implementation of a memory system is key to the improved performance obtained through decoupled computation.

The design of the memory system for a decoupled architecture is the topic of this dissertation. The goal of this research is to design a memory system that can service memory requests efficiently in order to sustain the improved performance through decoupled computation. Techniques to increase the performance of memory systems will be investigated, such as pipelining, interleaving, multiple-words-fetched-per-request, servicing requests out of arrival order, and cache memory. Request scheduling policies will be derived from two strategies: (1) to service requests according to their priorities, and (2) to minimize the total request service time. Then, memory systems with the derived request scheduling policies and the performance improvement features will be designed and evaluated through trace-driven simulations.

A general understanding of the features and performance levels of a decoupled architecture is important to this research. Because the PIPE architecture has all the necessary features for performing decoupled computations, a look at the PIPE architecture can show us clearly how the decoupled computation is performed, and how memory transactions are overlapped. The limitations and problems in the memory system will be listed along with general strategies and approaches to address them. Details of the proposed memory system will then follow in the remaining chapters of the thesis.

#### 1.1. The PIPE Architecture

The PIPE architecture (Parallel Instructions and Pipelined Execution) [SPRG83, GHLP85] is a pipelined, decoupled architecture designed in the VLSI environment. It uses identical processors for the Access and Execute processors

that communicate via hardware queues (Figure 1.1). PIPE uses a simple instruction set with the goal of issuing one instruction per CPU cycle in each of the processors. Each processor issues memory requests to fetch its own instruction stream, and is capable of fetching its own operands<sup>1</sup>. Each processor has registers and hardware queues to store information and a program counter to track its progress. In addition, there is an instruction cache on each processor chip.

Decoupled computation allows the PIPE architecture to explore a new level of parallelism, which is lower than the multiprogramming environment, without precluding traditional multiprogramming. This new level of parallelism permits some code scheduling to be performed dynamically (at run-time), and reduces the burden of static code scheduling done by the compiler.

There are three considerations that guide the design of the PIPE architecture: (1) the von Neumann bottleneck [Back78], (2) the Flynn limit [Flyn66], and (3) efficient code generation by a compiler. The von Neumann bottleneck refers to the communication path between the processing unit and the main storage unit. This path is a potential bottleneck because instruction fetch and instruction execution contend for its available bandwidth. The Flynn limit is the observation first stated in [Flyn66] that at most one instruction can pass through the instruction fetch/decode path per clock period. Code scheduling is required to order the instruction codes for a pipelined architecture, so that the amount of overlapped operations on the pipeline stages can be maximized. Thus, PIPE is designed with three important features: (a) the prepare-to-branch/exit [Scho71] program control scheme, (b) memory Load/Store operation through hardware

<sup>&</sup>lt;sup>1</sup>This capability is not used in the Execute Processor.

Figure 1.1 Block Diagram of a PIPE Architecture

queues, and (c) instruction cache. These features combine to reduce the severity of the von Neumann bottleneck. While features (a) and (b) provide flexibility in compiler code generation, they also result in simple pipeline interlock circuitry, increasing the possibility of issuing one instruction per CPU cycle. For the Flynn limit, PIPE uses two processors to execute two instruction streams simultaneously, so that the number of instructions passing through the instruction fetch/decode paths can be greater than one per clock period.

As shown in Figure 1.1, there are several queues in the PIPE architecture; each is implemented in the hardware. The *Branch Queue* (BQ) is used to pass control information (i.e., branch decisions) between the Access Processor and the Execute Processor. Memory requests are temporarily stored in the *Output Queue* (OUTQ) and are later sent to the memory system as soon as the memory system is prepared to accept the requests. The *Load Data Queue* (LDQ) stores the operands fetched from the memory. The *Load Address Queue* (LAQ) stores the load address requests that fetch operands for the corresponding LDQ of a processor. The *Store Data Queue* (SDQ), and the *Store Address Queue* (SAQ) in the memory system store the store address and the store datum, respectively.

The load operation of the PIPE architecture places a load request into the OUTQ, this load request is then sent to the memory system to fetch the datum from the target address into the LDQ. Another operation retrieves the datum from the LDQ when the datum is needed. The load instruction that starts the load operation is considered to be completed once the load request is placed into the OUTQ. The store operation of the PIPE architecture consists of a store address operation and a store data operation. The store address operation puts an address

into the SAQ, and the store data operation puts a datum into the SDQ. When both the SAQ and the SDQ are not empty, the address and the datum from the heads of both queues are paired and sent to the memory as a store operation. The load/store scheme of the PIPE architecture provide the compiler flexibility to schedule other instructions between the separated load data and retrieve data operations or the separated store address and store data operations, so that the effective delays among the instructions with data dependencies can be reduced. In addition, the separation dissociates the completion of a load/store instruction from the completion of its corresponding memory operation. Therefore, it is possible for the compiler to generate efficient codes which will utilize the computing resource effectively and achieve the issue rate of one instruction per CPU cycle.

The load request of a processor that fetches and delivers data to the LDQ of the other processor is called an *alternative load request*. An *alternative store request* consists of two operations issued by two different processors: (1) an alternative store address operation to put an address into the SAQ of one processor, and (2) an alternative store data operation to put a datum into the SDQ of the other processor. Subsequently, the address and the datum from the SAQ and the SDQ of different processors will be paired in the memory.

In order to increase the memory bandwidth and to facilitate the flow of memory requests through the von Neumann bottleneck, each PIPE processor has two uni-directional buses. One is dedicated to memory input for sending addresses and data to the memory system, and the other is dedicated to memory output for receiving data from the memory system. Tags are used to distinguish between the different types of items appearing on the bus. All the data paths are uni-

directional so that memory requests and fetched data can be overlapped.

## 1.2. Constraints on the Memory System

While the use of hardware queues contributes several advantages to a decoupled architecture, it also places constraints on the memory system. The constraints are: (1) the data must be placed in the queue in the correct order based on the program algorithm, and (2) the required data is the only data allowed in the queue. Three techniques to increase memory bandwidth will be investigated: cache memory [SmiA82], multiple-words-fetched-per-request, and servicing memory request out-of-order [BoGr67]. Each of these techniques must work with a bookkeeping scheme, whose responsibility is to reorder the fetched data while complying with the constraints.

# 1.3. Design Issues of the Memory System

Design techniques are employed to construct an efficient memory system within the constraints stated above. Three issues related to the use of queues to buffer memory requests and fetched data in the design of the memory system are described below. Each issue is accompanied by a possible design alternative.

- (1) Multiple memory requests can be simultaneously waiting for service in the memory system. An efficient request scheduling algorithm may be needed to maximize the throughput and/or meet the urgency of memory requests.

- (2) If the load address and the store address requests are stored in separate queues, the load and store request can be serviced out of arrival order. Thus, memory access hazards -- Read-After-Write, Write-After-Read, and Write-After-Write hazards -- must be checked before a load or a store request is serviced. When fetch and store requests are accessing the same memory location, the memory system may detect a Read-After-Write or Write-After-

Read access hazard before the store datum arrives. If a Read-After-Write access hazard is detected, the memory system should short-circuit the store datum to the fetch request, so that a memory fetch cycle can be avoided. The impact of access hazard on the performance of memory system will be investigated, as well as the performance improvement through short-circuiting Read-After-Write data.

(3) Each PIPE processor has two buses dedicated to input and output, respectively. The memory system can be designed to receive two inputs per clock period, one from each processor, or one input per clock period. The performance difference for these two alternatives will be investigated. If the performance difference is substantial, alternative multiplexing schemes for receiving one input per clock must also be studied.

The memory controller can be considered as another processor in a decoupled architecture. Its responsibility is to service requests efficiently and to provide operands before they are needed, so that decoupled computation can proceed smoothly without excessive memory wait time. During decoupled computation, it is possible that the Execute Processor falls behind the Access Processor. It is also possible that the memory controller cannot meet the demand from both Access and Execute processors. If the Execute Processor is running behind and becomes the bottleneck of decoupled computation, the memory controller should service the request of the slower processor first. Thus, it will reduce the memory delay for the slower processor and speed up the progress of decoupled computation. If the memory controller cannot meet the demand of requests from the processors, the memory controller should service requests as fast as it can and minimize its effects as the bottleneck of decoupled computation. Thus, the memory request scheduling policy can be designed with two strategies: (1) to service requests according to their priorities, or (2) to minimize the total request service time.

Since there are different ways to organize the queue space, to store memory requests, to schedule memory requests, to design multiplexing schemes, and to implement bookkeeping schemes, this research will study alternative schemes to address each issue. These schemes will each be evaluated, and their tradeoffs analyzed. A selection of the most efficient scheme is then proposed.

A review of the previous work related to the performance of interleaved memory models, memory access conflicts and access hazards, memory system designs of decoupled and non-decoupled architectures, will be discussed in the next chapter. After a study of memory reference characteristics for decoupled computation is presented in chapter 3, several request scheduling policies will be proposed. The design and the simulation of the pipelined, interleaved memory systems for these scheduling policies will be presented in chapters 4 and 5, respectively. Chapter 6 will discuss the design of a data cache to further enhance the performance of the memory system.

#### CHAPTER 2

### A Survey of High Performance Memory System Designs

The memory system is a major bottleneck of a von Neumann architecture [Back78]. Matching the memory bandwidth with the speed of the central processing unit has long been an important factor in the design of computing systems.

Latency is the time it takes for a processor to fetch information from the main memory. When the memory system receives a request, three steps are required to complete the service. First, the address of the request is decoded; then, the addressed memory location is selected. Finally, the read or write of a word at this location will take place. The total fixed time to carry out these three steps is called a memory bank busy time. A memory module can only accept one request per memory bank busy time. If there are parallel memory modules in the memory system and the stream of memory references are staggered to enough different memory modules, the apparent memory throughput can be much higher than the reciprocal of memory bank busy time.

Memory access conflicts and access hazards are two important factors that prevent the interleaved memory system from achieving its maximum bandwidth.

A memory access conflict occurs when a memory request is accessing a busy memory module, or when two or more memory requests attempt to access the same memory module in the same clock period. When an access conflict occurs, one of the memory requests can be stored in conflict buffers and processed in the next memory cycle. A memory access hazard exists when more than one memory request references the same memory location, and an incorrect sequence of memory operations can result in using wrong data or storing wrong information into memory. There are three kinds of access hazards: the *Read-After-Write* (RAW) hazard, the *Write-After-Read* (WAR) hazard and the *Write-After-Write* (WAW) hazard. Techniques for reducing memory access conflicts and resolving access hazards will be discussed in the following sections.

A discussion of the characteristics and the theory of interleaved memory systems is necessary for designing a high performance interleaved memory system. This is followed by examples of methods used to reduce memory access conflicts and resolve memory access hazards in current memory systems.

## 2.1. Theory of Interleaved Memory System

Consider an interleaved memory system with *m* memory modules of *n* memory words per module and in which each memory module performs operations independently. The memory word is the unit of a memory operation, and not necessarily the same width as the CPU word. Interleaving techniques can increase memory bandwidth, allowing the use of slow, inexpensive main memory to match the speed of the processing unit, and providing a large memory at low cost.

In a conventional memory system, each memory module contains n consecutive memory words and the word at address i is in module i div n. The amount of memory in the system can be increased by simply adding more memory modules. When a memory module malfunctions, a contiguous block of memory is inaccessible; the rest of memory can still be accessed. Because instructions are stored in adjacent memory words, the likelihood that a segment of program code is stored in one memory module would be high. In such a case, memory conflicts are frequent and the latency for instruction fetches will be as long as the memory bank busy time. However, this memory organization can be used for some systems where reliability, reconfigurability, or cost is the main concern.

In the interleaved memory system, the consecutive n memory addresses are located across the m memory modules -- the word at address i is in module i mod m. This low-order interleaving scheme can eliminate most memory conflicts, resulting in latency close to the access time (the time required by a memory module to provide the stored information). This technique is used in many high performance computer systems, such as the IBM 360/91 [AnSp67, BoGr67], the CDC6600 [Thor70], and the CRAY-1 [Russ78]. The low-order interleaving scheme is assumed throughout the rest of the dissertation.

Since the first appearance of interleaved memory systems in STRETCH [Kuck78] and ILLIAC II [UIII57], memory models [Hell67, BuCo70, CoBu71, Ravi72, Bhan75 and ChKL77] with different assumptions have been introduced to evaluate the performance of interleaved memory systems. The effective memory bandwidth, which is defined to be the average number of memory accesses per memory cycle, is used to measure the performance in each memory model.

Chang and others [ChKL77] established models to study the data dependency of the address streams and the performance of interleaved memory models with conflict queues. Their results indicate that the performance of a properly designed memory system can be a linear function. Hellerman's model [Hell67], on the other hand, established a square root function of the number of memory modules.

## 2.1.1. Memory Models without Conflict Queues

Hellerman's model considers memory requests as a stream of addresses in the range of 1 through m, where m is the number of memory modules. His assumptions are that no queuing of requests are permitted on busy modules, and that there is no data dependency between successive memory references. Addresses are examined in order until the first duplicate memory module number is found. These first k requests to distinct addresses are then processed in parallel. He shows that the probability of encountering a string of exactly k distinct integers with the (k+1)st a repetition of one of the k others is

$$P(k) = \frac{k (m-1)!}{m^k (m-k)!}$$

The average length of address sequences, which is the effective bandwidth, is the sum of the products of the probabilities and k:

Bandwidth =

$$\sum_{k=1}^{k=m} k P(k)$$

When  $1 \le m \le 45$ , Hellerman found a good numerical approximation of the above equation to be  $m^{0.56}$ , or approximate  $\sqrt{m}$ . The error is no more than 4.3

percent. This means that the effective memory bandwidth of an interleaved memory system is a *square root* function of the interleaving factor. Knuth and Rao [KnRa75] also show in a closed form that the effective bandwidth of Hellerman's model is

Bandwidth =

$$(\frac{\pi m}{2})^{\frac{1}{2}} - \frac{1}{3} + \frac{1}{12}(\frac{\pi}{2m})^{\frac{1}{2}} + O(m^{-1})$$

This confirms that Hellerman's bandwidth is asymptotic to  $\sqrt{m}$ .

In Ravi's memory model [Ravi72], p memory requests are generated during each cycle. This model can be considered as a multiprocessor system of p processors and m memory modules. Ravi derives a formula to compute the average number of distinct integers in a group of p integers chosen uniformly from the integers 0 to m - 1. He takes this value to be the effective bandwidth in the steady state and is computed as

Bandwidth =

$$\sum_{k=1}^{k=t} k \frac{k! S(p,k) {m \choose p}}{m^p}$$

where t = min(m,p), S(p,k) is a Stirling number of the second kind, and k!S(p,k) is the number of ways to put p distinct requests into k distinct memory modules with each modules holding at least one request. Ravi's formula was reduced to a very simple closed form [ChKL77], that is

Bandwidth =

$$m \left[ 1 - \left( 1 - \frac{1}{m} \right)^p \right]$$

.

It is shown that, given a constant p/m ratio, the effective bandwidth in the steady state is a *linear* function of either m or p. The assumption in Ravi's model that the conflicting requests are simply ignored and not re-submitted does not correspond to any real machine.

Another memory model similar to Ravi's model but of different assumptions is introduced by Chang [ChKL77] to study the performance of interleaved memory in multiprocessor systems. Chang's model assumes that there are p independent address streams, each uniformly distributed, issued from p processors. In any given stream, an address can be accessed only after its predecessor has been accessed. Those processors not being serviced will reissue their addresses in the next cycle. Simulation techniques are used by Chang to find the steady-state bandwidth of their model. The results show that the effective bandwidth is linear in p but is 6 to 8 percent worse than Ravi's result. Chang believes that the difference is due to the difference in assumptions and the statistical error in the simulation. Chang's results are very close to Bhandarkar's results [Bhan75], where a similar model is solved with a Markov chain method.

## 2.1.2. Memory Models with Conflict Queues

Coffman, Burnett, and Snowdon [CoBS71] introduced a memory model with a conflict queue to buffer conflicting requests. They assumed that the addresses are not uniformly distributed but are determined by two parameters  $\alpha$  and  $\beta$ . They assumes that the probability of a request accessing the next module in sequence (modulo m) will be  $\alpha$  and the probability of addressing any other module out of sequence will be  $\beta$ , where  $\beta = (1-\alpha)/(m-1)$ .

The stream of memory requests from the request queue is examined and the conflicting requests are placed in the conflict queue. For each memory cycle, the conflict queue are first scanned and then the new requests in the request queue are scanned. This procedure continues until either the conflict queue is full or all the memory modules are busy. Because of memory conflicts, memory requests can be serviced out of their arrival sequence in this model. However, this model assumes that there are no data dependencies between requests and therefore out-of-order service is permitted. Their results indicate that handling requests out-of-order can greatly increase memory bandwidth. For example, if  $\alpha = 0.25$  and m = 16, the bandwidth is about 4.5 when no conflict queue is used but jumps to 9.5 if a conflict queue of length 4 is used. Clearly, as the length of the conflict queue approaches infinity, the bandwidth approaches the interleaving factor m.

[ChKL77] to investigate the effect of using queues to improve the memory bandwidth in a multiprocessor system. There are *p* processors and *m* memory modules in this model, each memory module has a conflict queue. When a memory module receives more requests than it can queue, then the processors which submitted the unqueuable requests are blocked and will submit their request during the next memory cycle. Since it is possible for a processor to have two or more requests satisfied in one memory cycle (e.g. its current request in one module plus some previously queued requests in other modules), Chang assumes that the processors are capable of accepting more than one returned result in one memory cycle. Simulation techniques are used to evaluate this model. This study indicates that adding queues to the memory system did

improve the bandwidth of the system, and the effective bandwidth in the steady state is a *linear* function of r, where r = p/m. When r = 1, the simulation results showed an approximate 5 percent improvement over Ravi's model if the memory queue length is 1, and an approximate 10 percent improvement over Ravi's model if the queue length is 2.

In summary, the literature review of interleaved memory models suggests that if a conflict queue is not implemented in an interleaved memory system, (1) for a single request stream, the effective memory bandwidth approximates a *square* root of the interleaving factor; (2) for p request streams and m memory modules, the effective memory bandwidth is a *linear* function of either p or m, given a constant p/m ratio. If a conflict queue is used with an interleaved memory system that services a single request stream, the effective memory bandwidth is a *linear* function of the interleaving factor.

#### 2.2. Methods to Reduce Memory Access Conflicts

Although interleaved memory systems can reduce the frequency of memory conflicts and balance the memory speed with the processor speed, the nondeterministic occurrence of memory conflicts can degrade the performance of a memory system when the request arrival rate is increased. Better memory systems design requires understanding memory reference patterns and program behavior.

Memory references may be partitioned into three categories: (1) instruction fetch, (2) scalar variable access, and (3) array variable access. These three categories of memory reference types and their characteristic access patterns can

influence the approach to the design of interleaved memory systems. The memory addresses for instruction fetches are sequential until there is a successful branch. Scalar variables are frequently stored in blocks of memory spaces, but are referenced unpredictably. Array variables are usually referenced in a regular sequence. The addresses of these referenced elements can be in contiguous memory locations, or in locations with the same number of words separating two consecutively referenced elements. The distance between two consecutive array element references is called a *stride*.

Since the instruction stream comprises sequential words, multiple-words-returned-per-fetch-and/or prefetching techniques may be used to fetch the instruction words. Many mainframe systems use wide processor-memory buses to fetch more than one memory word per access, with the expectation that the prefetched words would be used in following cycles. For example, two 32-bit words are fetched per memory access in the IBM SYSTEM/360 Model 91 [AnST67, BoGr67], and the fetched instruction words are stored in an *instruction buffer array*. Other computer systems with cache memories use the cache line to be the unit of memory access such that contiguous memory words are fetched into the cache memory in each memory fetch cycle. Instruction buffer arrays and cache memories are used not only to match the demand from the processing units, but also to reduce the number of memory requests, thus reducing memory conflict.

For array variable accesses, many supercomputers such as the CRAY-1 [Russ78], the CDC Star-100 [HiTa72], the CYBER205 [Linc82], and the Burroughs Scientific Processor BSP [KuSt82], use interleaving techniques and vector instructions to facilitate vector operations. The arrays must be carefully assigned

to memory in order that conflict-free memory access is achieved.

The memory system of the CRAY-1 computer is 16-way interleaved. It prevents memory conflicts except in the case of memory accesses that step through memory with a multiple of 8-word increment. Vector instructions place a reservation on whichever functional unit they use, including memory, and on the input operand registers. Vector elements are brought into the register files and manipulated within the register files. Once issued, a vector instruction produces its first result after a delay equal to the functional unit latency. Subsequent results then continue to be produced at a rate of 1 per clock period. These results must be stored in a vector register. A separate instruction is required to store the final result vector to memory. In order to facilitate the operation flow of a vector functional unit, the memory system has to be idle before a vector stream is initiated. The memory system is reserved for the vector operation such that the vector elements can be accessed without interference by scalar accesses. Conflictfree memory references can thus be scheduled unless the stride is a multiple of eight. When a vector memory reference with a stride of a multiple of eight is detected, speed control is put into effect, and vector elements are referenced at a reduced but predictable rate.

The CDC Star-100 and the CYBER 205 are *memory-to-memory* vector machines. Unlike the CRAY-1 computer, the data in vector form are read from central memory and sent to the arithmetic units with the results returned to memory upon completion of the vector operation. These two systems can support up to three simultaneous vector streams: two load streams and one store stream. In the CYBER 205, the memory system is 128-way interleaved; it is organized

into sixteen sections each of eight banks. The lowest order three bits of a memory address select the bank number of a section, which is selected by the next higher four bits. Instead of slotting I/O requests around the memory demands of the vector streams as in the input/output scheme of the STAR-100, the CYBER 205 designers chose to give I/O free entry to the central memory. In order to service two vector load streams, one vector store stream, and an I/O data stream simultaneously, the memory system of the CYBER 205 fetches eight consecutive memory words belonging to one vector and stores them in buffers. In the following clock period, eight consecutive memory words of another vector are fetched and stored into buffers. In the third clock period, eight buffered results can be stored into the memory. The fourth clock period is dedicated to I/O transfers. Then, the same four operation sequence is repeated. If the vector accesses are not of stride one, the needed elements must first be gathered from the buffered consecutive vector words before being used as input operands, and the results must be scattered into the consecutive memory words in the result buffers before being stored in the memory. A vector control unit will determine the timing of memory requests when a vector instruction is initiated, so that there are no memory conflicts.

The memory system for the Burroughs Scientific Processor was organized differently from those of the other vector machines. There were two separate memory units in the BSP system: the *control memory* and the *parallel memory*. The *control memory* was used to store portions of the operating system and all user programs as they were executed. It was also used to store data values that were operands for those instructions executed by the scalar processor unit. The *paral*-

lel memory was used only to hold data arrays for the parallel processor. There were 16 arithmetic processing units in the parallel processor, and 17 memory modules in the parallel memory.

The organization of the *parallel processor* and the *parallel memory* is the result of a study of parallel memory by Budnik and Kuck [BuKu71]. They demonstrated that, in general, accessing rows, columns, and diagonals of a square array without conflicts is impossible to accomplish if any *power of two* number of memory modules is used.

If the distance between the referenced array elements and the number of memory modules are relatively prime, however, then all the modules can be accessed simultaneously without conflict. The data of array elements are then stored such that there are conflict-free accesses to row, column, and diagonal vectors of length 16.

An input alignment network is needed to arrange the fetched array elements into proper order in this memory system, and an output alignment network is used to re-align the array elements before they are stored into the *parallel* memory. Also, modulo 17 arithmetic is required to compute the module number of an array element and the address within the module. For example, the module number M of A(i,j) is

$$M = (j*I + i + base) \mod 17$$

where I the row dimension of array A(I,J) and base is the starting address of array A(I,J).

# 2.3. Memory Access Hazard and Its Resolution Schemes

Since the ultimate performance of an interleaved memory system is limited by the memory modules themselves, the memory controller must optimize the data rate by efficiently scheduling the unserviced requests and controlling the processor-memory buses. The data rate can be increased by issuing memory operations for memory requests whenever the required modules become available, i.e., not in logical order. The memory controller must detect the access hazards and correctly sequence several stores, or stores and fetches, to the same memory location.

Compiler techniques can also be used to avoid memory access hazards. Given certain physical constraints, the compiler can detect the potential access hazards at compilation time, then schedule the code such that the second memory request will not be started until the first memory request to the same address is completed. However, because every store request can create a potential access hazard, it is not a simple task for the compiler to precisely detect the access hazards. For example, when a fetch instruction and a store instruction are generated for two elements of the same array variable that are referenced in an arithmetic statement, the compiler has to know the indices of these two elements in order to decide whether or not there is a potential access hazard between them. If the indices of these two array elements are indexed by two arithmetic expressions and the results of these two expressions cannot be computed in the compilation time, then the compiler can only assume that there is a potential access hazard between these two array elements. In addition, if the fetch and the store of the same array variable are initiated from different program statements or each of

them are submitted by the code of the same loop segment but at different iterations of the loop during the run-time, the correct detection of access hazard can become very complex for the compiler. Also, worst-case behavior must always be assumed. For a cache memory system, this is a serious penalty because the compiler decides whether a potential access hazard may occur during the run-time based on the completion time of the memory request in conflict. Thus, the time required to fetch information from main memory for a cache miss must be assumed for each detection of potential access hazard.

Alternatively, hardware control can be used to detect and resolve the memory access hazards when requests are submitted at run-time. Three computer systems, the IBM SYSTEM/360 Model 91, the IBM SYSTEM/370 Model 168, and the CSPI MAP-200 array processor [CoSt81], will be used as examples to discuss how memory access hazards are resolved in non-decoupled architectures and a decoupled architecture.

## 2.3.1. The Storage System of the IBM SYSTEM/360 Model 91

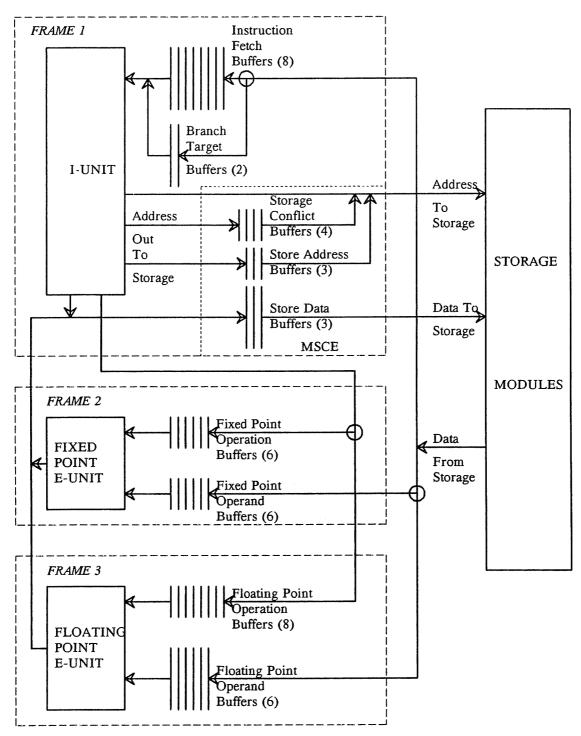

The IBM SYSTEM/360 Model 91 [AnST67, BoGr67] is a high performance pipelined computer system. In order to achieve a smooth operation flow along the pipeline stages, the organizational techniques of storage interleaving, arithmetic execution concurrency, and buffering are utilized. The tasks of the pipeline stages are performed by three major processing units: the *Instruction Unit* (I-unit), the *Execution Unit* (E-unit), and the *Main Storage Control Element* (MSCE). The E-unit is further divided into two independent units: the fixed point execution unit and the floating point execution unit. A block diagram of the IBM SYSTEM/360

Model 91 is shown in Figure 2.1 with an illustration of buffer allocation and function separation.

The central control functions for the CPU are performed in the I-unit, which decodes and sets up instructions for execution by the E-unit. The I-unit accomplishes this by scanning each instruction, in the order presented by the program, and clearing all necessary interlocks for buffer allocations before releasing the instruction. In addition, when a storage reference is required by the operation, the issuing mechanism performs the necessary address calculations, initiates the memory requests, and establishes the routing by which the operand and operation will ultimately be merged for execution within the E-unit.

In designing the I-unit, many program situations were examined by the design group of the IBM SYSTEM/360 Model 91 [BoGr67]. They found that, while many short instruction sequences are nicely ordered, the trend is toward frequent branching. In addition, even with sophisticated execution algorithms, very few programs can actually cause answers to flow from the pipeline stages at an average rate in excess of one every two cycles. Inter-instruction dependencies, storage and other hardware conflicts, and the frequency of operations requiring multi-cycle execution all combine to prevent this rate from being achieved.

In order for the I-unit to consistently run ahead of the E-unit, the multiple-words-returned-per-fetch scheme is used in conjunction with instruction fetching. Additionally, various types of buffers are used to smooth the total instruction flow by allowing the initiating pipeline stages to proceed despite unpredictable delays further down the pipeline. Buffers for instruction fetch, operand fetch, operand store, operation, and address are used among the I-unit, the E-unit and the

Figure 2.1 -- Buffer allocation and function separation within the IBM SYS-TEM/360 Model 91 from [AnST67].

MSCE as illustrated in Figure 2.1. The I-unit will not issue an instruction unless the required buffers are available. For example, a free operand buffer will be assigned to an operand fetch request before the request is sent to the MSCE, so that there is always a buffer available to receive the operand fetched from the memory.

For each instruction, following the clearing of all interlocks, the decode decision determines whether or not to issue the instruction to the E-unit and initiate address generation for memory access, or to retain the instruction for sequencing within the I-unit. For example, after a storage-to-register (RX) instruction is decoded, the issuing of the RX instruction to the E-unit and the fetching of the operand together constitute a controlled splitting operation, where sufficient information is forwarded along both paths to effect a proper execution unit merge.

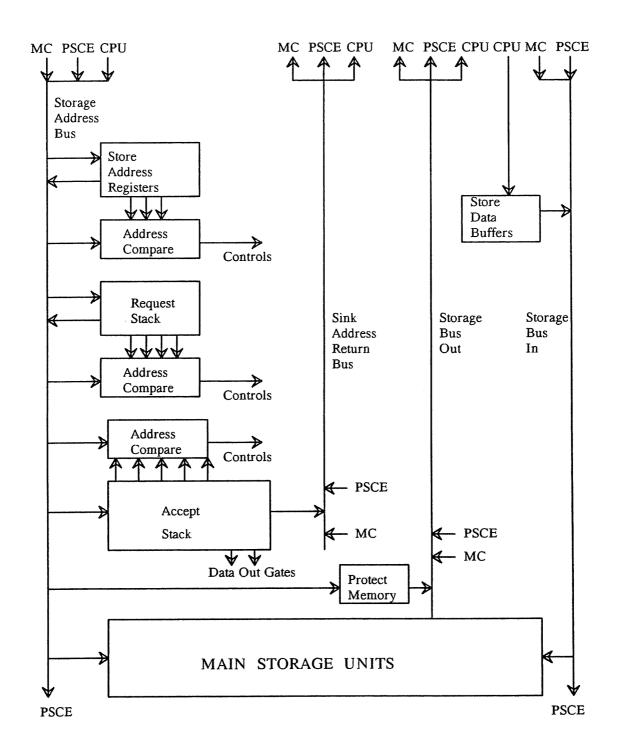

The block diagram of the MSCE is shown in Figure 2.2, where MC is the maintenance console and PSCE is the Peripheral Storage Control Element. There are different functional areas within the MSCE. Only those related to memory access hazard resolution will be discussed. Details about other functions of the MSCE can be found in [BoGr67].

There are three request queues in the MSCE, each of them associative for address matching: (1) The store address registers, where three registers hold the addresses of stores pending availability of store data. (2) The request stack where a set of four registers holds rejected requests from the processor pending availability of the memory module, and thus buffers the processor from storage conflicts.

(3) The accept stack where a set of shift registers hold information on accepted requests in process. In addition, there are three store data buffers that hold store

Figure 2.2 -- Block Diagram of MSCE Organization from [BoGr67].

data words from all areas of the processor pending availability of the memory module.

A memory request to the MSCE consists of an address, a return or sink address (to route the returning data), control bits (to define the operation precisely), and the data for store operations. When neither memory conflicts nor access hazards occur (and store data is available for store operation), the memory request that is transmitted through the storage address bus, can be gated into the accept stack and serviced immediately. However, when there are memory conflicts and/or access hazards, the memory request will be stored in the request stack or the store address registers-depending on whether or not it is a fetch or a store request. For a store request, the store data is submitted by either the I-unit or the E-unit, while the store address is generated by the I-unit. Since the I-unit always decodes and sets up the execution of instructions ahead of the E-unit along the pipeline stages, the store address of the store operation will arrive at the MSCE ahead of the store data if the store data is the result of arithmetic operation produced by the E-unit. In this case, the store address is placed into the store address register waiting for the store data to arrive. There may also be conflicting store requests that are waiting for the memory modules to become available. Thus, the MSCE has to check whether an access hazard exists for each new request.

During each cycle, the MSCE controls determine the source (the peripheral storage control element, the maintenance console, or the central processing unit) that is allowed to make a request. The address of the request is then sent through the address bus. This address bus is also used to load the address of a store

request into a store address register. The store address remains in the store address register until its data word is generated by the processor. A successful request is sent to the proper memory module, or to the PSCE if the extended main storage is requested. If a request is accessing main storage, it is also gated into the top of the accept stack with its control information. Any rejected processor request is stored in a position of the request stack for later recycling.

The priority order for the requesting sources used by the MSCE to decide which should be selected is:

- (1) PSCE to (main) storage.

- (2) Maintenance console to storage.

- (3) Request stack to (main) storage for Multi-Access.

- (4) Store address register to storage.

- (5) Request stack to storage.

- (6) Processor to storage.

When a fetch address passes through the address bus, it is compared with addresses in the store address registers, the request stack and the accept stack. A match with a store address register forces rejection of the request and the request is stored in the request stack. This is because the acceptance of the request would have caused an out-of-sequence fetch. A Read-After-Write access hazard is therefore detected and resolved. A match with an address in the accept stack implies that the desired word is being fetched by a previous request, and can be obtained when the previous request is completed without selecting a memory module or waiting for the memory module to become free. This is the *Multi-Access* scheme used to obtain data for a fetch following either a fetch or a store to the same memory address.

When a store address is sent to the MSCE, it is gated into a store address register and will wait for the store data to be available. Once the store address and the store data are available, the store request is gated to the address bus as soon as possible. The store address register is made available once again to the I-unit, which considers a store operation completed once it loads the store address register. If the accessed memory module is busy or the store address matches with an address in the request stack, (Write-After-Read or Write-After-Write hazard detected) the store request is gated into the request stack.

When a request address passes through the address bus, a match with an address in the request stack causes the request to be tagged for a future Multi-Access operation, and to be gated into another position of the request stack. The presence in the request stack of an outstanding request for a particular address causes the second request to be rejected, thus keeping the two in the proper sequence.

In summary, hardware interlocks in the form of address comparators (address bus vs. pending store address registers and pending requests in the request stack) are used to order stores to the same address, and to detect and reorder out-of-sequence store/fetch requests to the same address. Hence, memory access hazards in the IBM SYSTEM/360 Model 91 are detected and resolved.

The storage system of the IBM SYSTEM/360 Model 91 is a high performance memory system. However, its hazard detection and resolution scheme requires centralized interlock control and associative request buffers that can be too complex to be partitioned and implemented on VLSI chips.

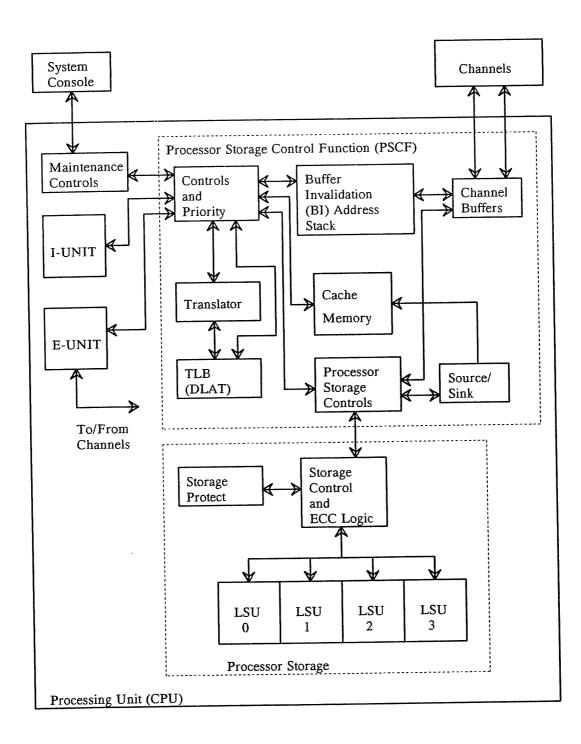

#### 2.3.2. Resolution of Access Hazards in the IBM SYSTEM/370 Model 168

The memory access hazard resolution scheme in the IBM SYSTEM/370 Model 168 [IBM76] is very different from the SYSTEM/360 Model 91. Instead of detecting and avoiding out-of-sequence (fetch/store) memory operations before the operations are started, the IBM SYSTEM/370 Model 168 detects the out-of-sequence fetch after the data is fetched from the storage system. The out-of-sequence fetch is ignored, and a fetch request has to be submitted again after the store is completed.

The IBM SYSTEM/370 Model 168 is a cache-based architecture. The high-speed cache permits the central processing unit to work with the 80-ns cache, rather than with a relative slower 4-way interleaved main storage system. Similar to the SYSTEM/360 Model 91, the major processing units of SYSTEM/370 Model 168 are: the I-unit, the E-unit, and the *Processor Storage Control Function* (PSCF). The I-unit fetches, decodes instructions, makes operand fetch requests and sets up instructions for execution by the E-unit. The PSCF controls requests for the processor storage from the I-unit, the E-unit, the maintenance console, and the I/O channels. As illustrated in Figure 2.3, the PSCF has these major sections: priority controls, translator and translation lookaside buffer (TLB), buffer (caches are called buffers in the IBM systems) invalidation address stack (BIAS), channel buffers, source/sink, and processor storage controls. Together, these units provide the following functions:

- (1) Determine the priority of I-unit and E-unit requests.

- (2) Determine the priority of the CPU and the channel for processor storage requests.

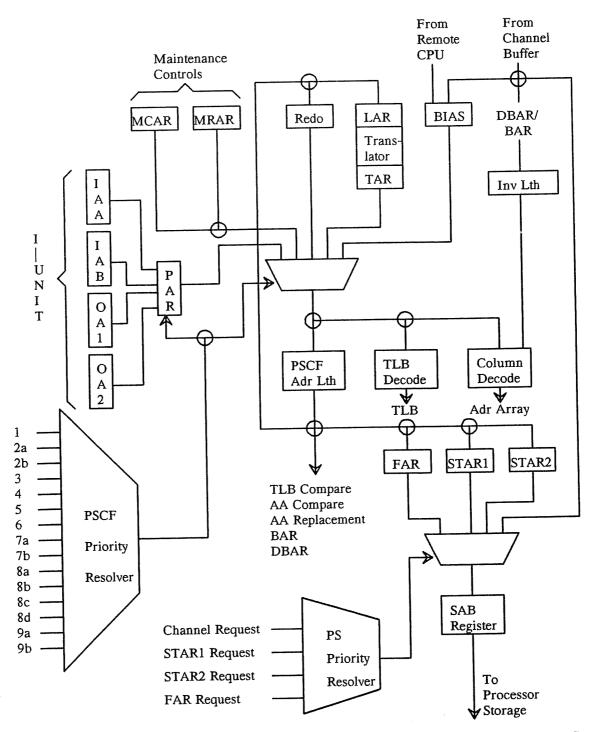

Figure 2.3 -- Block Diagram of the PSCF Organization of IBM SYSTEM/370 Model 168 from [IBM75].

- (3) Translate logical addresses to physical addresses for CPU requests. Recently translated addresses are held in the TLB (also called the DLAT), so that the translation process can be accelerated.

- (4) Buffer recently accessed instructions and data in the cache memory. The CPU gets its information from the cache memory about 90% of the time.

Only those areas related to memory access hazard will be discussed in the following paragraphs.

Four address registers are used by the I-unit to make memory requests via the Processor Address Register (PAR). These are Instruction Address A-register (IAA), Instruction Address B-register (IAB), Operand Address 1 Register (OA1), and Operand Address 2 Register (OA2). The PAR contains the address sent to the PSCF priority circuits for a storage operation. A word of storage, i.e. 64 bits, is obtained for each storage fetch request. IAA and IAB are used to fetch instructions. One of them fetches the main stream of instructions; the other, which is used for an execute or a branch instruction, fetches the target stream of instructions. OA1 and OA2 are used to fetch and/or store operands, and each of them has its own operand buffer for storing the operand from memory or the operand to be stored into memory. The OA1 and OA2 and their operand buffers can be controlled by either the I-unit or the E-unit. The storage addressing flow for a memory request from the CPU and from other request sources is illustrated in Figure 2.4 with the request lines that feed the PSCF priority resolvers arranged from top to bottom in that priority order. For the requests from the CPU, the store requests are given higher priority than the fetch requests, and the priority of operand fetch is higher than instruction fetch. Table 2.1 lists the priority assignment of requesting sources to the PSCF.

Figure 2.4 -- Storage Addressing Flow within the PSCF of the IBM SYSTEM/370 Model 168 from [IBM75].

| Priority Assignment of Storage Requests in IBM SYSTEM/370 Model 168 |                                                       |

|---------------------------------------------------------------------|-------------------------------------------------------|

| Priority                                                            | Function                                              |

| 1                                                                   | Prefetch Request for Cache Memory                     |

| 2a                                                                  | Invalidate Latch Request                              |

| 2b                                                                  | Buffer Invalidation Address Stack (BIAS) Request      |

| 3                                                                   | Buffer Add/Delete                                     |

| 4                                                                   | Translation Lookaside Buffer (TLB) Update             |

| 5                                                                   | Translator Request                                    |

| 6                                                                   | Redo Request                                          |

| 7a                                                                  | CPU Store Request from OA1 Operand Address Buffer     |

| 7b                                                                  | CPU Store Request from OA2 Operand Address Buffer     |

| 8a                                                                  | CPU Fetch Request from OA2 Operand Address Buffer     |

| 8b                                                                  | CPU Fetch Request from OA1 Operand Address Buffer     |

| 8c                                                                  | CPU Fetch Request from IAB Instruction Address Buffer |

| 8d                                                                  | CPU Fetch Request from IAA Instruction Address Buffer |

| 9a                                                                  | Maintenance Console Store Request                     |

| 9b                                                                  | Maintenance Console Fetch Request                     |

Table 2.1

Fetch requests are issued from the I-unit and store requests are issued from the E-unit (in the IBM SYSTEM/360 Model 91, a store datum can be issued from either the I-unit or the E-unit depending on the instruction format,) with the I-unit handling the interlocking between requests. The operand address register, being used as the destination register of a store operation, becomes busy when an address is loaded by the I-unit. This address register remains busy until the instruction that issues the store operation is completed and the store request is accepted by the PSCF. Once a store request is made, the E-unit cannot initiate another store request until it is signaled by the PSCF. Since there are only two operand address registers (OA1 and OA2), at most two store addresses can exist at the same time. Instructions are released to and executed by the E-unit according to the order presented in the program; thus out-of-sequence stores never occur and *Write-After-Write* hazards are precluded.

When a fetch instruction follows a store instruction, the fetch request by the I-unit may precede the store request by the E-unit. To prevent old data from being used, the I-unit compares the addresses in the source/destination address registers (OA1 and OA2). If a match occurs, then an out-of-sequence fetch is detected. This out-of-sequence fetch is ignored and a fetch is re-submitted after the store is completed. Thus the *Read-After-Write* hazard is detected and resolved.

For the cache memory of the IBM SYSTEM 370 Model 168 uses write-through policy and blocks memory requests when a cache miss occurs. Thus, no access hazards can be introduced by cache operations.

The access hazard detection and resolution scheme of the IBM SYSTEM 370 Model 168 is less complex than that of the IBM SYSTEM 360 Model 91.

However, the scheme of the IBM SYSTEM 370 Model 168 is not suitable for a VLSI decoupled architecture for two reasons: (1) off-chip communication is required to re-submit the memory request that fetches a wrong operand from main memory, and (2) it can create ordering problem for storing the fetched operands correctly into the data queues.

### 2.3.3. Resolution of Access Hazards in CSPI MAP-200

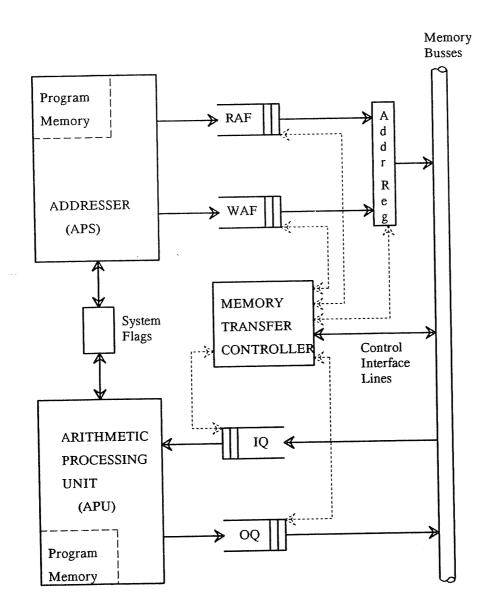

The MAP-200 [CoSt81] is a peripheral array processor and a decoupled architecture. There are three major processing units in the MAP-200: the Addresser (APS), the Arithmetic Processing Unit (APU), and the Memory Transfer Controller (MTC). As illustrated in Figure 2.5, these three processing units are connected by the address and data queues: the Read Address FIFO (RAF), the Write Address FIFO (WAF), the Input Queue (IQ), and the Output Queue (OQ).

The APS computes the load and store addresses and places them into the RAF and the WAF, respectively. The fetched operands are stored into the IQ and used by the APU. When a computed result is to be stored into the memory, it is placed in the OQ by the APU. As soon as the MTC detects that there is a load address in the RAF and there is space in the IQ, a fetch request will be issued to the memory. Alternatively, a store address in the WAF and data in the OQ will cause the MTC to issue a memory store operation. Obviously, the instruction that will send a memory request to the RAF should be blocked when the RAF is full. The size of the RAF and the flow control of handling the RAF full condition is not described in [CoSt81].

Figure 2.5 -- Block Diagram of MAP-200 Organization from [CoSt81].

The MAP-200 system is designed to assign fetch requests higher priority than the store requests, because fetches tend to be needed before stores. Cohler and Storer investigated the performance using this priority scheme over a wide range of algorithms. Their results did not produce a situation where giving a higher priority to the store request than the fetch request would have improved performance. However, they did find examples where, in giving output (writes) preference, throughput is improved.

Out-of-sequence memory operations will occur when a fetch request after a store request is made to the same memory location and the requests are waiting for service simultaneously. This is because the fetch request has been given priority over the store request. An access hazard detection and resolution scheme is required to prevent the memory requests from being serviced out-of-sequence. A software solution is chosen by the MAP-200 system to solve the problem.

For this purpose, the APS has an instruction that allows it to wait on the WAF to become empty. The APS can use this instruction to ensure that a fetch request will not be issued until the store request in the WAF is transferred to memory. Thus, whenever there is a potential access hazard, the APS will not place a fetch request into the RAF until the WAF is empty. However, since every store creates a potential access hazard, the compiler for the MAP-200 needs to be efficient in detecting access hazards; otherwise, the load and store operations will be serialized and the parallelism obtained through decoupled computation will be reduced.

## 2.4. Summary and Discussion

The review of previous research and existing memory systems led to the formulation of the following features to be considered for the proposed memory system for the decoupled architecture in this dissertation.

The first important feature is that the memory system must be interleaved, so that memory bandwidth can be increased to match the speed of processing units. Second, the use of conflict queue to buffer conflicting requests can make the effective bandwidth of the interleaved memory system to be a *linear* rather than a square root function of the interleaving factor. However, the use of conflict queues creates a sequencing problem when the order of data fetched from memory is not the same as the order of its original arrival (which, of course, is precisely when the conflict queue is used). Thus, a bookkeeping scheme must be used to correct this problem. On the other hand, if the memory request are serviced in the arrival order, the operands can be fetched and stored in data queue in the correct order without re-ordering. In addition, access hazard detection is not necessary. Thus, the control logic for servicing requests in the arrival order can be very simple. The performance difference of servicing request in order and out of order will be investigated in this research.

Third, multiple-words-returned-per-fetch techniques can be used to match the memory bandwidth with the processor speed. The only shortcoming of multiple-words-returned-per-fetch scheme is that data can be fetched but not used. Since the needed data is the only data allowed in the operand queue, the fetched data must be screened so that only the needed data is placed in the operand queue (an exception is made for an instruction fetch request, where a complete cache

line is fetched).

Memory access hazards must be checked in order to prevent out-of-sequence fetch/store to the same memory location from occurring. Categorization of the techniques to detect and resolve memory access hazards in existing memory systems are as following: