# Performance Evaluation of the PIPE Computer Architecture

by

Jian-tu Hsieh Andrew R. Pleszkun James R. Goodman

Computer Sciences Technical Report #566 November 1984

## Performance Evaluation of the PIPE Computer Architecture

Jian-tu Hsieh, Andrew R. Pleszkun and James R. Goodman

Computer Sciences Department University of Wisconsin 1210 W. Dayton St. Madison, WI 53706

#### 4BSTRACT

PIPE (Parallel Instruction and Pipelined Execution) is a high performance computer architecture with several features that make it well-suited for VLSI implementation. A PIPE machine consists of a memory controller and two co-processors. An execute processor computes operand addresses for the execute processor that performs the main calculations of a program running on the PIPE system. To study PIPE's performance, we implemented a simulator through which we ran a set of hand-coded benchmarks. The dependence of performance on both program and hardware characteristics is investigated. Various parameters and execution modes of the PIPE architecture are considered. Simulation results demonstrate the usefulness of architectural queues and decoupled architectures. Simulation results also show that the PIPE architecture performs very well on the benchmark programs.

## **Table of Contents**

| ١. | Introduction                                       | 1  |

|----|----------------------------------------------------|----|

| 2. | The PIPE Architecture                              | 2  |

| 3. | . The Simulation Tools                             | 4  |

|    | 3.1. The Simulation Language Simpas                | 5  |

|    | 3.2. The PIPE Processors                           | 7  |

|    | 3.2.1. The Instruction Unit                        | 7  |

|    | 3.2.2. The Execution Unit                          | 8  |

|    | 3.2.3. The Busses                                  | 9  |

|    | 3.2.4. The Issue of Instructions                   |    |

|    | 3.3. The Memory Subsystem                          | 12 |

|    | 3.3.1. The Memory Modules                          | 12 |

|    | 3.3.2. The One-by-One Service Strategy             | 12 |

|    | . The Benchmarks                                   | 14 |

| 5. | PIPE Performance for the Lawrence Livermore Loops  | 16 |

|    | 5.1. Parameters and Execution Modes                | 16 |

|    | 5.1.1. The Parameter Sets                          | 17 |

|    | 5.1.2. The Execution Modes                         | 19 |

|    | 5.2. Program Characteristics                       | 24 |

|    | 5.2.1. The Load Distance                           | 25 |

|    | 5.2.2. The Branch Count                            | 27 |

|    | 5.2.3. The Loop Sizes                              | 29 |

|    | 5.2.4. The Read-After-Write Hazards                | 31 |

|    | 5.2.5. Long Instructions versus Short Instructions | 34 |

|    | 5.2.6. Accessing Array Elements                    | 36 |

|    | 5.2.7. Code Balancing                              | 36 |

|    | 5.3. Hardware Characteristics                      | 37 |

|    | 5.3.1. The Output Queue                            | 38 |

|    | 5.3.2. The Request Queue                           | 39 |

|    | 5.3.3. The Load Data Queue                         | 40 |

|    | 5.3.4. The Branch Queue                            | 41 |

|    | 5.3.5. Result Bus Scheduling                       | 42 |

|    | 5.3.6. The Bus Utilizations                        | 43 |

|    | 5.3.7. The Memory Modules                          | 45 |

|    | 6. Conclusion                                      | 49 |

| 7  | 7. Acknowledgement                                 | 50 |

| _  |                                                    | 51 |

#### 1. Introduction

PIPE (Parallel Instruction and Pipelined Execution) is a decoupled computer architecture with several features that make it well suited for VLSI implementation. PIPE was first proposed in [SPKG83] as a research vehicle for studying high performance VLSI architecture and organization. Since then, a great amount of effort has been devoted to the study of various aspects of this architecture. The PIPE processor is intended for state-of-the-art single-chip VLSI fabrication. The design of a prototype PIPE processor was described in [CGKP83]. Several major portions of the processor have been laid out in nMOS technology and submitted for fabrication and many software tools have been developed for studying the PIPE architecture.

Very Large Scale Integration (VLSI) is the current trend in computer technology [MeCo80]. A very powerful single-chip processor is a good candidate for use of the large number of electronic devices provided on a silicon chip [PaSe80]. Well-established pipelining design philosophy [Kogg81. RaLi77] and VLSI technology are a good match. A pipelined computer organization requires more logic than a serial one, but it does not necessarily require more interface pins. The additional logic required for pipelining contributes significantly to system performance by allowing parallel execution in the pipeline stages.

High performance machine design should exploit parallelism at all system levels, both within processors and among processors. PIPE is a decoupled architecture that allows parallel execution of a single task in two processors. A decoupled architecture provides a clean partition of computing functionals so that they can be implemented in two cooperating processors. Communication among the processors and the main memory is buffered by architectural queues that smooth out temporary congestion in busses and allow "elastic" coupling between the two processors.

To validate the features of the PIPE architecture, we decided to perform detailed simulation of the system. For such a study, a functional interpreter and performance simulator were implemented. In order to justify the design rationale and to identify possible weaknesses of the PIPE architecture, we decided to evaluate the performance of the PIPE system in a particular application environment.

To this end, we used the Lawrence Livermore Laboratories loops [McMa72] as benchmark programs.

The rest of the paper is organized as follows. In the next section, we give more details of the PIPE architecture. Section 3 describes the performance simulator and some implementation details of a PIPE system. As benchmarks, we used hand-coded Lawrence Livermore loops and these are discussed in Section 4. Simulation results of the Lawrence Livermore loops are presented in Section 5. We also analyze the results and discuss some programming techniques and performance/ hardware trade-off. Section 6 contains a conclusion.

### 2. The PIPE Architecture

The PIPE (Parallel Instruction and Pipelined Execution) architecture is intended for very-high-performance VLSI computers. The architecture, the motivation behind it, and some of the features of its planned implementation are discussed in [SPKG83]. More details on implementing a prototype PIPE processor are described in [CGKP83]. In this section, we briefly describe the important features of PIPE and some related architectures. More implementation details will be discussed in a later section, in conjunction with the PIPE simulator.

Some known impediments to computer performance have been taken into consideration in the design of the PIPE architecture. In a conventional von Neumann architecture, the CPU interacts with one memory over one bus. Both instructions and operands are transferred via this bus. In the VLSI environment, bus width is usually limited to the processor's word size. The speed of bus communications is limited by the power-delay product [MeCo80] of the circuit. The von Neumann bottleneck is the limitation on the bus traffic posed by the bus bandwidth. An on-chip instruction cache is implemented for each PIPE processor to reduce the number of words passed through this bottleneck [Good83]. Flynn [Flyn66] observed that in the instruction fetch/decode path there is some bottleneck through which instructions pass at the maximum rate of one per clock period. Decoupled architectures, with their two parallel instruction streams, reduce the constraint of the Flynn bottleneck.

PIPE is a Register-to-Register (RR) architecture in which all the operands of arithmetic and logical instructions come from registers or queues. Similarly, the operation results go to registers or queues. Load and Store are the only instructions that access main memory. Since the resource and time requirements of register-to-register operations are known in advance, RR architectures are better suited for pipelining than memory-oriented architectures.

Some processors have simple instruction sets. The argument for these processors is that they are easy to design and implement, and can execute instructions quickly. For example, the Reduced Instruction Set Computer, RISC-I [PaSe81], has a 400ns cycle time and can execute one instruction per cycle. In the pipelined implementation of a PIPE processor, an instruction may take several clock periods to finish, but we can issue one instruction per clock period. A PIPE processor has an elemental instruction set similar to that of RISC-I. An elemental instruction is one whose resource requirements can be readily determined before instruction execution. Pipeline conflict detection and interlocks can be done in a single instruction issue stage that precedes the execution pipeline. The instruction issue stage for an elemental instruction set can be implemented with relatively simple logic. Using nMOS technology, a PIPE processor is expected to have a basic clock period which is about an order of magnitude shorter than the RISC-I cycle time.

The main feature of decoupled architectures is a high degree of decoupling between operand access and execution. This results in an implementation which has two separate instruction streams and processors that communicate via queues. The MAP-200 array processor [CoSt81] proposed the first decoupled architecture in the literature. The MAP-200 has an integer addresser separate from its floating-point arithmetic unit. The two units run independently except that some synchronization is needed at certain points, such as the end of a loop. Software is called on to do most of the coordination and synchronization between these two units. Another decoupled architecture based on CRAY-1 computers [Russ78] was proposed in [Smit82]. It tried to remove the burden of synchronization from the programmers. This architecture uses queues to pass branch decisions between the cooperating processors and eliminates some unnecessary waiting periods suffered in the MAP-200

architecture. The Structured Memory Access (SMA) architecture [Ples82, PlDa83] also falls in the category of decoupled architectures. It uses a computation processor and a decoupled memory access processor with special hardware for efficient accessing of program and data structures and for effective branch and loop management.

PIPE is similar to the decoupled architectures described above, but with special considerations for pipelined VLSI implementation. Although a single PIPE processor can execute a program by itself, we are more interested in the decoupled configuration where two processors execute a single process divided into two parallel instruction streams. The Access Processor (AP) computes operand addresses and makes memory references for the Execute Processor (EP) that performs the main calculations of a program. Each processor has an on-chip instruction cache that reduces the effect of the von Neumann bottleneck. Both the instruction fetch unit and the Arithmetic Logical Unit (ALU) are pipelined. The Prepare to Branch (PBR) instructions are designed to facilitate smooth transfer of control. A PBR instruction gives the instruction fetch logic advance notice of a branch and minimizes its interruption of the instruction unit pipeline.

A memory control unit serves both processors and is responsible for detection and resolution of memory hazards. All memory transactions in a PIPE system are buffered by hardware queues. These queues allow memory access time to be overlapped with useful processing. The branch queues between the two processors provide elastic coupling between the two processors' execution. Thus a decoupled architecture automatically performs some code scheduling between the two processors at run time. The intent of a decoupled architecture is that the access processor should run ahead of the execute processor and reduce or eliminate observed memory delay.

### 3. The Simulation Tools

Many software tools have been developed for studying the PIPE architecture. Among them are a Pascal compiler, a code scheduler, an assembler, a functional interpreter, and a performance simulator. All these tools work for both single-processor and decoupled access/execute modes.

The interpreter takes PIPE object code as input, interprets it on an instruction-by-instruction basis and produces both text and binary trace files. The binary trace files contain the following information for performance simulation:

- (1) addresses of data reads.

- (2) addresses of data writes.

- (3) addresses of instruction reads.

- (4) the instructions.

A very versatile cache simulator has been developed that uses this binary trace format and has been used extensively in studying the cache organizations with PDP-11 and VAX traces [Good83, SmGo83]. This simulator can be modified slightly to add hit/miss tags to the PIPE instructions in the binary trace files. Currently, however, the PIPE simulator only has a simple built-in instruction cache simulator that simulates a direct-mapped cache.

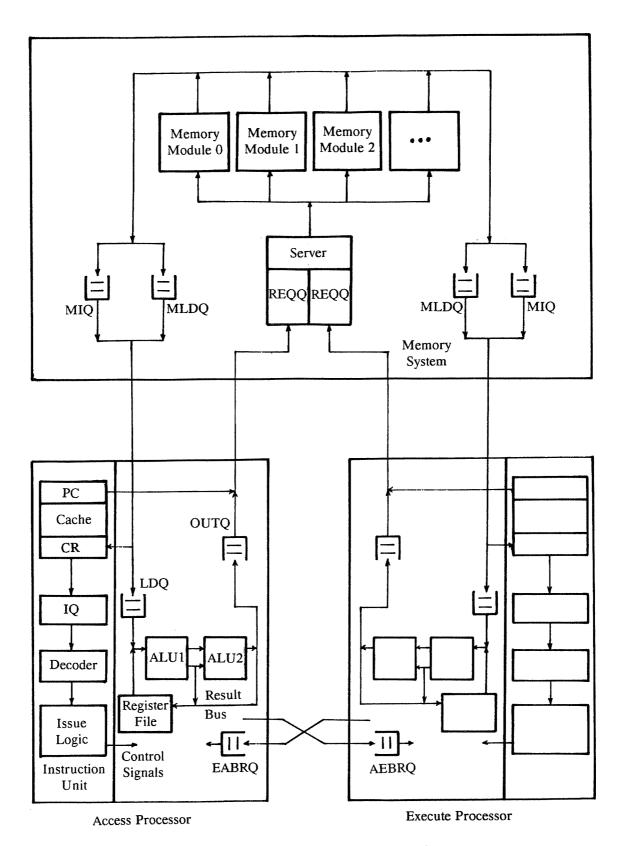

The PIPE simulator takes binary trace files as input, simulates the execution of a PIPE program on a clock-by-clock basis, and finally prints the statistics gathered during the simulation. The remainder of this section discusses the simulator in more detail. Detailed knowledge of the simulator, its operation, and its implicit assumptions is necessary for proper interpretation of the results in Section 5. Section 3.1 introduces the simulation language we used to implement the PIPE performance simulator. We use the model illustrated in Figure 3.1 to simulate a PIPE computer system. The system consists of two cooperating processors and a memory subsystem which services both processors. Section 3.2 discusses the simulation model for a PIPE processor. Section 3.3 describes a simple model for the memory system.

## 3.1. The Simulation Language Simpas

The PIPE simulator is written in the simulation language Simpas, version 5.0 [Brya83]. Simpas is an event-oriented simulation language embedded in Pascal. It has many attractive features.

First of all, it is extremely portable. It is implemented as a preprocessor that accepts an extended version of Pascal as input and produces a standard Pascal program as output. The preprocessor itself is written in standard Pascal, and the language has been designed so that it depends only

Figure 3.1. The block diagram for a PIPE machine.

on standard Pascal features.

Secondly, the language supports queues and operations on queues. This makes the simulation of the PIPE architectural queues very easy. The language also supports some error-detection at run-time. For example, it detects the error of having an element in two queues at the same time.

Finally, Simpas has automatic mechanisms for statistics collection. In order to gather statistics about an interested variable, a programmer simply specifies it to be of *watched* type. The preprocessor will generate appropriate code to collect statistics for watched variables. Since the change from a regular variable to watched variable, and vice versa, is very easy, we can make such changes during the development of a simulator depending on the execution efficiency and the amount of statistics needed.

The simulator used for this study was implemented in about 2,000 lines, excluding comments, of Simpas code. The simulator executes on a VAX-11/750 at the speed of about 30 ms user and system CPU time per PIPE clock cycle in decouple-mode simulation.

### 3.2. The PIPE Processors

The processor functions that we simulate are based on the proposed initial implementation of the PIPE processors [CGKP83]. The access processor and the execute processor can be identical: they are in fact simulated by the same procedure. However, we do not preclude the possibility of using two different processors. The simulator maintains two separate sets of simulation parameters for the processors and allows a user to specify each parameter independent of the others.

### 3.2.1. The Instruction Unit

A PIPE instruction consists of either one or two 16-bit parcels. The instruction unit is responsible for supplying an instruction stream for the ALU to execute. In order to reduce the number of accesses it makes to main memory, the instruction unit contains an on-chip instruction cache. Upon a cache hit, a line of instructions is loaded from the cache into the Cache Register (CR). Upon a cache miss, the miss address is sent to the memory control unit and the returned instructions are

assembled into a line in the CR. The instructions are processed through a pipeline consisting of the CR, the Instruction Queue (IQ), the decoder and the issue logic.

The branch instructions in the PIPE architecture are designed to minimize their interruption of the instruction unit pipeline. Branch target addresses are loaded into branch registers by separate instructions. A 'Prepare to Branch' (PBR) instruction specifies: (1) a condition to test. (2) a branch register, and (3) a 3-bit branch count. The branch count ranges from 0 to 7 and specifies the number of instruction parcels to execute before the branch is taken. Well-written programs keep the branch counts large, allowing the processor to gracefully change control flow.

In order to supply a smooth instruction stream, the instruction unit prefetches a line of instructions into the CR if the line will definitely be used. The decision is based on the early detection and partial decoding of PBR instructions. When the outcome of a branch condition is not yet known, a cache miss beyond the branch count will not be processed.

The bus width in VLSI processors is limited by the number of pins available on a package. The speed of bus communications limits the clock of the on-chip logic. The bus bandwidth also generates a potential bottleneck in the PIPE system. The PIPE architecture's prefetching strategy and small cache line size are designed to avoid unnecessary memory accesses.

## 3.2.2. The Execution Unit

The simple instruction set [PaSe81] of PIPE allows a well-structured pipelined implementation of the Arithmetic Logic Unit (ALU). The simulator assumes that the ALU is a two-stage pipeline. The first stage takes operands from the register file, the Load Data Queue (LDQ), or the instruction unit (immediate operands). Both stages can send data through the result bus to the register file or the Output Queue (OUTQ).

The Load Data Queue (LDQ) is the most important architectural queue in the PIPE architecture. It serves as a First-in First-out buffer for the data loaded by the *Load* instructions. The size of the LDQ is a simulation parameter. Ideally we like the queue to be infinitely long. So a large

number of Load instructions can be scheduled ahead of the instructions that use the data. The effect

of the LDQ size on the system performance will be studied in later sections.

3.2.3. The Busses

Each processor communicates with the Memory Control Unit (MCU) through two dedicated

busses, one for input and one for output. Bus communications are buffered by the queues on both

sides of the busses. Tags are associated with all the bus traffic and designate the kind of information

being transferred.

The MCU-to-CPU tags are:

data: A data word loaded by a Load instruction has returned from the MCU. It should go to

the LDQ.

(2) instruction: An instruction requested by a cache miss has returned. It should go to the Cache

Register in the instruction unit.

control: A control message is sent through the bus. One possible control message is that the

bus is idle. Other kinds of control messages are used to coordinate the MCU-CPU communi-

cations and will be discussed shortly.

Each processor conceptually contains the following queues:

LAQ: load address queue,

ALAQ: alternate load address queue.

SAQ: store address queue, ASAQ: alternate store address queue,

SDQ: store data queue.

Physically all these queues are combined into a single queue called the Output Queue (OUTQ).

Cache-miss instruction addresses can be thought of as going through an Instruction Address Queue

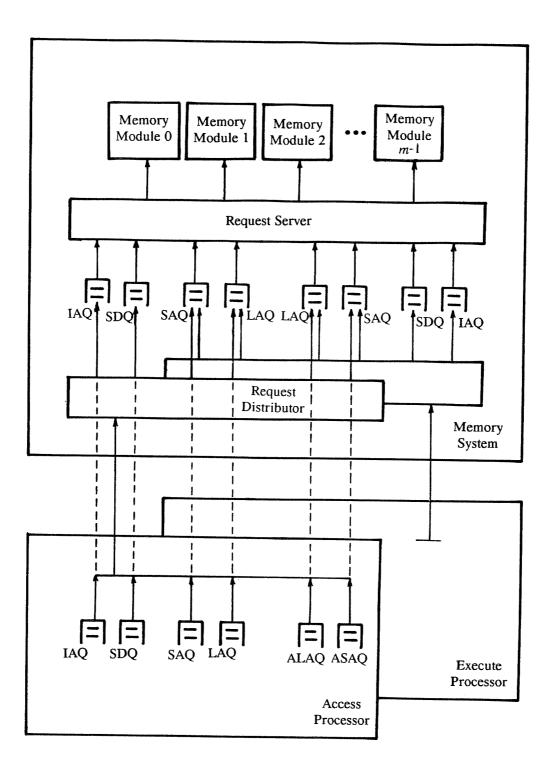

(IAQ). These queues are illustrated in Figure 3.2.

The data or addresses in the OUTQ are sent to the memory control unit in a strict first-in

first-out order. In the event of a cache miss, the instruction address is sent through the same CPU-

to-MCU bus. By default the simulator gives priority to the instruction address. The simulator

-9-

Figure 3.2. Memory request queues in a PIPE machine.

provides an option that deprives the instruction address of its priority and forces it to enter the OUTQ and wait for transmission to the MCU.

All the CPU-to-MCU bus traffic is also tagged with a source queue indicator. Another tag on the bus is for control messages. When the LDQ of a processor is full, the processor has to inform the MCU so that no more data will be sent to the LDQ. Similarly, a processor has to inform the MCU when the LDQ is not full and can be refilled. The LDQ-refill and LDQ-full messages can be considered as the set and reset signals to a flip-flop in the MCU. The MCU sends LDQ data only if the flip-flop is set. The LDQ-full message is the most urgent signal. In order to avoid any loss of data, it is given the highest priority to use the CPU-to-MCU bus. Usually the LDQ-refill message is not urgent and can be delayed if necessary. The LDQ-low parameter of the simulator is used to determine when to send the LDQ-refill message. If the LDQ length is less than LDQ-low then the LDQ-refill gets priority. Otherwise the LDQ-refill message is postponed unless the CPU-to-MCU bus is idle and can be used freely for this message.

A similar mechanism is used to control the MCU-to-CPU bus transmission. The control messages sent by the memory control unit are named REQQ-full and REQQ-refill.

## 3.2.4. The Issue of Instructions

PIPE and the CRAY-1 have similar philosophies about instruction issue: resources needed by an instruction are reserved at issue time [Cray79]. If an instruction to be issued would conflict with an already issued instruction in the execution pipeline, the instruction is blocked until the conflict is removed. In the PIPE architecture, possible reasons for blocking the instruction issue are:

- (1) instruction not available,

- (2) LDQ empty.

- (3) OUTQ full.

- (4) result bus contention,

- (5) output BRQ full, and

- (6) input BRQ empty.

The last two reasons are only for decoupled-mode executions where one processor has to wait for the other at some synchronization point. The simulator keeps a record of all these blockings. Such

information is very useful in identifying possible bottlenecks in a PIPE program or the PIPE machine.

## 3.3. The Memory Subsystem

The memory subsystem consists of the Memory Control Unit (MCU) and several memory modules. Design of a memory subsystem for PIPE and the study of various memory service strategies are in progress [Liou84]. A simple one-by-one memory service strategy is implemented as an integral part of the PIPE performance simulator.

## 3.3.1. The Memory Modules

PIPE's memory modules are interleaved for high performance: low order interleaving is used. If there are m memory modules then the memory word at address n resides in module  $n \mod m$ . In real memory systems the number m is usually a power of two so that the least significant bits of an address determines which module the memory word resides in.

The simulator allows any number of memory modules in the memory system. If the number of memory modules is specified to be zero then the simulator ignores memory module conflicts and treats all the memory requests as pure delay of the amount specified by the memory access time unless the request is blocked by hazards (to be described below). This feature can be used to study the effect of memory module conflicts.

## 3.3.2. The One-by-One Service Strategy

Figure 3.1 shows that, in the memory system, all the requests are buffered in the Request Queues (REQQs) before they are serviced. In fact, the requests cannot be serviced in a strictly first-in first-out order. For example, an unmatched store address should not block the subsequent load requests. Figure 3.2 shows one way to avoid such blockings. As illustrated, the incoming bus traffic is distributed into various buffer queues according to the associated tags. An alternate load/store address from one processor is considered as a load/store address for the other processor. The dashed lines in the figure show the virtual paths between the pairs of queues. All the virtual

paths are concentrated into a single physical bus (and therefore necessitating the use of tags).

An address from the Store Address Queue (SAQ) and a data word from the Store Data Queue (SDQ) are matched by the server and are serviced as a single write operation. In order to detect possible Read-After-Write (RAW), Write-After-Read (WAR) or Write-After-Write (WAW) hazards, each request is time-stamped when it enters the memory control unit. The time stamp for a write operation is that of the SAQ element. In addition to the RAW, WAR and WAW hazards, there are also MLDQ hazards which will be discussed shortly.

Three general rules are observed in the memory system.

- (1) Unmatched SAQ or SDQ elements must wait for their mates.

- (2) Any request whose intended memory module is busy must wait.

- (3) Any request that can cause hazards must wait.

Two more rules are enforced by the one-by-one memory service strategy.

- (4) The requests in each separate queue are serviced in a strict first-in first-out order.

- (5) If two or more requests are ready to be serviced then the one with earlier time stamp has priority.

An exception to the last rule is that the simulator gives instruction requests higher priority by default. The priority can be canceled optionally. The fourth rule insures that the data are returned to the processors in their original requested order. If some sequencing mechanism can guarantee the same effect then this rule can be lifted. The return order is important for instructions and the LDQ elements. The benefit of issuing requests out of order is studied in [Liou84].

The data read from the memory modules are buffered in the Memory Load Data Queue (MLDQ) or the Memory Instruction Queue (MIQ) and are sent to the processor through the bus. The simulator gives priority to instructions. Since there is at most one outstanding cache miss, the length of the MIQ is bounded by the cache line size. The MLDQ is essentially an extension of the LDQ. Since the MLDQ is of finite size, an MLDQ-overflow hazard will occur if a load request tries

to send data to a full MLDQ. The third rule above prevents such a request from being issued

The simulator keeps track of the number of outstanding memory requests from each processor A control message is sent to the processor when certain limits are reached. The limits for such REQQ-full and REQQ-refill control messages are simulation parameters.

#### 4. The Benchmarks

The Lawrence Livermore Laboratories (LLL) loops [McMa72] are often used to measure the performance of computer systems. They are CPU-limited numerical computations extracted from scientific application programs and involve floating-point operations on arrays of one or more dimensions. Since the floating-point operations and data format are not fully defined in the PIPE architecture, in this study we treat all variables as integers. Under this restriction the study of some of the loops is not practical because they involve conversions between floating-point numbers and integers. In this study we hand-coded the first twelve loops and use the PIPE simulator to simulate their execution.

The LLL loops are originally coded in FORTRAN as DO loops. We translated the loops into Pascal and used the PIPE Pascal compiler and code scheduler to generate PIPE code. The translation was straightforward but the compiled code was inefficient. The simulation results shown in Table 4.1 can be used to compare hand-coded and compiled code. The execution times are measured in terms of the basic clock cycle of a PIPE machine. The last column shows the ratios between the execution times for the single-processor mode and the decoupled access/execute mode. The compiler generates inefficient code for accessing array elements. This is indicated by the results for loop 8, which operates on many three-dimensional arrays. Efforts to write an optimizing PIPE Pascal compiler are underway [Youn84]. (An improved PIPE Pascal compiler is available at the time of this writing.)

We feel that a performance study based on inefficient code may not be fruitful and its results may be misleading. Therefore, we hand-coded the first twelve LLL loops. The following rules guided our coding work for the single-processor mode of execution.

|                                           | SP    |              | AE          |             |                |              |         |  |

|-------------------------------------------|-------|--------------|-------------|-------------|----------------|--------------|---------|--|

| Program                                   | #inst | exec<br>time | AP<br>#inst | EP<br>#inst | total<br>#inst | exec<br>time | Speedup |  |

| LLL1 hand-written code LLL1 compiled code | 4009  | 4069         | 2406        | 2005        | 4411           | 2859         | 1.423   |  |

|                                           | 13609 | 18125        | 14409       | 2804        | 17213          | 16138        | 1.123   |  |

| LLL2 hand-written code LLL2 compiled code | 8005  | 11053        | 5604        | 3603        | 9207           | 6851         | 1.613   |  |

|                                           | 14809 | 20422        | 20809       | 2804        | 23613          | 27882        | 0.732   |  |

| LLL8 hand-written code LLL8 compiled code | 3330  | 3564         | 1412        | 1726        | 3138           | 1894         | 1.882   |  |

|                                           | 14115 | 16815        | 19994       | 1653        | 21647          | 32643        | 0.515   |  |

Table 4.1. Comparison of hand-written and compiled code for some LLL loops.

- (1) The original loop structure is maintained. A Prepare to Branch (PBR) instruction at the end of the loop tests the termination condition and branches to the head of the loop when appropriate.

We tried to maximize the branch count in the PBR instruction.

- (2) As long as free registers are available, the loop-invariant quantities are kept in registers. These registers are loaded before the loop is entered. Similarly the branch target address is loaded into a branch register only once before the loop is entered.

- (3) All Load instructions appear at the beginning of the loop in order to hide the memory access delay. However, this loading strategy may fill up the queues and cause deadlock in the single-processor mode, especially if the queues are short. In some loops it is necessary to intersperse the load instructions in the loop body to avoid deadlock.

- (4) Loop indices are kept in registers and are updated at the end of each iteration. We don't store the final index value into main memory because usually the loop index is only for controlling the loop iteration. Variables for storing intermediate results are treated similarly.

- (5) The index-addressing mode is used to access array elements efficiently. Loop 8 is an example where we access multi-dimensional array elements gracefully.

All these rules are very simple and can be applied to compiler-generated code. Therefore, our code also serves as a guideline for compiler writers and provides a means for comparison. The code for the single-processor mode of execution can be split naturally into two streams for the decoupled mode of execution. The access processor is responsible for memory accessing and loop control. The execute processor performs the arithmetic operations and follows the access processor's branch decisions.

Loop 3 is the simplest of all the loops we studied. The Pascal source program, the annotated single-processor code, and the decouple access/execute code are shown in Figure 4.1. The 'L' and 'S' prefixes in the opcode field designate long and short instructions, respectively. Register 7 represents either the head of the Load Data Queue (LDQ) or the tail of the Store Data Queue (SDQ). The ZBR pseudo opcode marks the location where a branch takes place if the condition tested by the antecedent Prepare to Branch (PBR) instruction is true. No code is generated for a ZBR.

The simulation results for these loops will be presented in the next section. Special coding techniques for improving system performance will also be discussed.

## 5. PIPE Performance for the Lawrence Livermore Loops

Using the PIPE simulator, we simulated the execution of the first twelve Lawrence Livermore Laboratories (LLL) loops [McMa72] (also see Appendix A) under various execution modes and system parameters. Section 5.1 presents the general simulation results. Program characteristics of the loops and their influence on system performance are discussed in Section 5.2. Dependence of the performance on hardware configuration and speed is studied in Section 5.3.

## 5.1. Parameters and Execution Modes

Two basic parameter sets and three execution modes are used in our simulation of the first twelve Lawrence Livermore loops. The parameter sets are specified in Section 5.1.1. The execution modes are discussed and compared in Section 5.1.2. Simulation results of the LLL loops in each mode and using each parameter set are also presented and briefly discussed.

```

q := 0;

for k:= 1 to 1000 do

q := q + z[k] * y[k].

```

#### (a) Pascal source program

```

1.

-1000+1

/* Rl for loop index k-1000.

LENTER

1

/* R2 for q, initialized to Ø.

2.

SXOR

2

Ø

Ø

/* Load branch register.

3.

LLDBR

Ø

ALOOP

4.

ALOOP

Z+1000-1 /* LDQ <-- z[k].

5.

LLDLN

/* Loop back if Rl < Ø.

SIPBRLT

6.

1

Ø

Ø

Y+1000-1 /* LDQ <-- y[k].

7.

LLDLN

1

/* Increment loop index by 1.

8.

LADDIM

1

1

/* R3 \leftarrow z[k]*y[k].

9.

SMULI

3

7

/* R2 <-- R2 + z[k]*y[k].

2

lØ.

SADDI

2

3

11.

ZBR

/* Branch taken here.

/* Generate store address for q.

12.

LSTLN

Q

2

/* Store the value of q.

13.

SMOVNFF 7

```

(b) PIPE assembly code for single-processor mode

| access processor     | execute processor |   |

|----------------------|-------------------|---|

|                      |                   |   |

| 1. LENTER 1 -1000+1  | 1. SXOR 2 Ø Ø     |   |

| 2. LLDBR Ø ALOOP     | 2. LLDBR Ø ELOC   | P |

| 3. ALOOP             | 3. ELOOP          |   |

| 4. SPBRLT 1 Ø Ø      | 4. SIPBRQ Ø Ø Ø   |   |

| 5. LALDLN 1 Z+1000-1 |                   |   |

| 6. LALDLN 1 Y+1000-1 | 5. SMULI 3 7 7    |   |

| 7. LADDIM 1 1        | 6. SADDI 2 2 3    |   |

| 8. ZBR               | 7. ZBR            |   |

| 9. LASTLN Ø Q        | 8. SMOVNFF 7 2 Ø  |   |

(c) PIPE assembly code for decoupled access/execute mode

Figure 4.1. Pascal and PIPE assembly code for LLL loop 3.

#### 5.1.1. The Parameter Sets

Although the simulator has the capability of specifying distinct parameters for individual processors, the access processor and the execute processor in our simulation are assumed to be identical unless otherwise specified. The instruction cache has a fixed line size, 4 instruction parcels. We assume that the instruction cache is big enough to accommodate the code for each loop. In fact, 16

cache lines are enough for each of the loops except loop 8 in single-processor mode, which needs 32 lines. Two basic parameter sets are used in the simulation and are summarized in Table 5.1. The first set consists of the default parameters of the simulator. Following are the important parameters in this default parameter set.

- (1) LDQ size = MLDQ size = OUTQ size = REQQ size = BRQ size = 4. Refill points for LDQ and REQQ are the same as the queue sizes; that is, a refill signal is sent as soon as an element is removed from a full queue.

- (2) The memory module access time is one clock period. For such a fast memory module, there is no memory module conflict at all. Therefore, there is no need for interleaving. Including the overhead incurred in the memory control unit, the minimum effective memory delay seen by a processor is 3 clock periods.

- (3) Addresses for instruction cache misses have priority in the OUTQ but not in the REQQ

Since the basic clock period for a pipelined machine is very short, it seems unrealistic to assume that the memory module access time is only one clock period. Our second parameter set

|                                                  | default | empirical |

|--------------------------------------------------|---------|-----------|

| LDQ, OUTQ, BRQ                                   | 4       | 4         |

| MLDQ, REQQ                                       | 4       | 8         |

| LDQ-low, REQQ-low                                | 4       | 4         |

| Number of memory modules                         | (1)     | 4         |

| Memory access time                               | 1       | 4         |

| Memory turnaround time                           | 3       | 6         |

| Instruction fetch requests have priority in OUTQ | yes     | yes       |

| Instruction fetch requests have priority in REQQ | no      | yes       |

Table 5.1. The default and empirical parameter sets.

assumes slower memory, more modules, and longer queues. We call it the empirical parameter set.

The important parameters are the following.

- (1) LDQ size = OUTQ size = BRQ size = 4. MLDQ size = REQQ size = 8. Refill points for both the LDQ and the REQQ are 4; that is, the refill signal must be sent when the queue length changes from 4 to 3, or earlier.

- (2) The memory module access time is 4 clock periods. The effective memory latency seen by a processor is 6 or more clock cycles. There are four interleaved memory modules. The least significant two bits of an address determine in which module the memory word resides.

- (3) Addresses for instruction cache misses are given priorities in both the OUTQ and the REQQ.

A memory module conflict occurs when a request tries to access a module which is busy servicing a previous request. We increase the queue sizes to buffer more requests and to allow the issue of more load requests while the previous ones are still in process. The maximum service rate for this memory system is one request per clock period, which is achieved only if the memory modules are used in a strictly cyclic pattern.

## 5.1.2. The Execution Modes

Table 5.2 shows PIPE performance for the first twelve LLL loops with default simulation parameters. The execution times and the numbers of instructions executed are listed for both the single-processor (SP) and decoupled access/execute (AE) modes. The issue rate is the quotient of the instruction number to the execution time. For AE mode, the issue rates listed in the table are for the processor which executes more instructions. The last column is the ratio of execution times, and shows the speedup of AE mode over SP mode. The last row shows the total number of instructions, the total execution times, and the averages of the issue rates and speedups. In calculating the averages, the issue rates and speedups are weighted by the execution times.

In AE mode of execution, the access processor and the execute processor execute two parallel instruction streams and are capable of issuing a total of two instructions per clock period. However,

| LLL            |       | SP           |               |             | AE          |                |              |               |         |  |  |  |

|----------------|-------|--------------|---------------|-------------|-------------|----------------|--------------|---------------|---------|--|--|--|

| loop<br>number | #inst | exec<br>time | issue<br>rate | AP<br>#inst | EP<br>#inst | total<br>#inst | exec<br>time | issue<br>rate | Speedup |  |  |  |

| * 1            | 4009  | 4069         | 98.5%         | 2406        | 2005        | 4411           | 2859         | 84.2%         | 1.423   |  |  |  |

| * 2            | 8005  | 11053        | 72.4%         | 5604        | 3603        | 9207           | 6851         | 81.8%         | 1.613   |  |  |  |

| * 3            | 6006  | 10039        | 59.8%         | 4005        | 3003        | 7008           | 5044         | 79.4%         | 1.990   |  |  |  |

| † 4            | 5610  | 5697         | 98.5%         | 4592        | 1530        | 6122           | 5681         | 80.8%         | 1.003   |  |  |  |

| † 5            | 7017  | 7425         | 94.5%         | 4011        | 3342        | 7353           | 5407         | 74.2%         | 1.373   |  |  |  |

| † 6            | 7662  | 8065         | 95.0%         | 4665        | 3332        | 7997           | 5395         | 86.5%         | 1.495   |  |  |  |

| * 7            | 3608  | 3687         | 97.9%         | 1686        | 2044        | 3730           | 2114         | 96.7%         | 1.744   |  |  |  |

| <b>‡</b> 8     | 3330  | 3564         | 93.4%         | 1412        | 1726        | 3138           | 1894         | 91.1%         | 1.882   |  |  |  |

| ‡*9            | 3909  | 4043         | 96.7%         | 1910        | 1807        | 3717           | 2002         | 95.4%         | 2.019   |  |  |  |

| *10            | 4103  | 4220         | 97.2%         | 2203        | 2002        | 4205           | 2598         | 84.8%         | 1.624   |  |  |  |

| <b>†11</b>     | 5997  | 8028         | 74.7%         | 4998        | 2000        | 6998           | 7031         | 71.1%         | 1.142   |  |  |  |

| *12            | 5997  | 8028         | 74.7%         | 4998        | 2000        | 6998           | 6035         | 82.8%         | 1.330   |  |  |  |

|                | 65253 | 77918        | 83.7%         | 42490       | 28394       | 70884          | 52911        | 81.6%         | 1.473   |  |  |  |

<sup>\*:</sup> vectorizable by CRAY FORTRAN Compiler.

Table 5.2. PIPE performance for LLL loops, with default simulation parameters.

this important advantage of the AE mode over the SP mode is often lessened by un-even splitting of the code between the two processors. Among the twelve loops we studied, loop 4 suffers the most from unbalanced code: the access processor executes about three times the instructions that the execute processor does. Incidentally, this loop has the smallest speedup, 1.003. Loop 9 has the best balanced code between the processors, and the largest speedup, 2.019, among all the loops.

PIPE instructions use 3-bit fields to designate the queue head/tail or one of the seven fore-ground registers. Loops 8 and 9 use more loop-invariant constants than a register set can accommodate. Therefore, in the SP mode of execution, some constants must be read from main memory into the LDQ every time they are used. In AE mode of execution, we have one register set in each

<sup>†:</sup> involves Read-After-Write hazards.

<sup>‡:</sup> uses many loop-invariant constants.

processor and can keep more constants handy in registers. This is the reason why the total numbers of instructions for AE mode are less than those for SP mode in these two loops.

Loop 3 executing in SP mode has the lowest issue rate in the table. The main reason is that some instructions have to wait for operands. A decoupled architecture performs some code scheduling dynamically at run time and allows both processors to run smoothly. Loop 3 executes much faster in AE mode and shows a speedup of 1.99.

The loops involving Read-After-Write (RAW) hazards are marked with "†" in the table. The loops marked with "\*" are classified as vectorizable by the CRAY FORTRAN Compiler. Notice that the loops involving RAW hazards are all non-vectorizable. However, the RAW hazards are not inherent in these tasks, and can easily be avoided. The detrimental effect of RAW hazards and how to avoid these hazards will be discussed later.

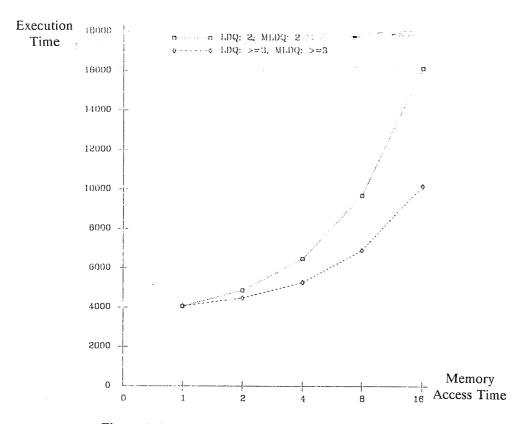

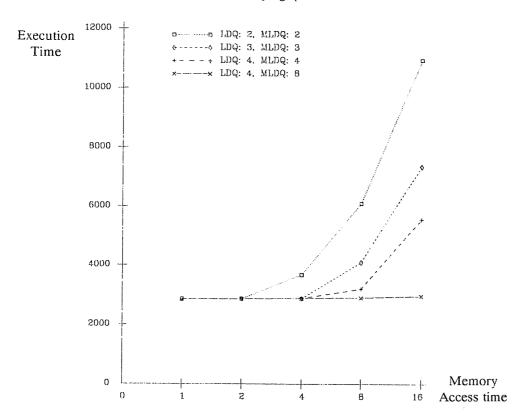

In order to see how memory speed influences system performance, we used the empirical parameter set and repeated the simulation in both SP and AE modes. The results are shown in Table 5.3. The table also shows the simulation results with the default parameter set for comparison. For the present, ignore the "MP exec time" lines. These will be discussed below. Generally speaking, a slower memory system degrades the performance. Loop 7 is an exception which executes quickly in either mode using either parameter set. The amount of degradation varies over a wide range, depending on the execution mode and the program characteristics. We can divide the loops into three categories: (1) hazard-bound, (2) scheduling-bound, and (3) memory-bound.

- (1) Hazard-bound loops. Loops 4, 5, 6 and 11 involve RAW hazards and fall into this category. A slow memory system degrades the performance significantly for both SP and AE mode of execution. Details of the degradation mechanism will be discussed in a later section.

- (2) Scheduling-bound loops. This category includes loops 1, 2, 3 and 12. Because of its dynamic-scheduling capability, the AE mode of execution suffers very little from the slow memory. On the other hand, the execution time of the SP mode increases significantly when the memory slows down. Therefore, using the empirical parameter set, loops in this category

|           |                    |       |       | 1     | оор    |        |       |

|-----------|--------------------|-------|-------|-------|--------|--------|-------|

| parameter | mode               | 1     | 2     | 3     | †4     | †5     | †6    |

| default   | SP exec time       | 4069  | 11053 | 10039 | 5697   | 7425   | 806.5 |

|           | MP exec time       | 4083  | 11061 | 10045 | 7229   | 7445   | 8415  |

| parameter | AE exec time       | 2859  | 6851  | 5044  | 5681   | 5407   | 5395  |

| set       | AE-over-SP speedup | 1.423 | 1.613 | 1.990 | 1.003  | 1.373  | 1.495 |

|           | AE-over-MP speedup | 1.428 | 1.615 | 1.991 | 1.272  | 1.377  | 1.560 |

| empirical | SP exec time       | 6483  | 17065 | 15047 | 8007   | 10453  | 11415 |

|           | MP exec time       | 8086  | 17091 | 15067 | *13577 | 10804  | 11764 |

| parameter | AE exec time       | 2879  | 6872  | 5066  | 6828   | 8424   | 8406  |

| set       | AE-over-SP speedup | 2.252 | 2.483 | 2.970 | 1.173  | 1.241  | 1.358 |

|           | AE-over-MP speedup |       | 2.487 | 2.974 | 1.988  | 1.283  | 1.399 |

|           |                    |       |       | !     | оор    |        |       |

| parameter | mode               | 7     | 8     | 9     | 10     | ÷11    | 12    |

| default   | SP exec time       | 3687  | 3564  | 4043  | 4220   | 8028   | 8028  |

|           | MP exec time       | 3708  | 3734  | 4069  | 4247   | 9033   | 9032  |

| parameter | AE exec time       | 2114  | 1894  | 2002  | 2598   | 7031   | 6035  |

| set       | AE-over-SP speedup | 1.744 | 1.882 | 2.019 | 1.624  | 1.142  | 1.330 |

|           | AE-over-MP speedup | 1.754 | 1.971 | 2.032 | 1.635  | 1.285  | 1.497 |

| empirical | SP exec time       | 3722  | 5057  | 6339  | 6462   | 13030  | 12032 |

|           | MP exec time       | 4103  | 6798  | 8513  | 6960   | *17026 | 12039 |

| parameter | AE exec time       | 2137  | 3009  | 4212  | 4839   | 13029  | 6049  |

| set       | AE-over-SP speedup | 1.742 | 1.681 | 1.505 | 1.335  | 1.000  | 1.989 |

|           | AE-over-MP speedup | 1.920 | 2.259 | 2.021 | 1.438  | 1.307  | 1.990 |

<sup>†:</sup> involves Read-After-Write hazards.

Table 5.3. PIPE performance for LLL loops with various parameters and modes.

have higher speedups than other loops

(3) Memory-bound loops. Loops 8 through 10 are in this category. The slow memory becomes the bottleneck in the system. The PIPE performance is degraded significantly for both SP and

<sup>\*:</sup> shows interference between processors.

AE mode of execution. Since the AE mode has higher memory request rate, it suffers from the slow memory more than the SP mode does: the AE-over-SP speedup decreases when the memory gets slower.

Table 5.4 shows the numbers of memory requests and the memory service rates for AE mode of simulation. The service rate is identical to the request rate, and is the quotient of the total number of requests to the execution time. The last column of the table lists the ratio of the execution times and shows the performance degradation caused by slow memory. The slowdown is negligible for the scheduling-bound loops. Using the default parameter set, the memory-bound loops have high memory request rates. However, the slow memory in the empirical parameter set can only sustain a much lower service rate. This explains the significant slowdown of the memory-bound loops. For example, the execution time of loop 9 is more than doubled with the slow memory.

In the SP mode of execution, we assumed that the memory system serviced only one processor. Another possible execution mode of a PIPE system is the Multi-Processor (MP) mode where two processors execute two independent programs and are serviced by a single memory system. The two processors then contend for memory service. Table 5.3 also shows the results of the MP mode of simulation. For each loop, we ran the same program on both processors. The two processors refer to the identical memory space, but should be considered as running two unrelated programs. Since the two processors are forced out of synchronization by the instruction cache misses, artificially introduced conflicts between them are very unlikely. However, RAW hazards may cause certain interference between the two processors' memory requests. We found two such cases, and marked them with asterisks in Table 5.3. Due to the memory contention, the execution time of MP mode is longer than that of SP mode. For the memory-bound loops, the degradation caused by slow memory is comparable for the AE and MP modes. A PIPE system can run either one program in AE mode or two programs simultaneously in MP mode. In some sense, the AE mode of execution is profitable only if the AE-over-MP speedup is 2 or more. In many applications, however, it is often preferred to be able to run one job quickly rather than to run two jobs slowly.

|                | memory |                                         |       | memory parameter set |                 |              |                 |              |  |

|----------------|--------|-----------------------------------------|-------|----------------------|-----------------|--------------|-----------------|--------------|--|

| L.L.L          |        | requests                                |       | de                   | default         |              | empirical       |              |  |

| loop<br>number | read   | write                                   | total | exec<br>time         | service<br>rate | exec<br>time | service<br>rate | slow<br>down |  |

| 1              | 1242   | 401                                     | 1643  | 2859                 | 57.5%           | 2879         | 57.1%           | 1.007        |  |

| 2              | 2036   | 200                                     | 2236  | 6851                 | 32.6%           | 6872         | 32.5%           | 1.003        |  |

| 3              | 2028   | *************************************** | 2029  | 5044                 | 40.2%           | 5066         | 40.1%           | 1.004        |  |

| 4              | 1577   | 510                                     | 2087  | 5681                 | 36.7%           | 6828         | 30.6%           | 1.202        |  |

| 5              | 2382   | 1002                                    | 3384  | 5407                 | 62.6%           | 8424         | 40.2%           | 1.558        |  |

| 6              | 2379   | 999                                     | 3378  | 5395                 | 62.6%           | 8406         | 40.2%           | 1.558        |  |

| 7              | 1138   | 120                                     | 1258  | 2114                 | 59.5%           | 2137         | 58.9%           | 1.011        |  |

| 8              | 1058   | 240                                     | 1298  | 1894                 | 68.5%           | 3009         | 43.1%           | 1.589        |  |

| 9              | 1377   | 100                                     | 1477  | 2002                 | 73.8%           | 4212         | 35.1%           | 2.104        |  |

| 10             | 1072   | 1000                                    | 2072  | 2598                 | 79.8%           | 4839         | 42.8%           | 1.863        |  |

| []             | 2022   | 999                                     | 3021  | 7031                 | 43.0%           | 13029        | 23.2%           | 1.853        |  |

| 12             | 2022   | 999                                     | 3021  | 6035                 | 50.1%           | 6049         | 49.9%           | 1.002        |  |

Table 5.4. Memory service rates for LLL loops, AE mode of execution.

## 5.2. Program Characteristics

Program characteristics strongly affect performance. Load distance and branch count are discussed in Sections 5.2.1 and 5.2.2, respectively. They are the most important factors to consider in a PIPE program. Their relationship to loop size is discussed in Section 5.2.3. We also consider some optimizing techniques for small loops. In Section 5.2.4 we study the mechanism how readafter-write hazards degrade performance. Long instructions and short instructions are compared in Section 5.2.5 with respect to their implication in performance. Section 5.2.6 discuss how to access array elements effectively. Code balancing between the processors is discussed in Section 5.2.7.

#### 5.2.1. The Load Distance

All the operands for PIPE instructions are either registers or the head of the Load Data Queue (LDQ). The LDQ serves as a first-in-first-out buffer for data which are produced by *Load* instructions and consumed as operands by other instructions. In order to allow the consumer to proceed without waiting, we have to schedule the corresponding producer ahead of the consumer. To show the importance of proper scheduling in the SP mode of execution, we recoded loop 7 so that all the operands are loaded on demand (that is, just before they are need). With the default parameter set, the execution time increases from 3687 to 9049 clock cycles. This corresponds to a decrease in the issue rate from 97.9% to 38.9%.

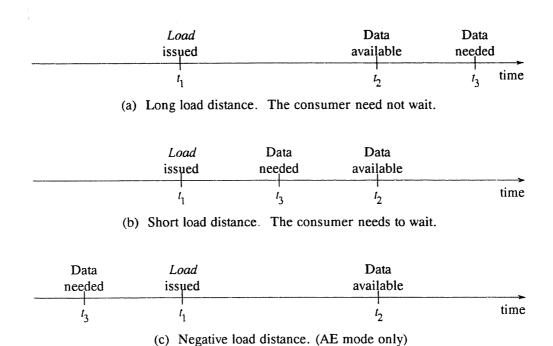

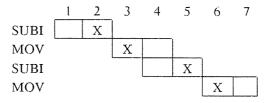

Figures 5.1 shows the timing diagrams for producing and consuming LDQ data. Assume that a Load instruction is issued at time  $t_1$ , the returned data enters the LDQ at  $t_2$ , and the data is needed by an instruction at  $t_3$ . The interval  $t_2$ - $t_1$  is the turnaround time for this load instruction. The inter-

Figure 5.1. Timing diagrams for producing and consuming LDQ data.

val  $t_3$ - $t_1$  is the time allowance for the producer to complete the load operation without slowing down the consumer. Figure 5.1(a) shows the case where the operand is available when it is needed. Figures 5.1(b) and (c) show the cases where the consumer has to wait for data.

For each load instruction in single-processor code, we try to increase the number of instructions between it and the instruction that consumes the data. This number is called the *load distance* for the load instruction. Long load distances tend to increase  $t_3$ - $t_1$  and reduce the probability or period for the consumer to wait. However, it is not always possible to have long load distances. Branch instructions may break the code into small segments so that very few instructions can be counted in the load distance. An example is the single-processor code for LLL loop 3 shown in Figure 4.1(b), where line 9 uses the data loaded by line 7.

Code scheduling in SP mode is complicated by its dependency on the hardware configuration and the memory service discipline. Following are the important factors to consider.

- (1) A sequence of load instructions with very long load distances may fill up the queues and cause deadlock. A safe instruction stream may become unsafe when the hardware configuration or characteristics change.

- (2) The turnaround time for a load operation depends on the speed and utilization of the memory system. Also it may increase significantly when there are bank conflicts or instruction cache misses.

- (3) The memory service discipline of the memory system also adds uncertainty to the turnaround times.

It is difficult to determine an optimal load distance for the SP mode of execution. However, if the hardware configuration is fixed, then we can schedule load instructions ahead as far as the queue sizes allow. By doing this, we have achieved very high issue rates in SP mode for many of the LLL loops.

In decoupled access/execute mode of execution, the code scheduling is between the instruction streams for two processors instead of within a single instruction stream. Scheduling takes place automatically at run time and suffers very little from the three problems mentioned above. When the producer (that is, the access processor) of data runs too far ahead of the consumer (that is, the execute processor), it is perfectly legal to block the access processor and allow the execute processor to proceed. Since the bottleneck is at the execute processor under this condition, blocking the access processor does not degrade system performance. The intent of a decoupled architecture is that the access processor should run ahead of the execute processor and reduce or eliminate observed memory delay. Any temporary variation in the memory turnaround time should be smoothed away in the queues.

In fact, in most of the loops we studied, the access-processor code has more instructions than the execute-processor code; therefore, the access processor does not run ahead of the execute processor. The timing diagram for the load instructions in these loops looks like the one in Figure 5.1(c). The figure, which is unique to the AE mode of execution, depicts the situation where the data are needed by the execute processor while the corresponding load instruction in the access processor has not yet issued. Therefore, the LDQ is empty most of the time; a data word is consumed by the execute processor as soon as it enters the LDQ. Our simulation results show that the average LDQ length is very small for the execute processor. The system throughput for these loops is limited by the access processor. We believe that the work load for the execute processor will increase when we add more stages to the ALU pipeline and add floating-point operation to the PIPE instruction set.

#### 5.2.2. The Branch Count

The Prepare to Branch (PBR) instructions in the PIPE architecture are designed to allow smooth control flow in program execution. It is important for a PBR instruction to have a large branch count so that enough instructions following it can proceed without knowing the branch decision. A simple technique is used in coding the LLL loops. We update the loop index at the end of the loop (that is, after the PBR instruction) to increase the branch count. Care is taken in

formulating the termination condition and in using the loop index as an index register. An example is the access-processor code for loop 3 shown in Figure 4.1(c), where line 4 is the PBR instruction and line 7 updates the loop index. The branch count would be 4 parcels instead of 6 if the loop index is updated at the head of the loop.

In order to fully utilize the processor, we should try to maintain a continuous flow of instructions through the pipeline stages. Holes in the instruction flow reduce the system throughput. Referring to the structure of the processor shown in Figure 3.1, we can count the number of instructions a branch count should cover in order to avoid holes in the instruction flow. Suppose that the first stage of the ALU executes a PBR instruction and determines that the branch condition is true. To avoid holes, there should be one instruction at

- (1) the Instruction Queue (IQ).

- (2) the decoder,

- (3) the issue logic, and

- (4) the first stage of the ALU.

while the instructions at the branch target are being fetched into the Cache Register (CR). Therefore, if a branch is taken, the branch count should cover four or more instructions in order to avoid holes in the instruction pipeline and the ALU pipeline. If the branch is not taken then the branch count should cover three or more instructions.

Some PBR instructions in the programs are not able to have a large branch count unless special coding techniques are used. The access-processor code in Figure 4.1(c) shows an example of a very small loop body that contains only three instructions (excluding the PBR instruction). The branch is taken in all iterations except the last one. The small branch count accounts for the low issue rate of loop 3 in the AE mode of execution.

The branch count is specified by a 3-bit field in a PBR instruction. A problem with this format is that the maximum branch count. 7, cannot cover 4 instructions if they are all two-parcel instructions. In our experience, most of the access-processor instructions are long *load* instructions. The branch count is 6 and covers three long instructions in the example above. If we add a long instructions

tion to the loop, it must be placed before the PBR instruction; if placed after, the branch count would be 8, greater than the maximum. In order to improve the issue rate, it is desirable to be able to specify a branch count of 8. One easy way to do this is to interpret the 3-bit branch count 0 as 8. If there is nothing to go after the PBR instruction then we pad a no-op instruction after the PBR and make the branch count 1. The no-op instruction only increases the code size by one byte and is executed free because the ALU is idle otherwise. Of course, for a different implementation some other maximum branch count may be desirable

#### 5.2.3. The Loop Sizes

The hit ratio of the instruction cache is very high in all of our simulation because the instruction cache is big enough to hold all instructions of the loop body. For a direct-mapped instruction cache, the hit ratio begins to decrease linearly when the size of the inner-most loop exceeds the cache size. It vanishes when the loop size is twice the cache size. However, large inner loops are very rare in real applications.

On the other hand, small loops are used very often and can degrade the performance significantly if not properly coded. Small loops have the following disadvantages:

- (1) The branch count of the PBR instruction is small.

- (2) The load distances are short.

- (3) The overhead for flow control is high.

The first two disadvantages are unique to the PIPE architecture and have been discussed earlier. The overhead for flow control includes updating the loop index and executing the PBR instruction. In the single-processor code for loop 3 shown in Figure 4.1(b), the loop body contains only six instructions (lines 5 through 10). The overhead (lines 6 and 8) is one third of the total instructions executed in each iteration.

Loops 3, 11 and 12 are very small. Following are some other typical uses of small loops:

- (1) initializing an array.

- (2) constructing a free list.

- (3) computing the sum of array elements,

- (4) searching for a specific value in an array.

Since small loops are used very frequently, it is important to execute them effectively. Here we consider two coding techniques for improving the issue rate of small loops: (1) software pipelining, and (2) code doubling.

The execution of loop 3 in the single-processor mode can be represented as

$$(L_{11}L_{12}WU_{11}U_{12}O)(L_{21}L_{22}WU_{21}U_{22}O) \cdot \cdot \cdot (L_{n1}L_{n2}WU_{n1}U_{n2}O)$$

where  $L_{ij}$  is the j-th load instruction in the i-th iteration,  $U_{ij}$  uses the data loaded by  $L_{ij}$ , W and O stand for 'Waiting' and 'Overhead', respectively. The waiting states are necessary because the load distances are very short. The parentheses delineate the loop structure. The loop is iterated n times.

The software pipelining technique [CoSt81. BrWe83] ravels the loop, re-arranges and regroups the instruction stream into

$$-L_{11}L_{12}(L_{21}L_{22}U_{11}U_{12}O)(L_{31}L_{32}U_{21}U_{22}O) + + (L_{n1}L_{n2}U_{n-1,1}U_{n-1,2}O)U_{n1}U_{n2}$$

The loop body remains the same size. However, including the prologue and the epilogue, the static code size is about doubled. The new loop body loads data for the next iteration and uses the data loaded by the previous iteration. This new structure effectively increases the load distances and, hopefully, eliminates the waiting states. The attainable branch count and the overhead for flow control remain about the same.

Another technique for improving the issue rate of small loops is to aggregate k consecutive iterations into a larger loop body. For k=2, this "code doubling" technique yields the following structure:

prologue

$$(L_{11}L_{12}L_{21}L_{22}U_{11}U_{12}U_{21}U_{22}O) \cdots (\cdots).$$

The prologue is used to handle special cases where the number of iterations is zero or odd. If n is odd then the first iteration of the original loop is executed in the prologue. The static code size is more than doubled. If the number of iterations is known to be even then the prologue can be omitted. The runtime overhead of the prologue is negligible when n is big. The new structure improves the issue rate by overcoming all the disadvantages listed above: it reduces the flow control overhead and increases the branch count and the load distances. We applied this technique to loop 3 and

simulated the SP mode of execution with the default parameter set. A comparison with the original results shows great improvements. The total number of executed instructions decreased from 6006 to 5016; the execution time decreased from 10039 to 5563; and the issue rate increased from 59.8% to 90.2%.

When splitting the single-processor code into two cooperating streams, we end up with two smaller loops. The overhead for flow control becomes more significant in the access processor. The execute processor has the overhead of executing the "Prepare to Branch from Queue" (PBRQ) instructions. The branch count for either the PBR or the PBRQ instructions is smaller than that in the SP mode. For loops 2, 3 and 12, the low issue rates in AE mode are caused by small branch counts in access-processor code. The code doubling technique can be applied to the decoupled mode as well.

# 5.2.4. The Read-After-Write Hazards

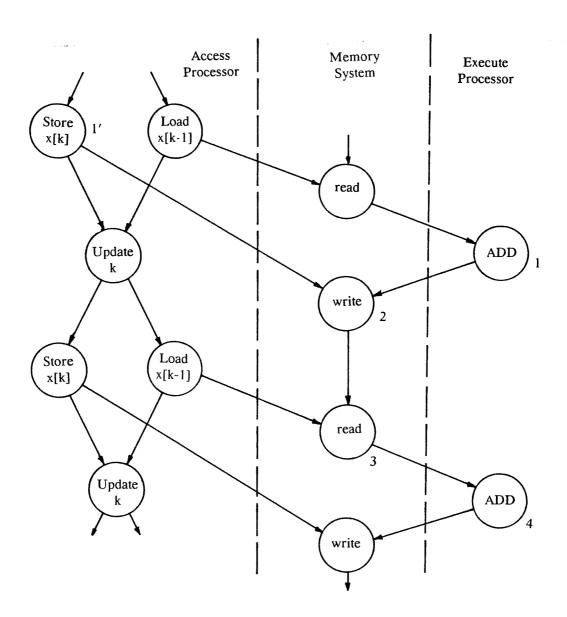

Many of the loops involve Read-After-Write (RAW) hazards and are marked with "in Tables 5.2 and 5.3. Generally, PIPE's performance of these loops are degraded by the hazards. Loops 11 and 12 are syntactically identical (see Appendix A) and provide us a good opportunity to see the effect of RAW hazards on performance. We now use loop 11 as an example and study the bad effect of RAW hazards in detail. The Pascal source code looks like

for

$$k := 2$$

to 1000 do

$x[k] := x[k-1] + y[k]$ .

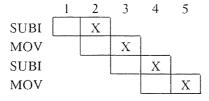

Figure 5.2 illustrates part of the activities during AE mode of execution of loop 11. The arcs in the figure denote the precedence relations among activities. For example, node 2 can execute only if both nodes 1 and 1' have finished. Nodes on a directed path must be executed in order. A *critical path* between two nodes is a directed path that has the longest execution time. For loop 11, the following nodes are on a critical path.

(1) At the end of an iteration, the execute processor sends the new value of x[k-1] to the memory control unit.

Figure 5.2. Precedence relations among activities in LLL loop 11.

- (2) This value is written to a memory location.

- (3) Due to the RAW hazards, the read operation can proceed only if the write operation has finished. Upon completion of the read operation, the value of x[k-1] is sent to the execute processor.

- (4) Once the operands enter the LDQ, the execute processor can issue the ADD instruction that computes x[k-1]+y[k].

Nodes 2 and 3 access the same memory word and must be executed in the read-after-write order. For loop 12, nodes 2 and 3 can proceed in any order because the read address is different from the write address. This is the essential difference between loops 11 and 12.

With the default parameter set, this critical path takes 7 clock periods to execute. Loop 11 traverses 999 similar paths and has an execution time close to 7000 clock periods (see Table 5.3). The execution times of both nodes 2 and 3 include the access time of the memory modules. When we change from the default parameter set to the empirical parameter set, the execution time of each node increases by 3 clock periods. Therefore, the execution time of the critical path increases form 7 to 13 clock periods: the total execution time is about 13000 clock periods. Incidentally, the SP mode of execution with the empirical parameter set has the same critical path and the same execution time (see Table 5.3).

One way to reduce the total execution time of loop 11 is to break the critical path. At the end of an iteration, the execute processor can save the newly calculated value of x[k] in a register as well as send it to the memory control unit. The register then can supply an operand for the ADD instruction in the next iteration. Therefore, node 3 is eliminated and the critical path is broken. Row 3 of Table 5.5 shows the simulation result when this technique is applied. This loop can be further optimized by other techniques. Row 4 shows the effect of doubling the loop size, as was discussed in

| and the same of th | parameter<br>set | RAW<br>avoided | code<br>doubled | short<br>ADD | AP<br>#inst | EP<br>#inst | total<br>#inst | exec<br>time | issue<br>rate | speedup |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-----------------|--------------|-------------|-------------|----------------|--------------|---------------|---------|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | empirical        |                |                 |              | 4998        | 2000        | 6998           | 13029        | 38.4%         | 1.00    |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | default          |                |                 |              | 4998        | 2000        | 6998           | 7031         | 71.1%         | 1.85    |